#### CSCI 150 Introduction to Digital and Computer System Design Lecture 3: Combinational Logic Design IV

Jetic Gū

### Overview

- Focus: Logic Functions

- Architecture: Combinatory Logical Circuits

- Textbook v4: Ch3 3.6, 3.7; v5: Ch3 3.6, 3.7

- Core Ideas:

- Encoder 1.

- 2. Multiplexer

## Review Systematic Design Procedures

- 1. Specification: Write a specification for the circuit

- 2. **Formulation**: Derive relationship between inputs and outputs of the system e.g. using truth table or Boolean expressions

- 3. **Optimisation**: Apply optimisation, minimise the number of logic gates and literals required

- 4. **Technology Mapping**: Transform design to new diagram using available implementation technology

- 5. **Verification**: Verify the correctness of the final design in meeting the specifications

- Value-Fixing, Transferring, Inverting, Enabler

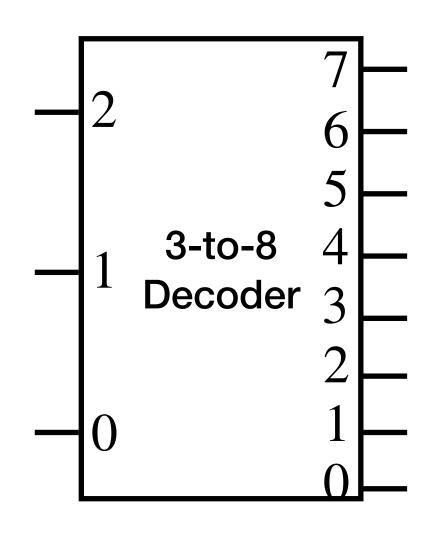

- Decoder

- Input:  $A_0 A_1 \dots A_{n-1}$

- Output:  $D_0 D_1 \dots D_{2^n-1}$ ,  $D_i = m_i$

## **Functional Components**

**P1** Encoder

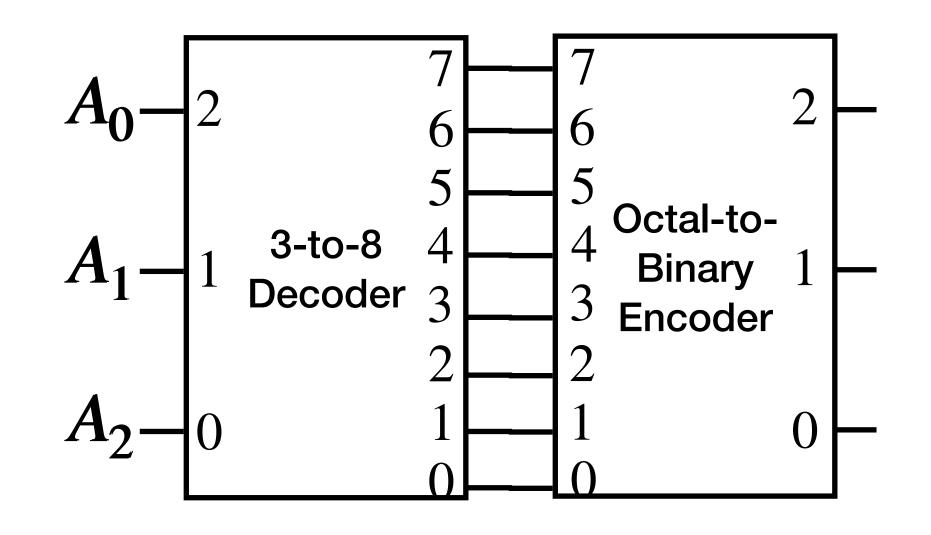

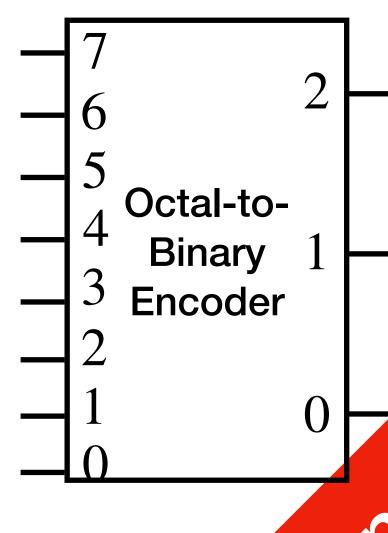

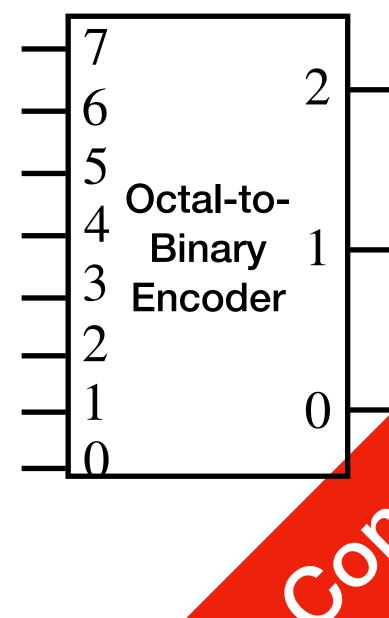

### Encoder

Wait, didn't we just covered this? Oh, that's decoder

- Inverse operation of a decoder

- $2^n$  inputs, only one is giving positive input<sup>1</sup>

- *n* outputs

1. In reality, could be less

- Inverse operation of a decoder

- $2^n$  inputs, only one is giving positive input<sup>1</sup>

- *n* outputs

1. In reality, could be less

| D <sub>0</sub> | <b>A</b> 2 | <b>A</b> <sub>1</sub> | A <sub>0</sub> |

|----------------|------------|-----------------------|----------------|

| 1              | 0          | 0                     | 0              |

|                | 0          | 0                     | 1              |

|                | 0          | 1                     | 0              |

|                | 0          | 1                     | 1              |

|                | 1          | 0                     | 0              |

|                | 1          | 0                     | 1              |

|                | 1          | 1                     | 0              |

|                | 1          | 1                     | 1              |

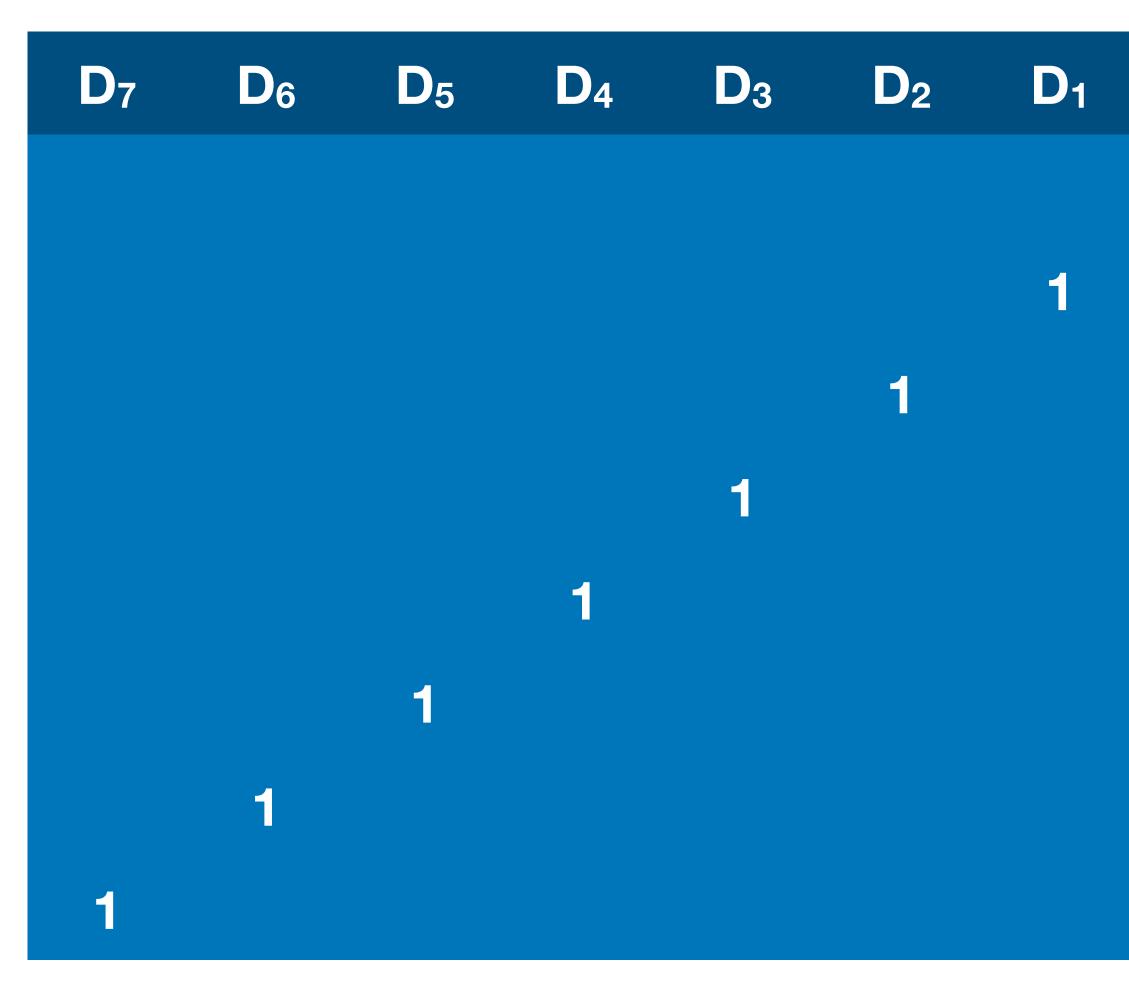

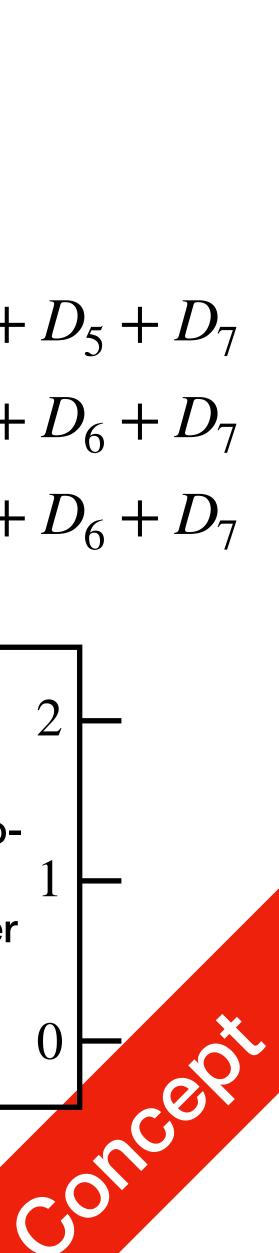

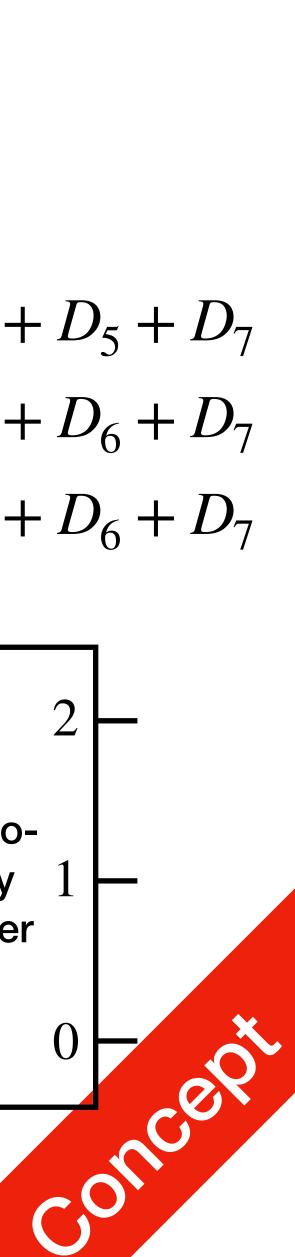

$A_0 = D_1 + D_3 + D_5 + D_7$  $A_1 = D_2 + D_3 + D_6 + D_7$  $A_2 = D_4 + D_5 + D_6 + D_7$

- What happens if the inputs are all 0s?

- What happens if the inputs include multiple 1s?

$A_0 = D_1 + D_3 + D_5 + D_7$  $A_1 = D_2 + D_3 + D_6 + D_7$  $A_2 = D_4 + D_5 + D_6 + D_7$

- Additional Validity Output V

- Indicating whether the input is valid (contains 1)

- Priority

- Ignores  $D_{<i}$  if  $D_i = 1$

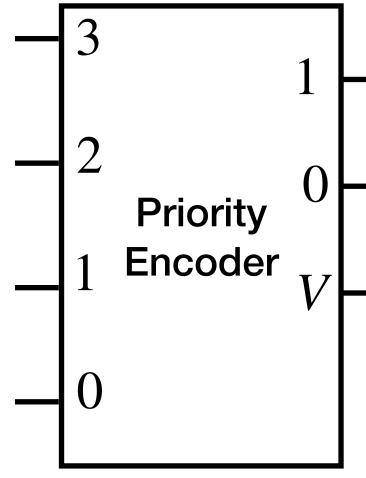

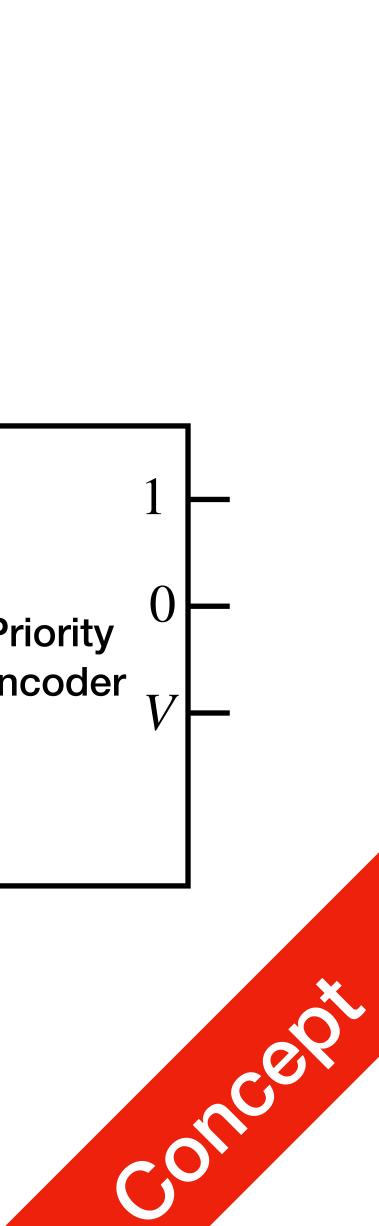

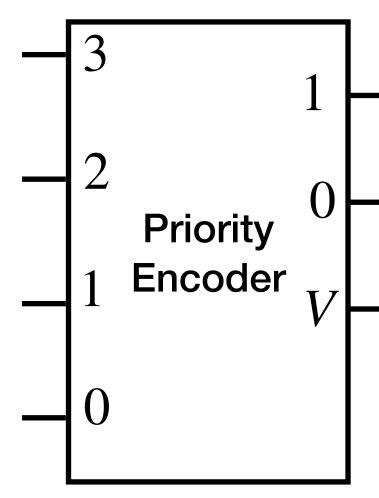

### **Priority Encoder**

**P1** Encoder

| D <sub>3</sub> | D <sub>2</sub> | D <sub>1</sub> | Do | A <sub>1</sub> | A <sub>0</sub> | V |

|----------------|----------------|----------------|----|----------------|----------------|---|

| 0              | 0              | 0              | 0  | Х              | Х              | 0 |

| 0              | 0              | 0              | 1  | 0              | 0              | 1 |

| 0              | 0              | 1              |    | 0              | 1              | 1 |

| 0              | 1              |                |    | 1              | 0              | 1 |

| 1              | X              | X              | X  | 1              | 1              | 1 |

## **Priority Encoder**

**P1** Encoder

| D <sub>3</sub> | D <sub>2</sub> | D <sub>1</sub> | Do | A <sub>1</sub> | A <sub>0</sub> | V | $V = D_3 + D_2 + D_1 + D_0$                                                               |

|----------------|----------------|----------------|----|----------------|----------------|---|-------------------------------------------------------------------------------------------|

| 0              | 0              | 0              | 0  | 0              | 0              | 0 | $A_1 = D_3 + \overline{D_3}D_2 = D_2 + D_3$ $A_0 = \overline{D_3}\overline{D_2}D_1 + D_3$ |

| 0              | 0              | 0              | 1  | 0              | 0              | 1 | $= \overline{D_2}D_1 + D_3$                                                               |

| 0              | 0              | 1              | X  | 0              | 1              | 1 |                                                                                           |

| 0              | 1              | X              | X  | 1              | 0              | 1 | $\begin{bmatrix} 2 \\ Priority \\ 1 \\ Encoder \\ V \end{bmatrix}$                        |

| 1              | X              | X              | X  | 1              | 1              | 1 |                                                                                           |

|                |                |                |    |                |                |   |                                                                                           |

## **Priority Encoder**

P2 Multiplexer

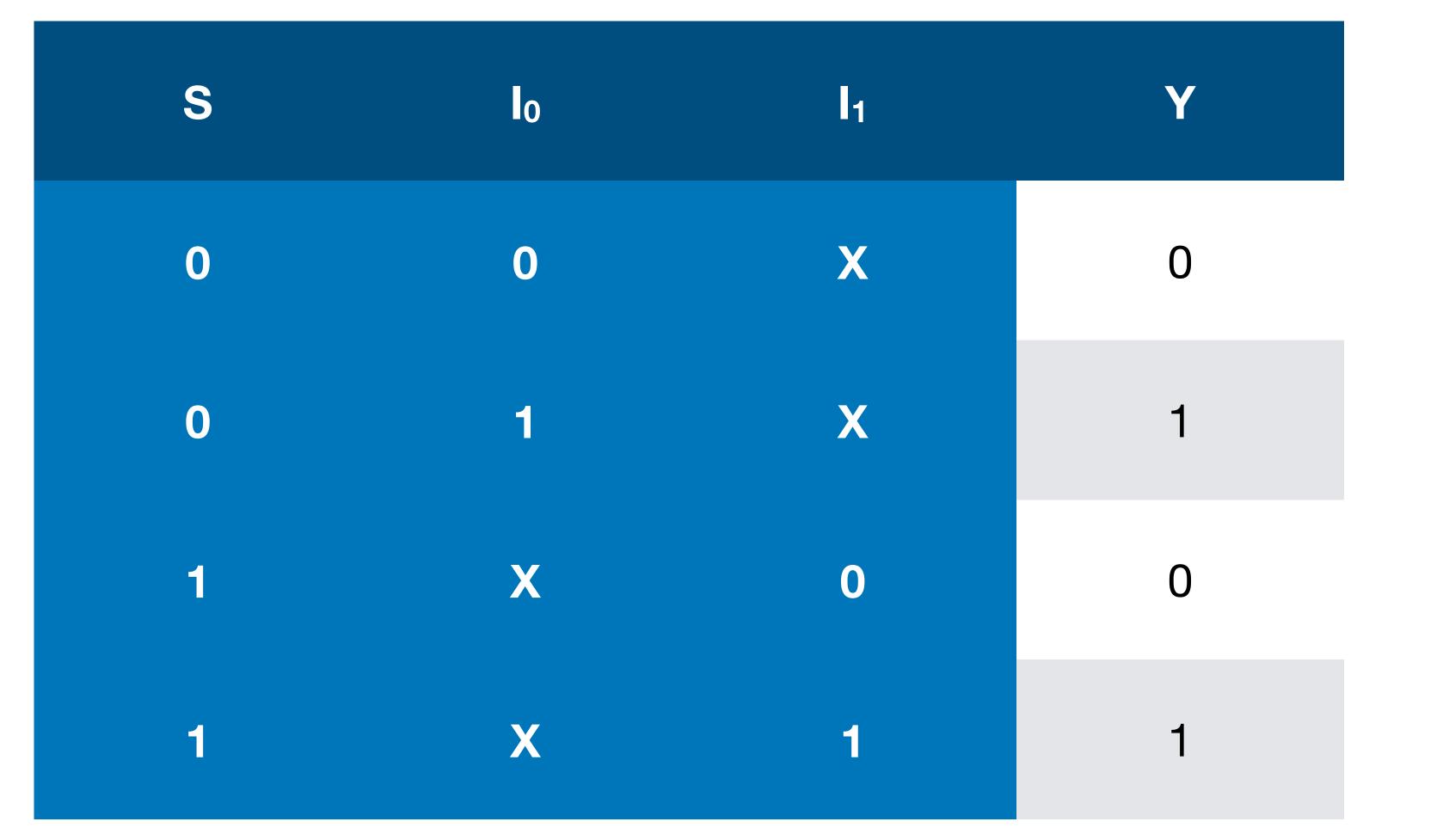

#### **Multiplexer** Switch Modes

**P2** Multiplexer

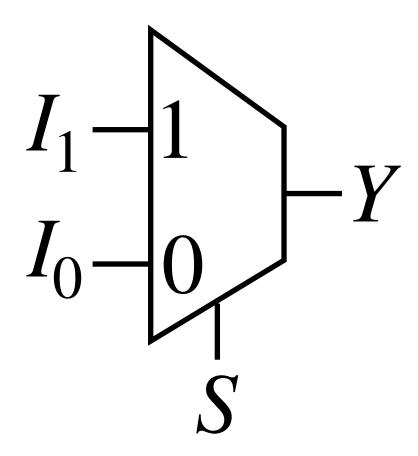

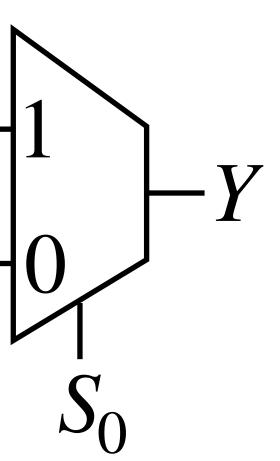

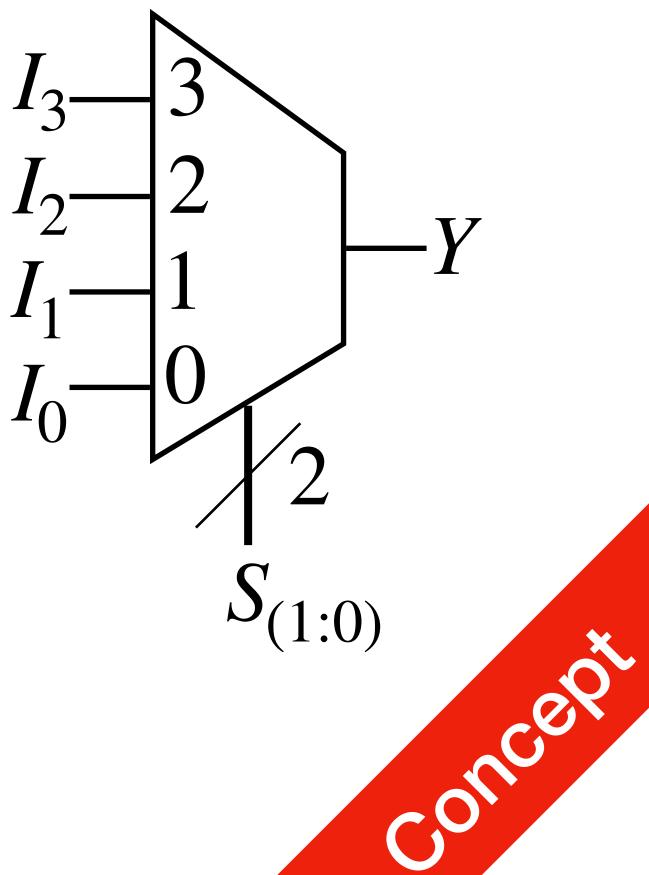

## Multiplexer

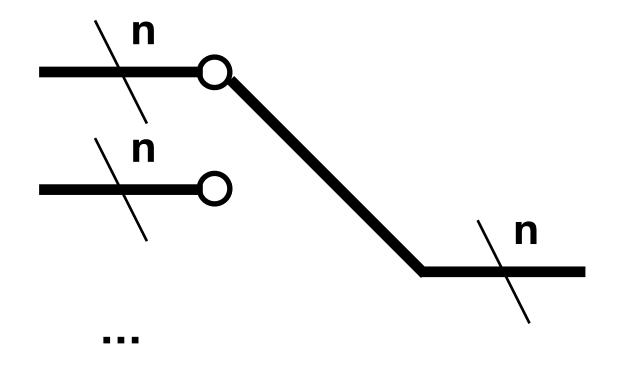

- Multiple *n*-variable input vectors

- Single *n*-variable output vector

- Switches: which input vectors to output

- 2 single-bit inputs

- 1 single-bit output

- 1-bit switch

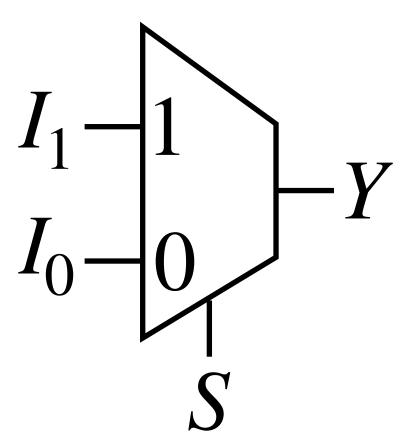

# Multiplexer Single-Bit 2-to-1 Multiplexer

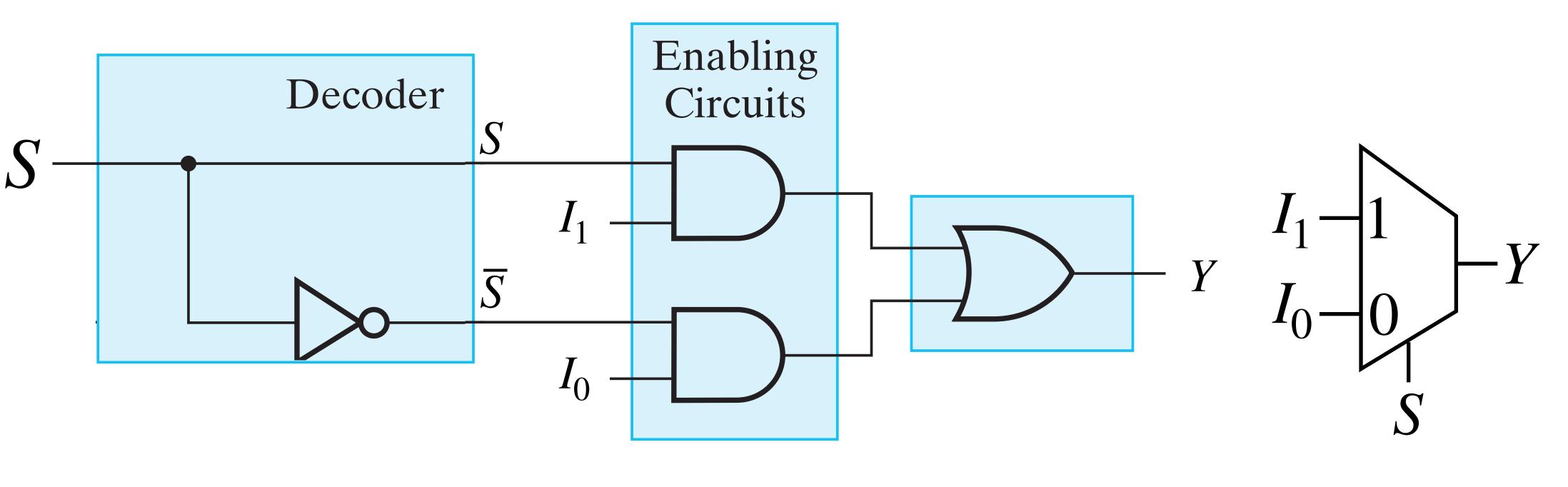

#### Single-Bit 2-to-1 Multiplexer

P2 Multiplexer

Technology

- 1 x 1-to-2 Decoder

- 2 x 1-bit Enabler

- 1 x 2-input OR Gate

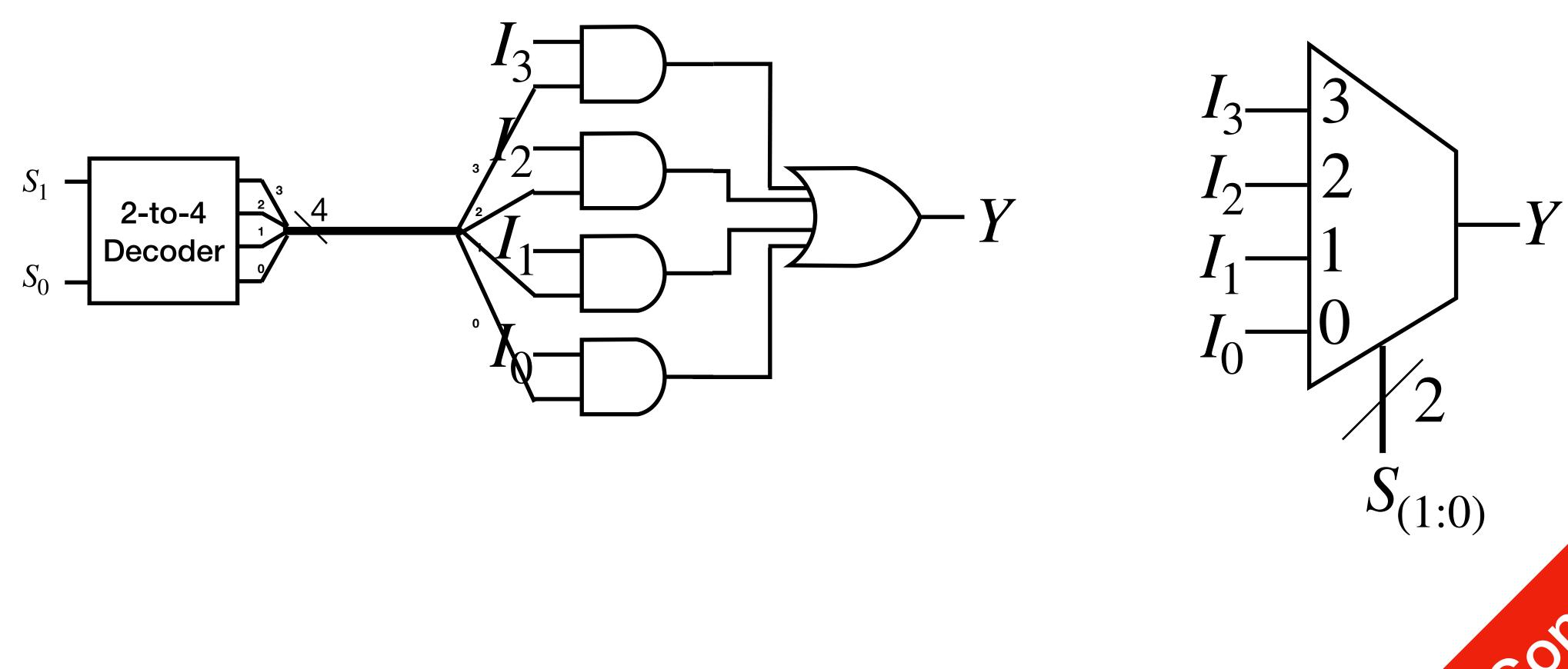

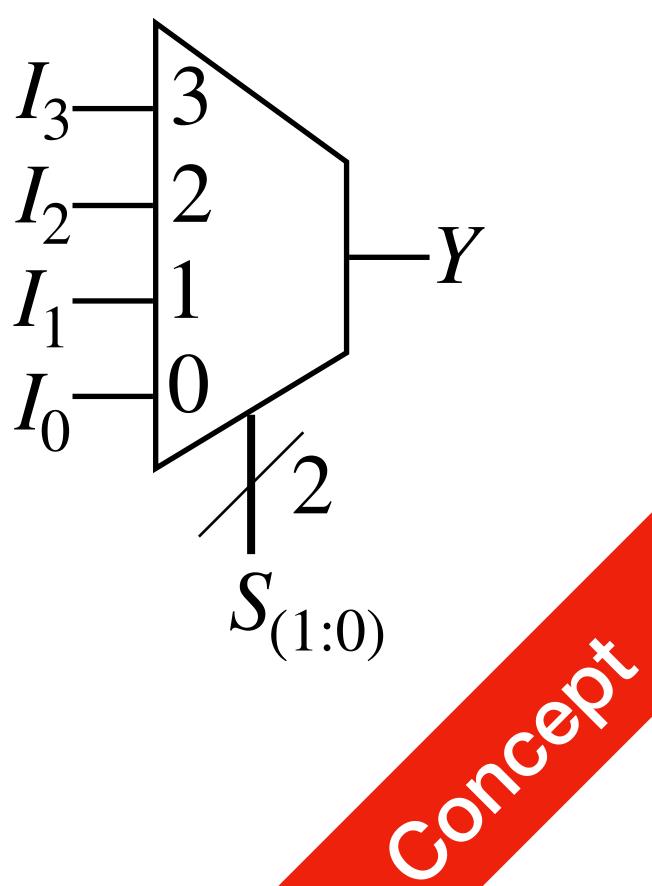

#### Single-Bit 4-to-1 Multiplexer

P2 Multiplexer

Technology

- 1 x 2-to-4 Decoder

- 4 x 1-bit Enabler

- 1 x 4-input OR Gate

#### Single-Bit 4-to-1 Multiplexer

**P2** Multiplexer

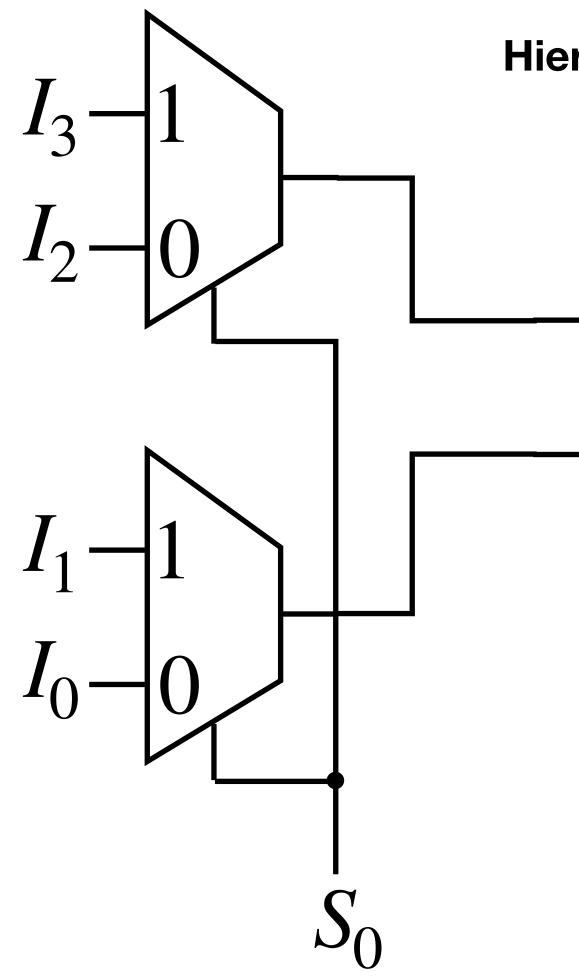

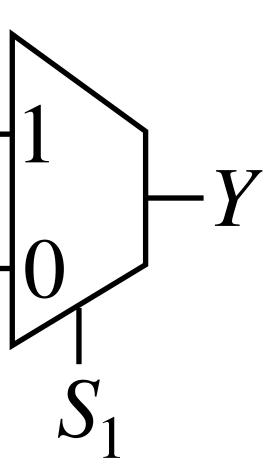

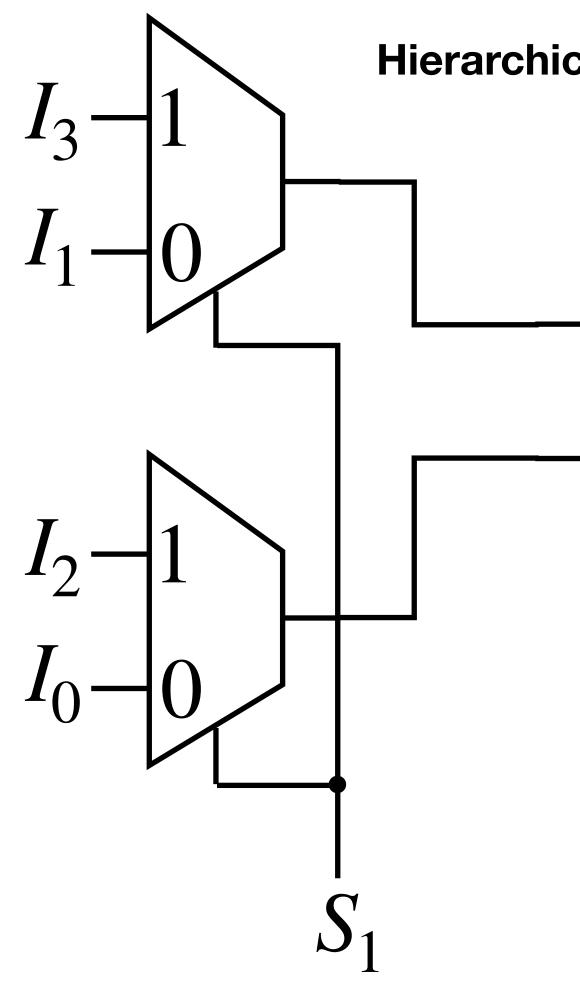

**Hierarchical using MUX**

Technology 3 x 1bit 2-to-1 MUX

#### Single-Bit 4-to-1 Multiplexer

**P2** Multiplexer

**Hierarchical using MUX (Alternative)**

#### Circuit Drawing Time! For Lab 2

## Logic Works Last Circuit Drawing Practice

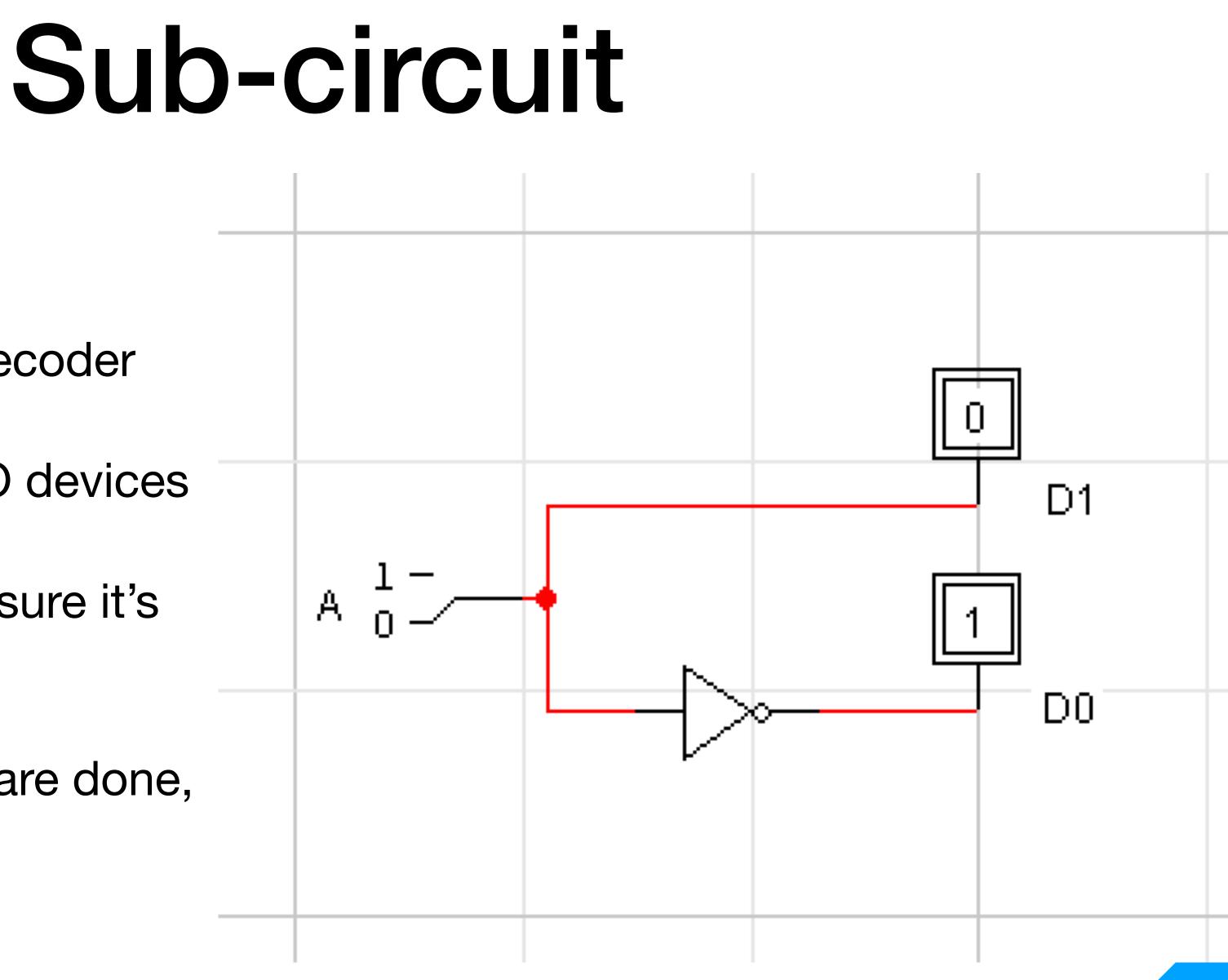

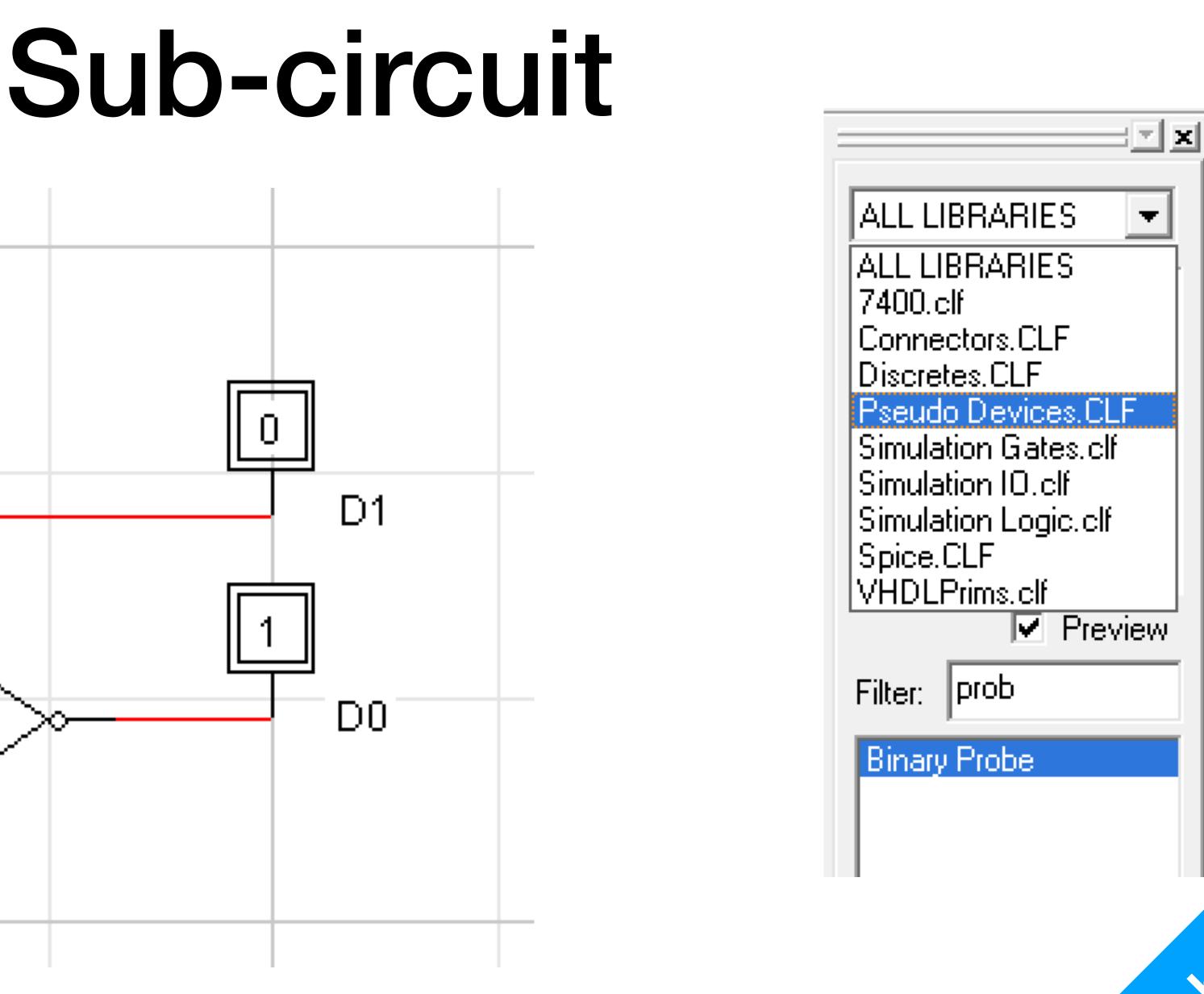

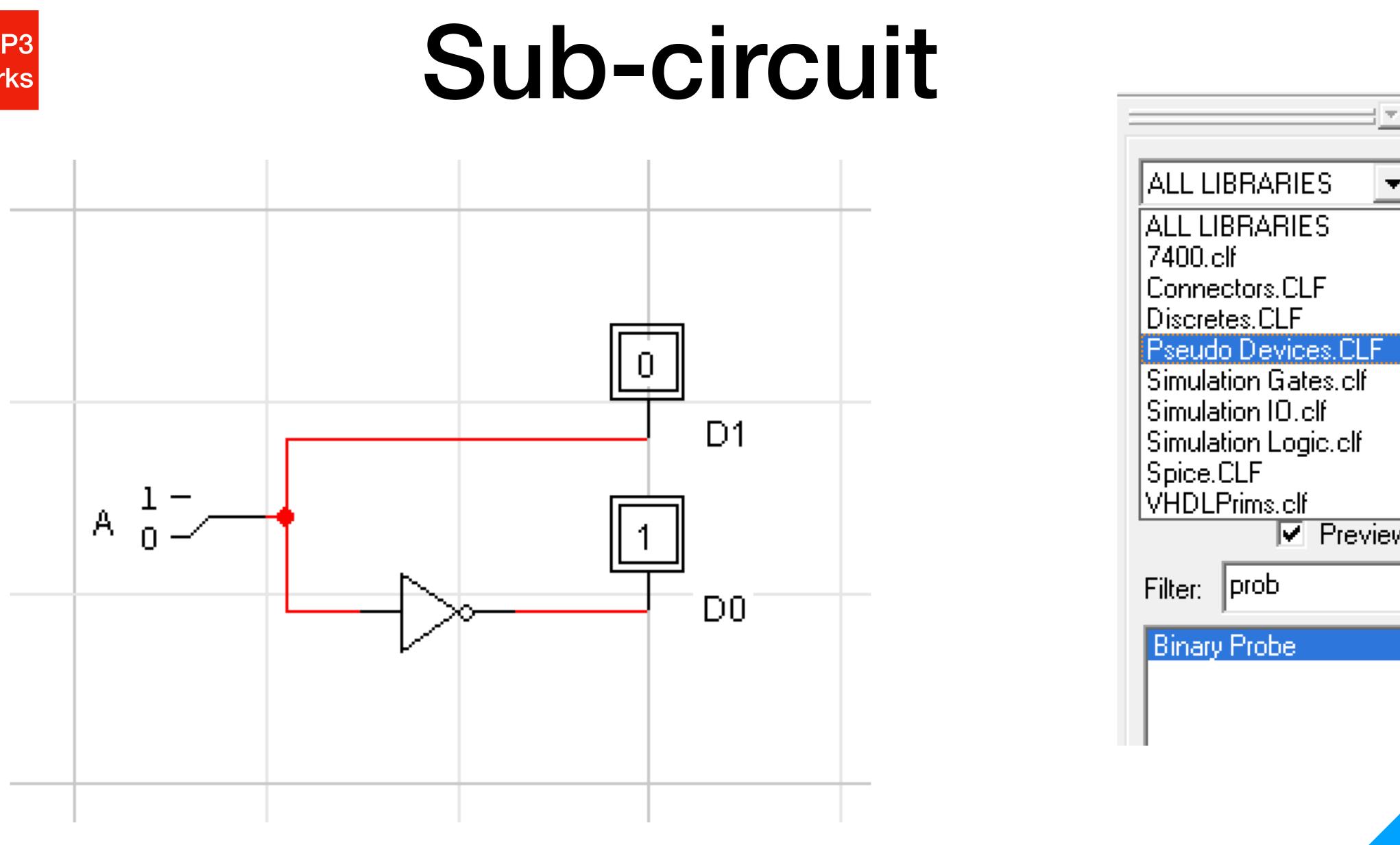

#### Sub-circuit

- 2. Implementing 2-to-4 Decoder using drawing tools

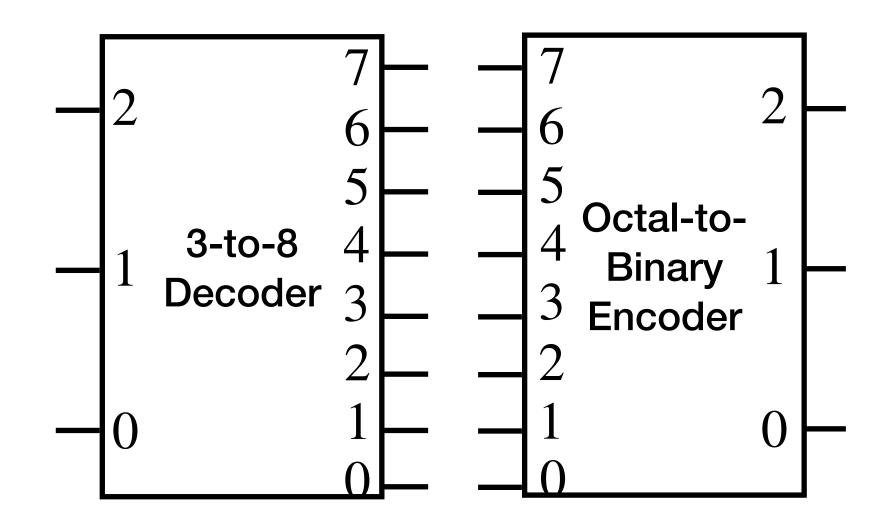

- 3. Implementing 3-to-8 Decoder using 2-to-4 Decoders

- 4. Implementing 4-to-16 Decoder using 2-to-4 Decoders or 3-to-8 Decoders

- 5. Implementing Octal-to-3 Priority Encoder

- 6. Implementing 1bit 4-to-1 Multiplexer using 2-to-4 Decoder

#### 7. Implementing 4bit 4-to-1 Multiplexer using 1bit 4-to-1 Multiplexers

#### 1. You will be reusing these designs in later lectures and assignments

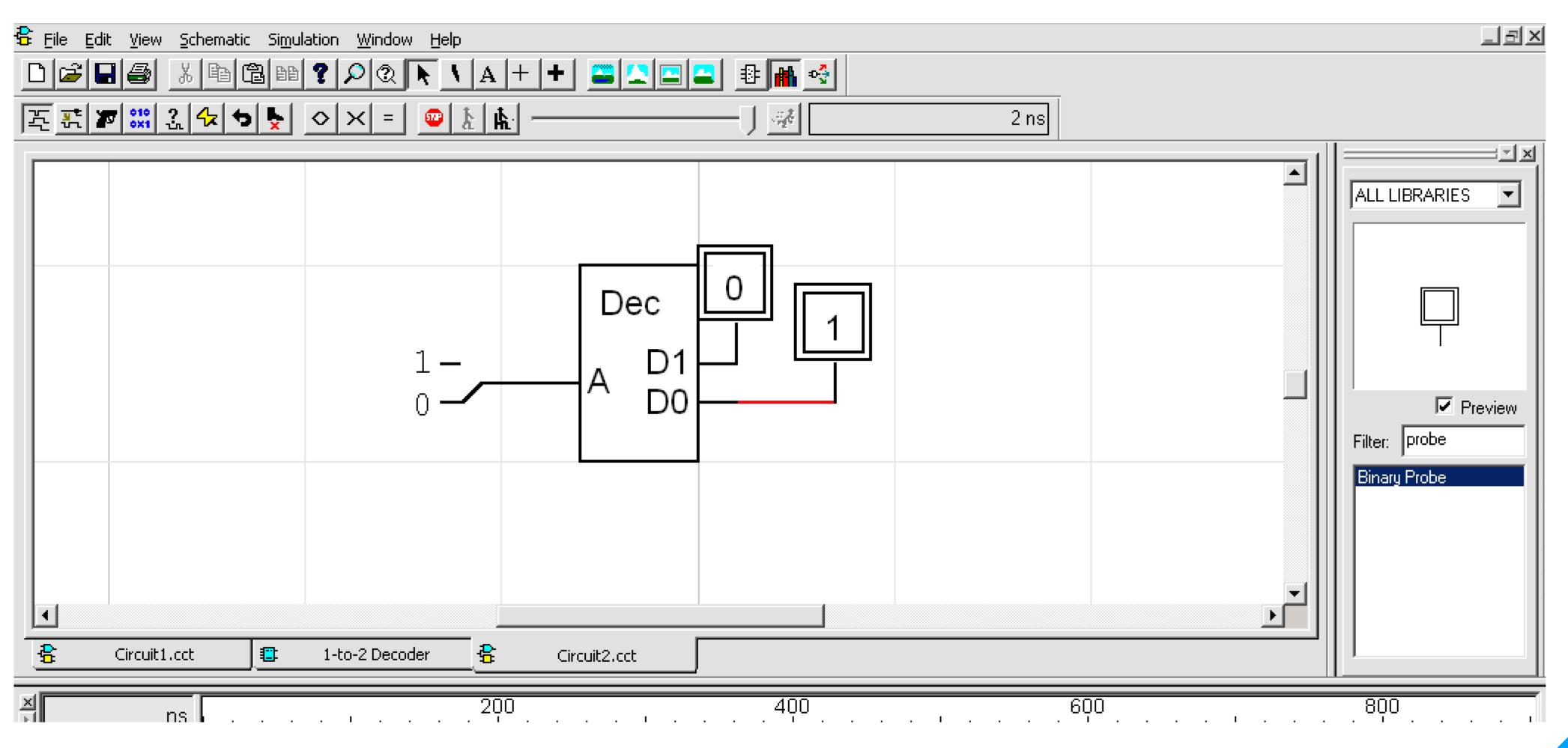

- Implement a 1-to-2 Decoder 1.

- 2. Correctly label ALL I/O devices

- 3. Test the circuit, make sure it's actually working

- 4. Only when the above are done, should you proceed

Before we get started, make sure you have implemented a 1-to-2 Decoder using switches and probes correctly

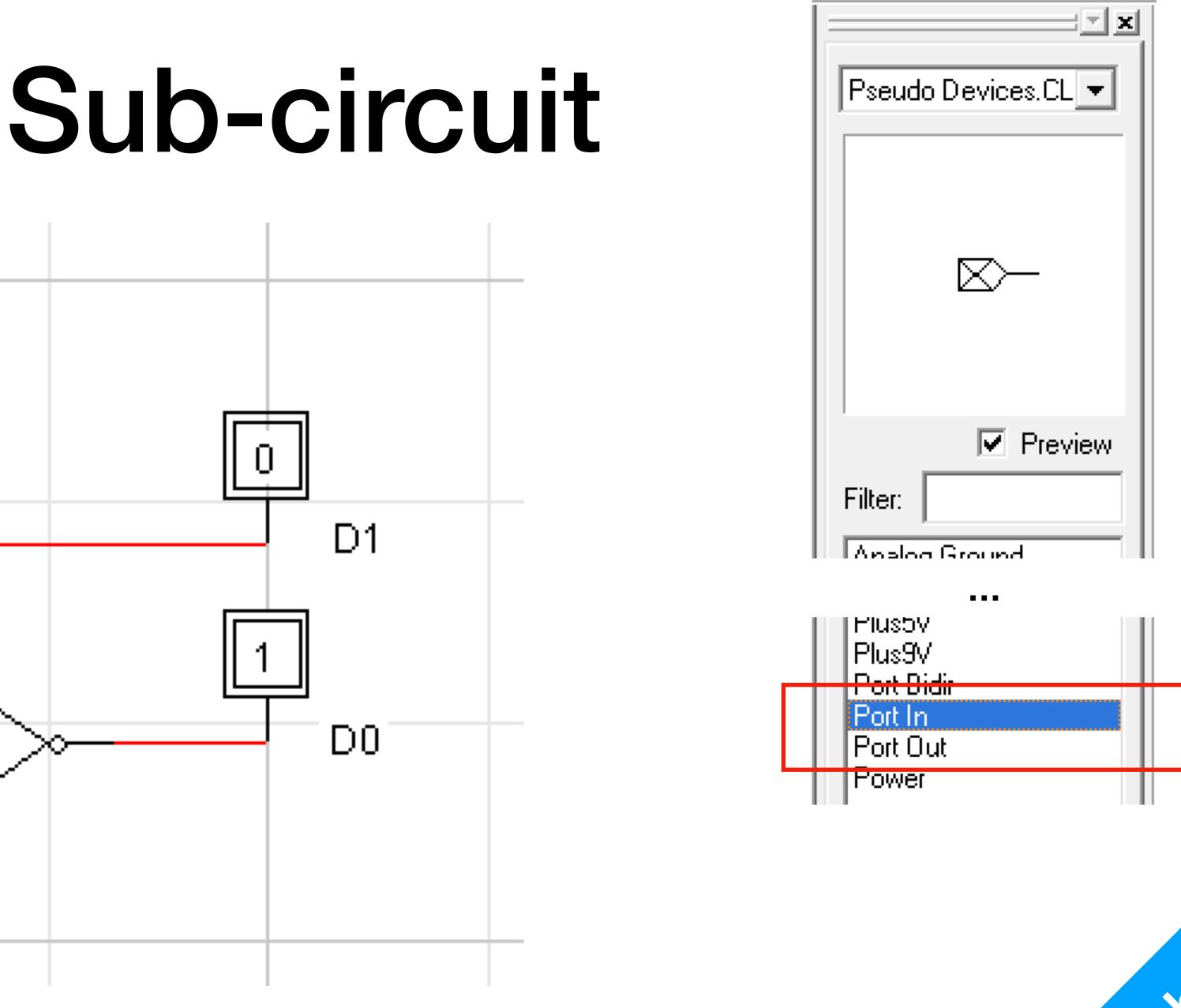

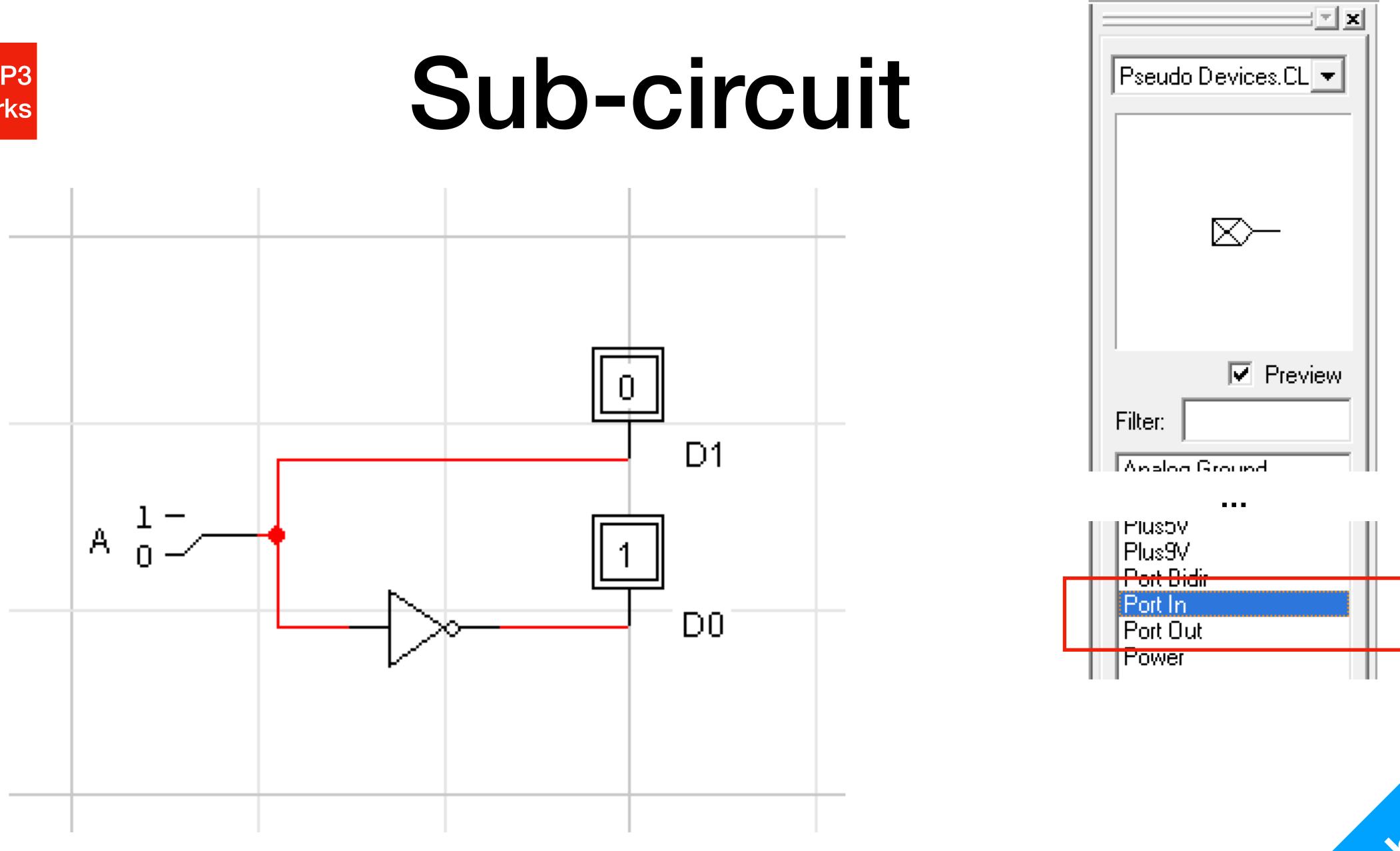

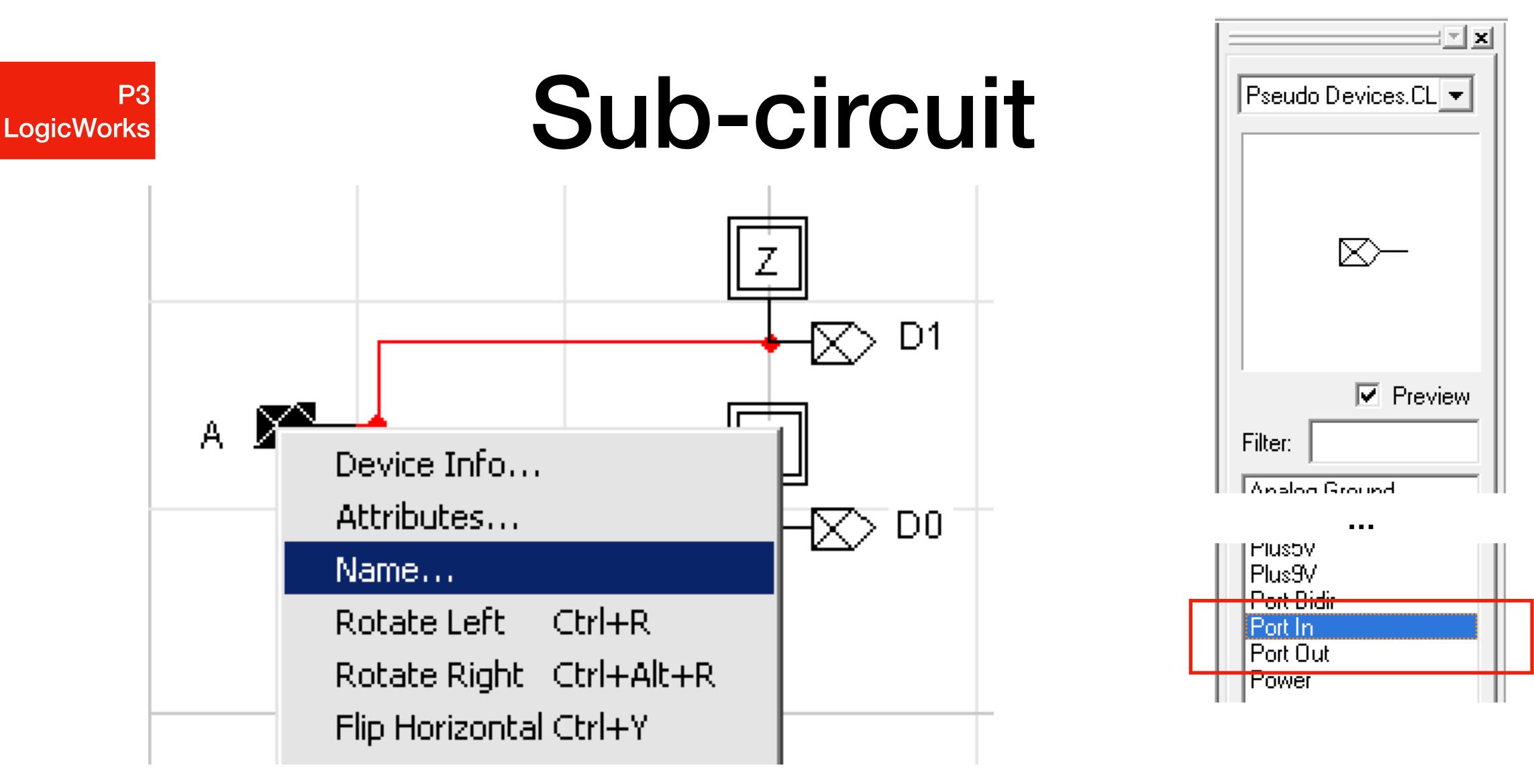

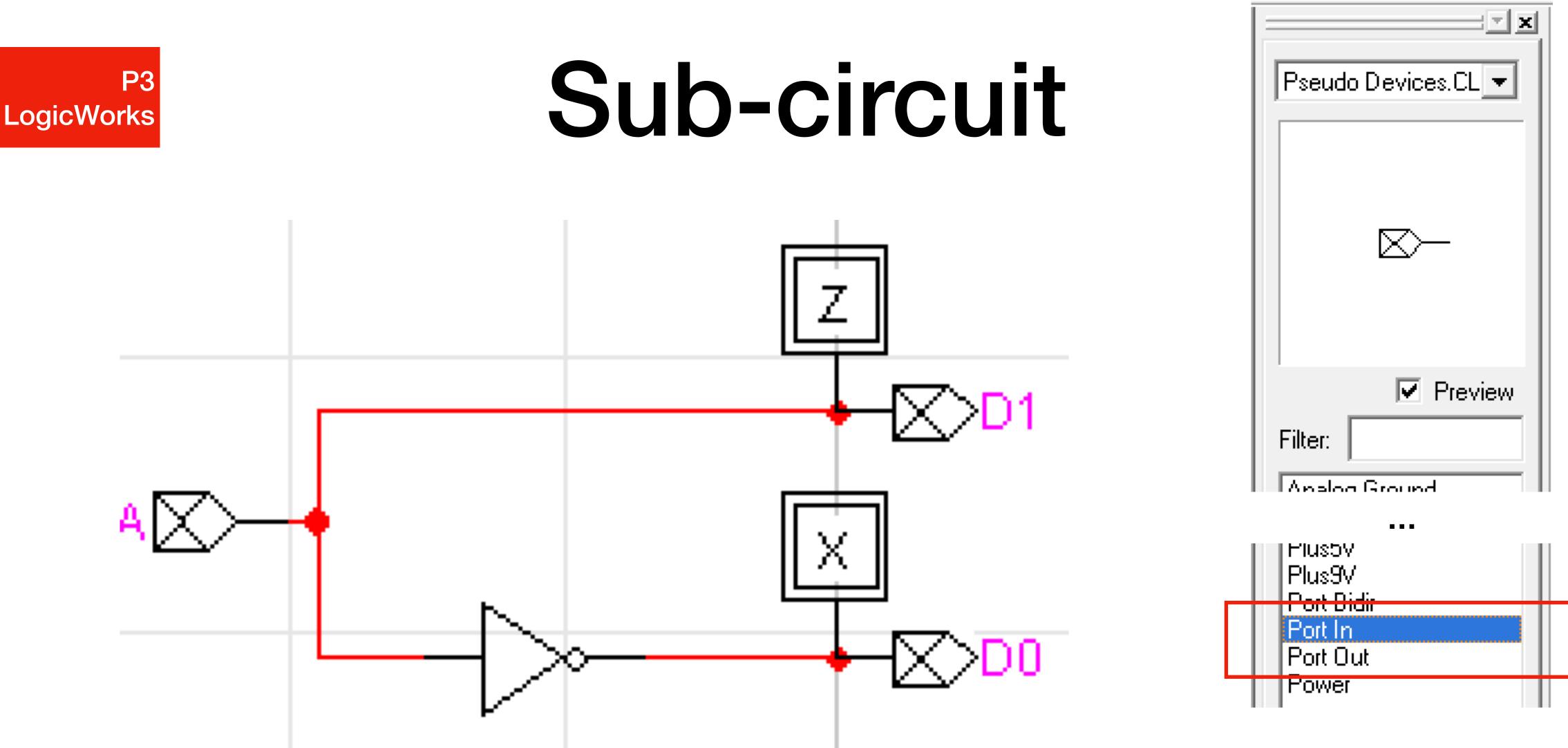

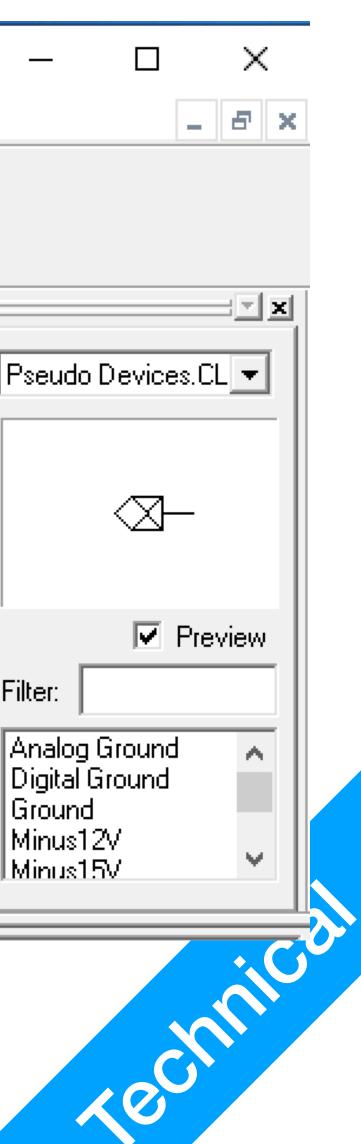

1. Select the Pseudo Devices library

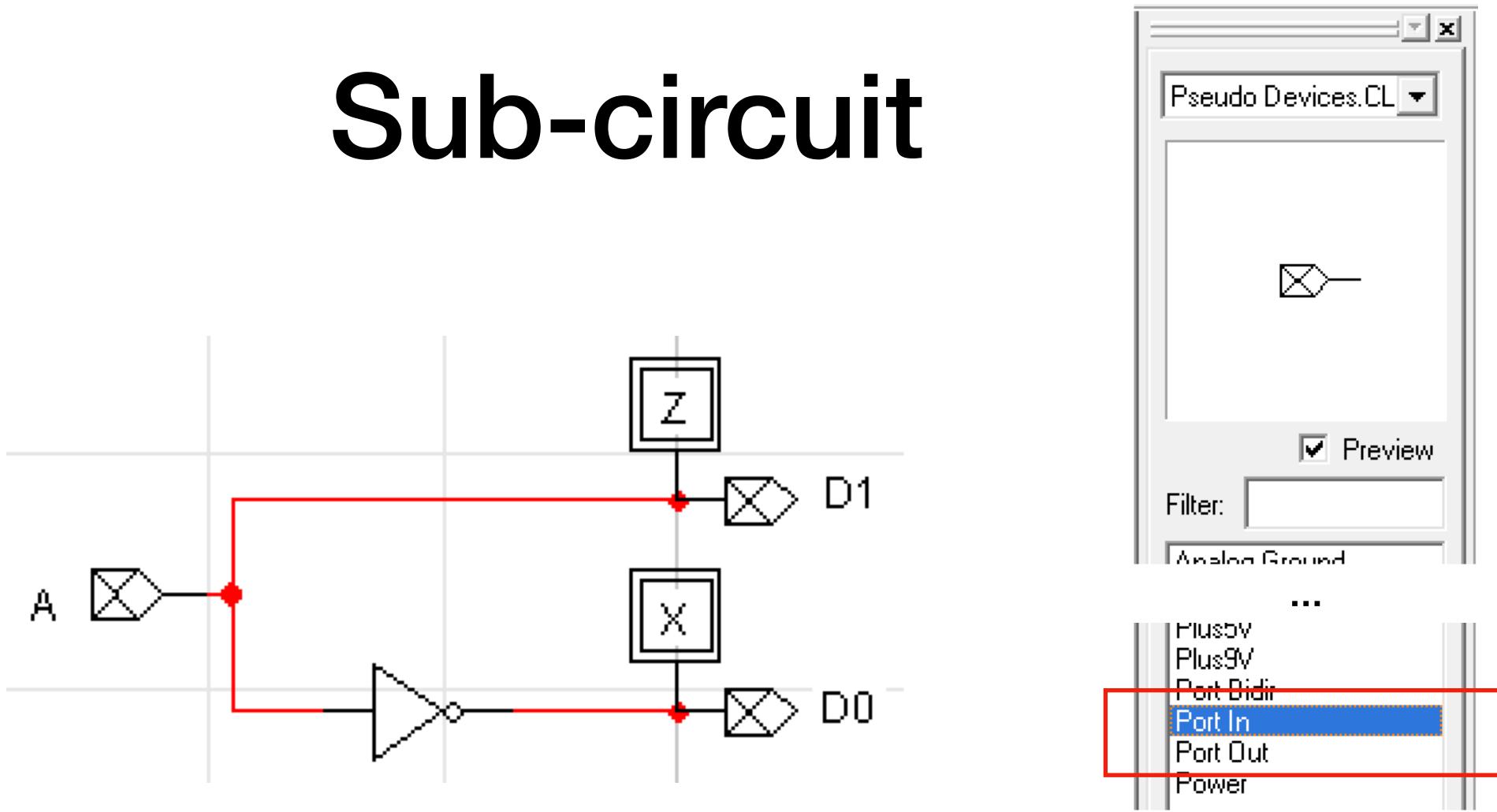

2. Replace the switch with Port In, replace the probs with Port Out, give them names

2. Right click on each port to give them names. Textbox will not be good enough

Once correctly done, the names will automatically be in purple

2. Right click on each port to give them names. Textbox will not be good enough

### Sub-circuit

|   | Х      |

|---|--------|

|   | OK     |

| ^ | Cancel |

| ¥ |        |

|   |        |

|   |        |

## Sub-circuit

| ≳ LogicWorks 5 - [Part1] |                           |              |                                         | — 🗆                                                       |

|--------------------------|---------------------------|--------------|-----------------------------------------|-----------------------------------------------------------|

| File Edit View Objects   | Options Pins Tools Window | Help         |                                         | -                                                         |

| 독 문 🖉 🔐 🏦 🕇 🖢 💆          | Auto Create Symbol        | Ctrl+J       |                                         | าร                                                        |

| X 🖻 🖀 🖬 i 🔤 🔼 [          | Subcircuit and Part Type  | Ctrl+Q       |                                         |                                                           |

|                          | Open Subcircuit           |              |                                         |                                                           |

|                          | Add Pins                  | Ctrl+E       |                                         |                                                           |

|                          | Grids                     |              |                                         | Pseudo Devices.                                           |

|                          | Part Attributes           | Ctrl+H       |                                         |                                                           |

|                          | Pin Attributes            | Ctrl+Shift+H |                                         |                                                           |

|                          |                           |              |                                         |                                                           |

|                          |                           |              |                                         |                                                           |

|                          |                           |              |                                         | Pr                                                        |

| Pin Number               |                           |              |                                         | Filter:                                                   |

| Pin Type                 |                           |              |                                         | <ul> <li>Analog Ground</li> <li>Digital Ground</li> </ul> |

| Pin Function             | <                         |              | > · · · · · · · · · · · · · · · · · · · | Ground                                                    |

|                          | Circuit2.cct              | Part1        |                                         | Minus12V<br>Minus15V                                      |

|                          |                           |              |                                         |                                                           |

|                          |                           |              |                                         |                                                           |

4. With the Circuit.cct open and Part1 open, go to Options - Subcircuit and Part Type

### Sub-circuit

#### Pa

| art Type                                                               | $\times$ |

|------------------------------------------------------------------------|----------|

| Primitive Type                                                         |          |

| Create a subcircuit symbol, but don't store a circuit with it yet.     |          |

| Create a subcircuit symbol and select an open circuit to attach to it. |          |

| <sup>○ Imp</sup> Select Internal Circuit × <sup>uit.</sup>             |          |

| O Set                                                                  |          |

| O Set Circuit2.cct                                                     |          |

| Oti                                                                    |          |

| Subcircu                                                               |          |

|                                                                        |          |

|                                                                        |          |

| Brow Cancel                                                            |          |

|                                                                        |          |

| - Messages Den                                                         |          |

| Don                                                                    | e        |

| Cano                                                                   | el       |

5. Select Create a subcircuit symbol and select an open circuit to attach to it

## Sub-circuit

#### Part Type

| Primitive Type                |

|-------------------------------|

| C Create a subcircuit symbol, |

| Create a subcircuit symbol    |

| C Imp Select Internal Circui  |

| O Set                         |

| O Set Circuit2.cct            |

| Ott                           |

|                               |

| Subcircu                      |

|                               |

|                               |

|                               |

| Brow                          |

|                               |

|                               |

| Messages                      |

|                               |

|                               |

|                               |

6. Select Circuit.cct

$\times$ but don't store a circuit with it yet. and select an open circuit to attach to it. uit. Х OK. Cancel Done Cancel

**Use these pins only!**

Add a text description

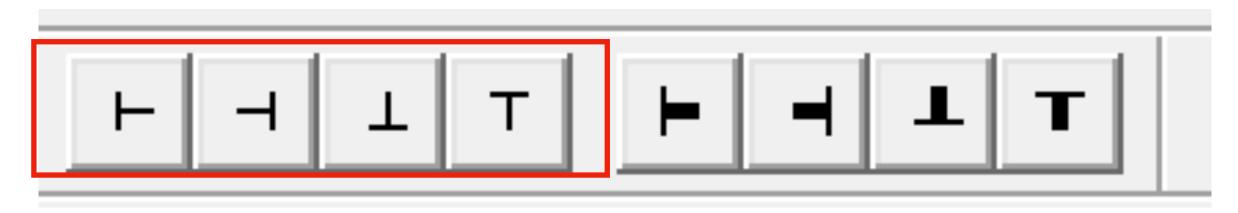

7. Draw a rectangle and add the THIN pins

#### Sub-circuit

## Sub-circuit

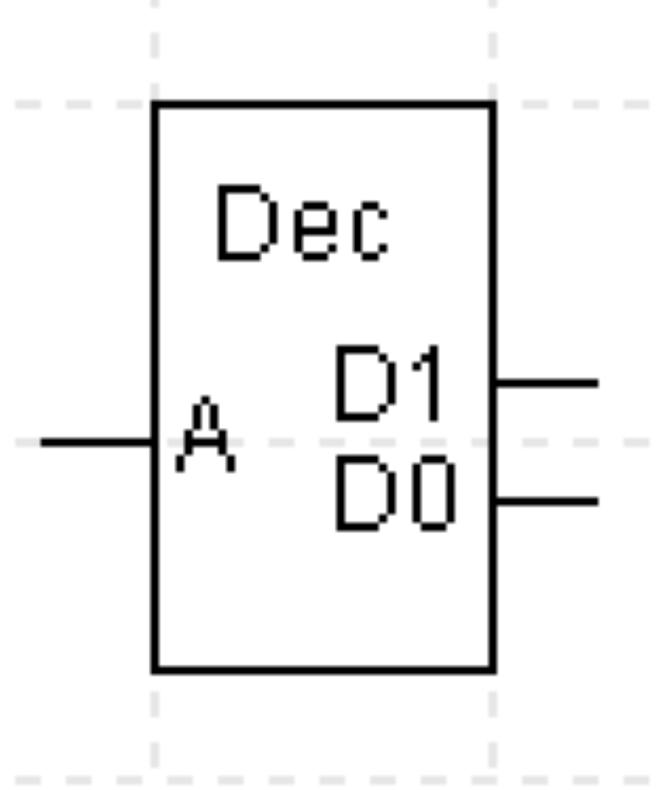

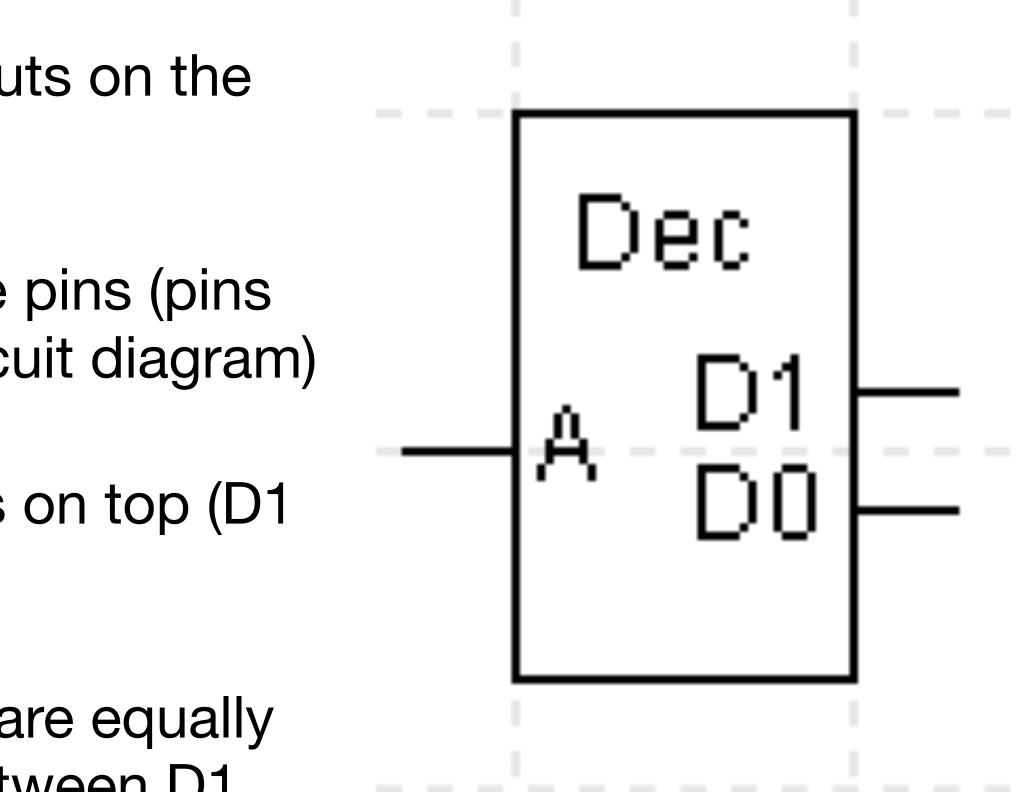

- 1. Ensure inputs are on the left, outputs on the right

- 2. Ensure that there are no excessive pins (pins that do not exist in the original circuit diagram)

- 3. Ensure the more significant digit is on top (D1 above D0)

- 4. Ensure the pins on the same side are equally spaced with distance of 2 (e.g. between D1 and D0)

## Sub-circuit

| Save Part As                                                                                                                                                         | Save Part As                                                                                                                                                                        |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Part name: 1-to-2 Decoder                                                                                                                                            | Part name: 1-to-2 Decoder                                                                                                                                                           |

| Destination Library: Library is read-c                                                                                                                               | Destination Library:                                                                                                                                                                |

| 7400.clf<br>Connectors.CLF<br>Discretes.CLF<br>Pseudo Devices.CLF<br>Simulation Gates.clf<br>Simulation IO.clf<br>Simulation Logic.clf<br>Spice.CLF<br>VHDLPrims.clf | 7400.clf<br>Connectors.CLF<br>CSCI150.clf<br>Discretes.CLF<br>Pseudo Devices.CLF<br>Simulation Gates.clf<br>Simulation IO.clf<br>Simulation Logic.clf<br>Spice.CLF<br>VHDLPrims.clf |

| New Lib Open Lib Save Cancel                                                                                                                                         | New Lib Open Lib Save Cancel                                                                                                                                                        |

|                                                                                                                                                                      |                                                                                                                                                                                     |

8. Save the part in a new library as 1-to-2 Decoder, call your library CSCI150

### Sub-circuit

#### 9. Create a new circuit, test your new design before calling it a day

## LogicWorks Circuit Drawing Practice

- 1. Sub-circuit

- 2. Implementing 2-to-4 Decoder using drawing tools

- 3. Implementing 3-to-8 Decoder using 2-to-4 Decoders

- 4. Implementing 4-to-16 Decoder using 2-to-4 Decoders or 3-to-8 Decoders

- 5. Implementing Octal-to-3 Priority Encoder

- 6. Implementing 1 bit 4-to-1 Multiplexer using 2-to-4 Decoder

- 7. Implementing 4bit 4-to-1 Multiplexer using 1bit 4-to-1 Multiplexers 1

- 1. You will be reusing these designs in later lectures and assignments