## CSCI 150 Introduction to Digital and Computer System Design Lecture 5: Registers I

Jetic Gū 2020 Fall Semester (S3)

## Overview

- Focus: Fundamentals of Complex Digital Circuit Design

- Architecture: von Neumann

- Textbook v4: Ch7 7.1 7.2; v5: Ch6 6.1 6.2

- Core Ideas:

- What are Registers 1.

- 2. Register Transferring Operations and Circuit

- Synchronous Sequential Circuit Signals arrive at discrete instants of time, outputs at next time step

- Has Clock

- Asynchronous Sequential Circuit Signals arrive at any instant of time, outputs when ready

- May not have Clock

## What are Registers? Definitions; Register Loading; Parallel Loading

### 1. Von Neumann Architecture

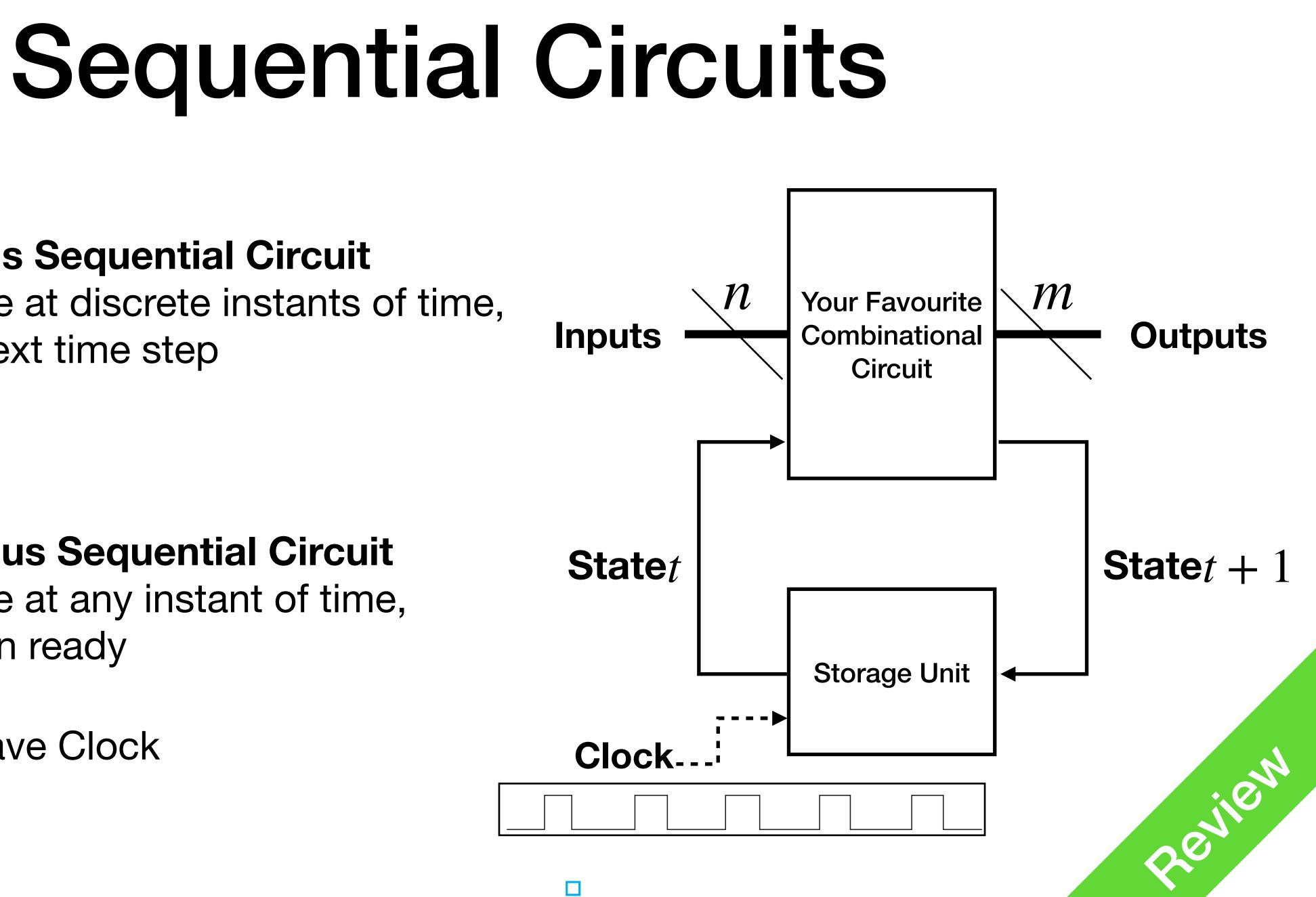

## Computer

### **P1** Registers

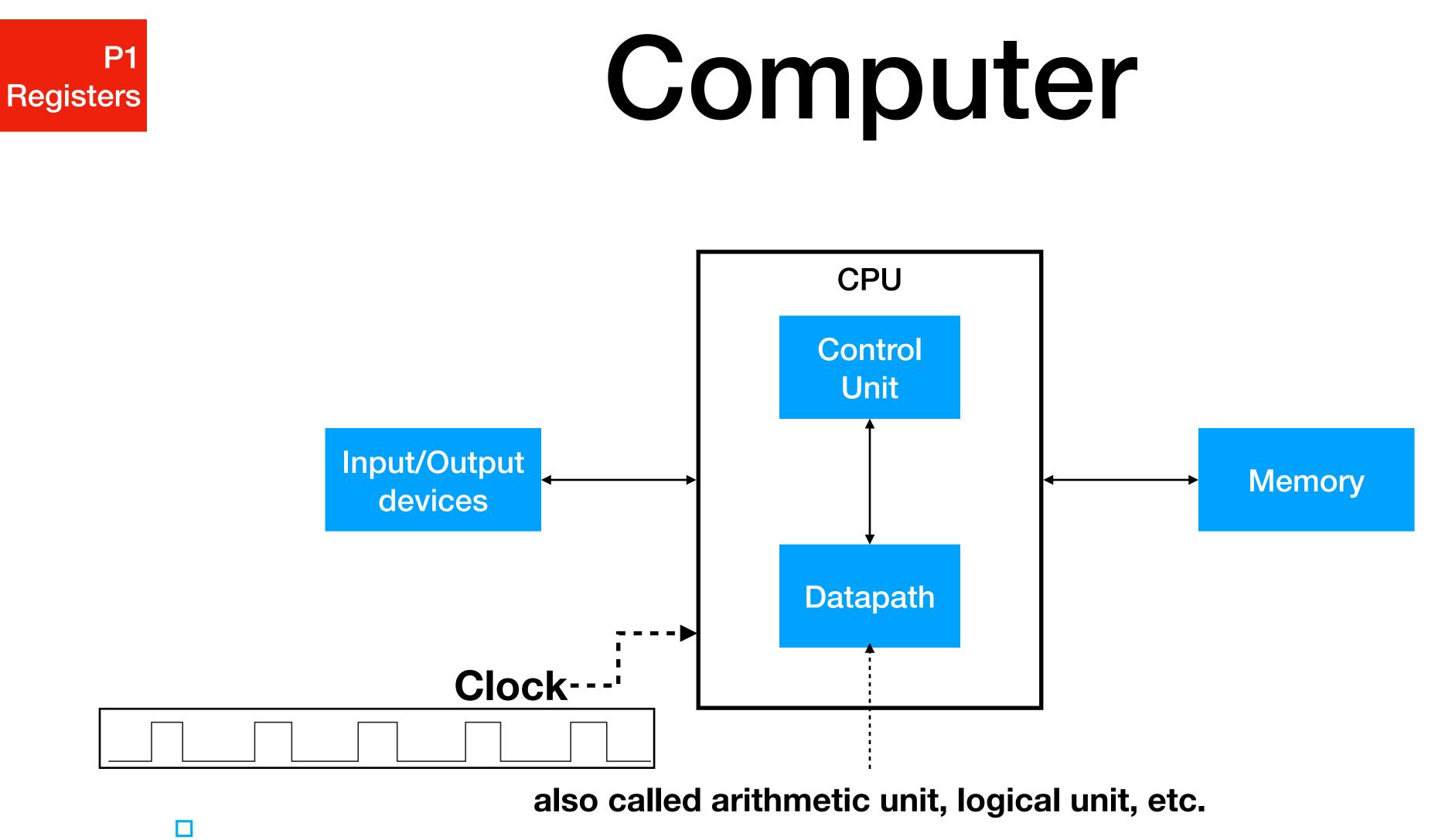

### A very rough example

### **P1** Registers

## von Neumann CPU

- Control Unit

- datapath

- Datapath

- Processing logic units: Adder, Subtractor, Shifter, Counter, etc.

- digital system

Determine sequence of data-processing operations performed by the

Registers: Storage of temporary information, basic components of the

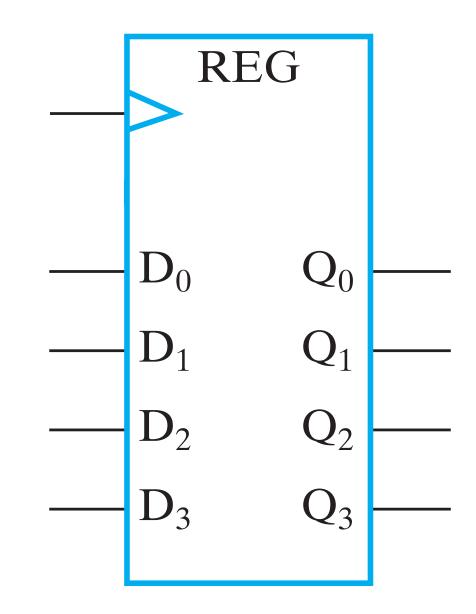

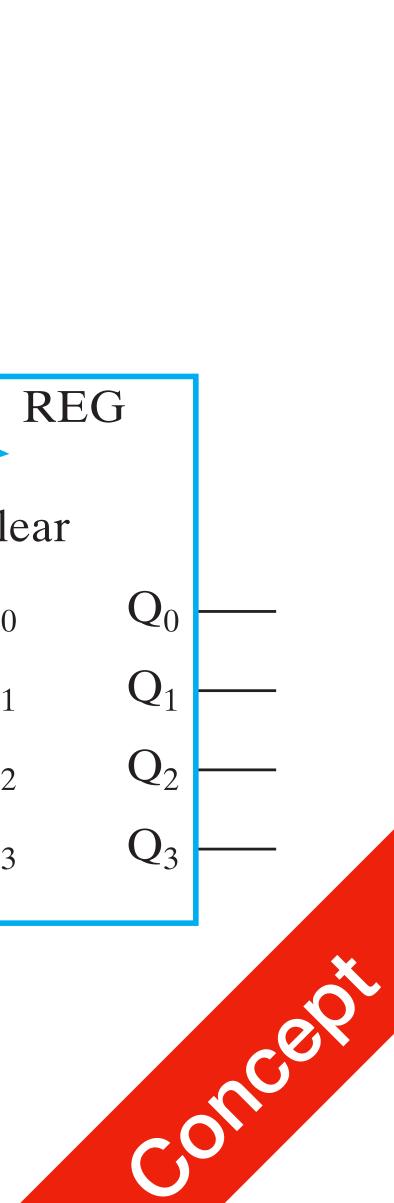

## Register

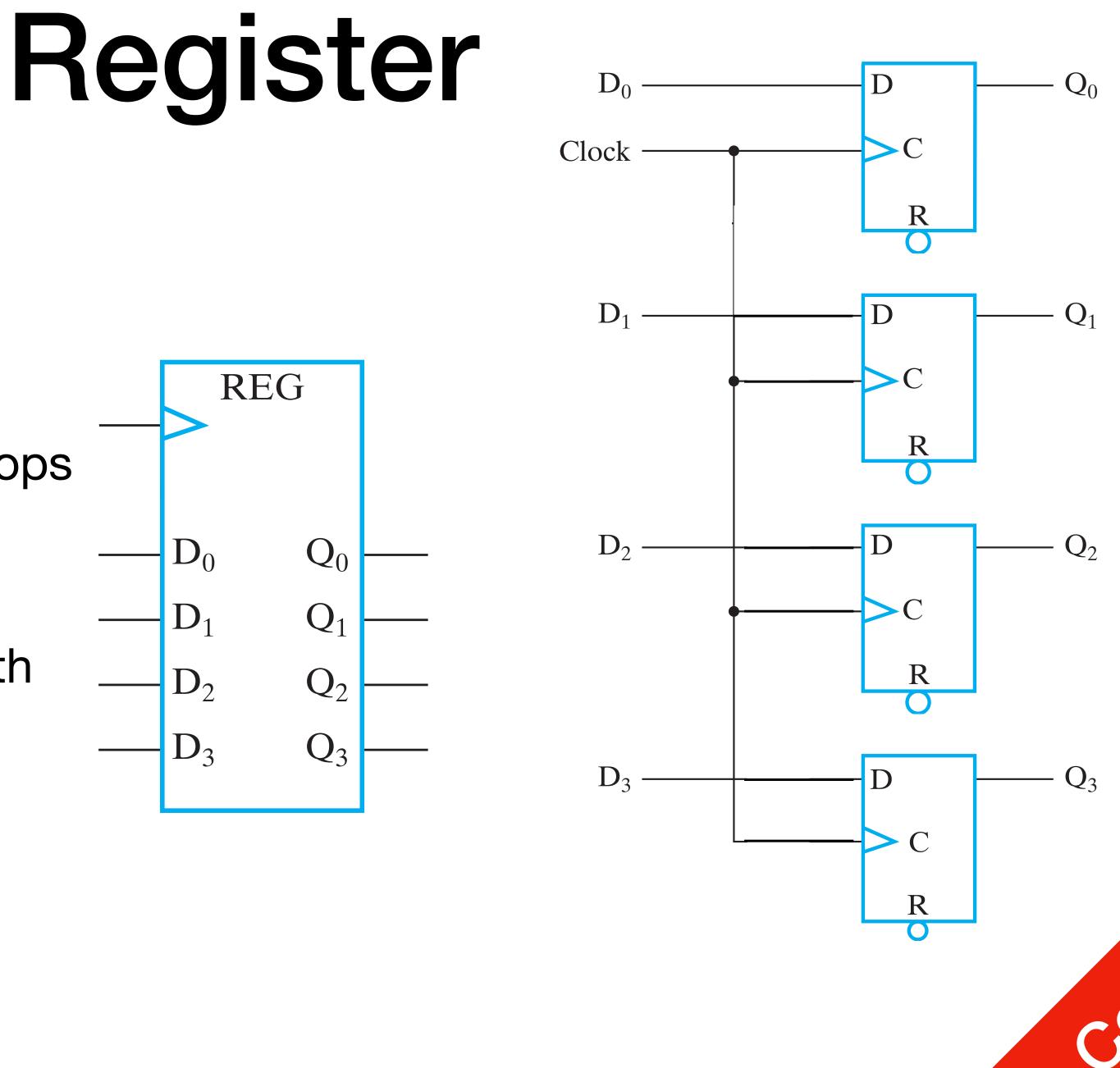

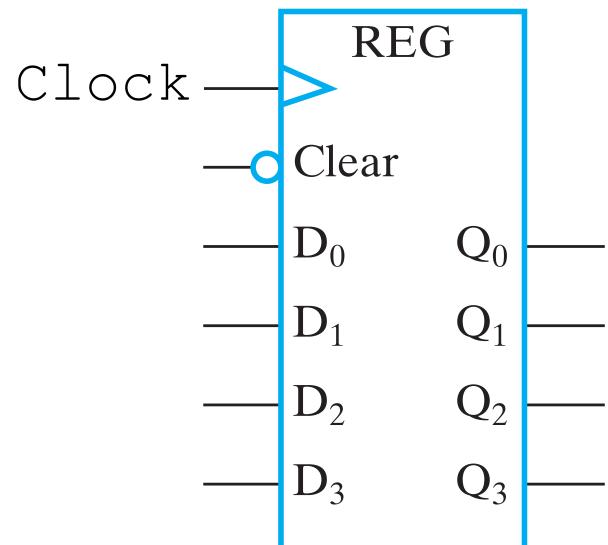

• *n*-bit register: uses *n* flip-flops stores *n* bits of information

- *n*-bit register: uses *n* flip-flops stores *n* bits of information

- An array of D flip-flops with reset

- *n*-bit register: uses *n* flip-flops stores *n* bits of information

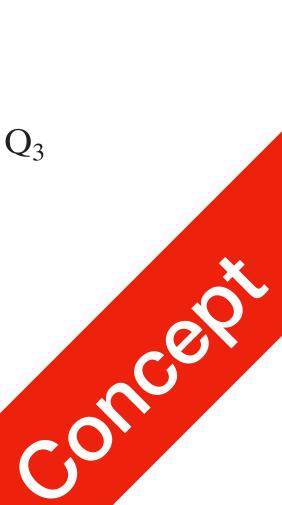

- An array of *D* flip-flops with reset

- Clear: set register to all 0s

## Register

- *n*-bit register: uses *n* flip-flops

stores *n* bits of information

- An array of *D* flip-flops with reset

- Clear: set register to all Os

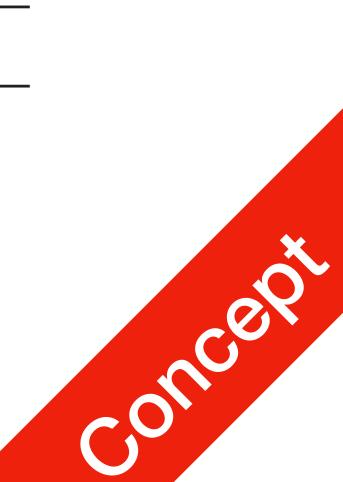

- Loading: set register to  $D_{3:0}$ Triggered by Load or Clock

- All registers are most likely wired to one Clock

- Loading a register: assigning new values to all *n*-bits of a register

- Clearing a register: change all *n*-bits of a register to 0s

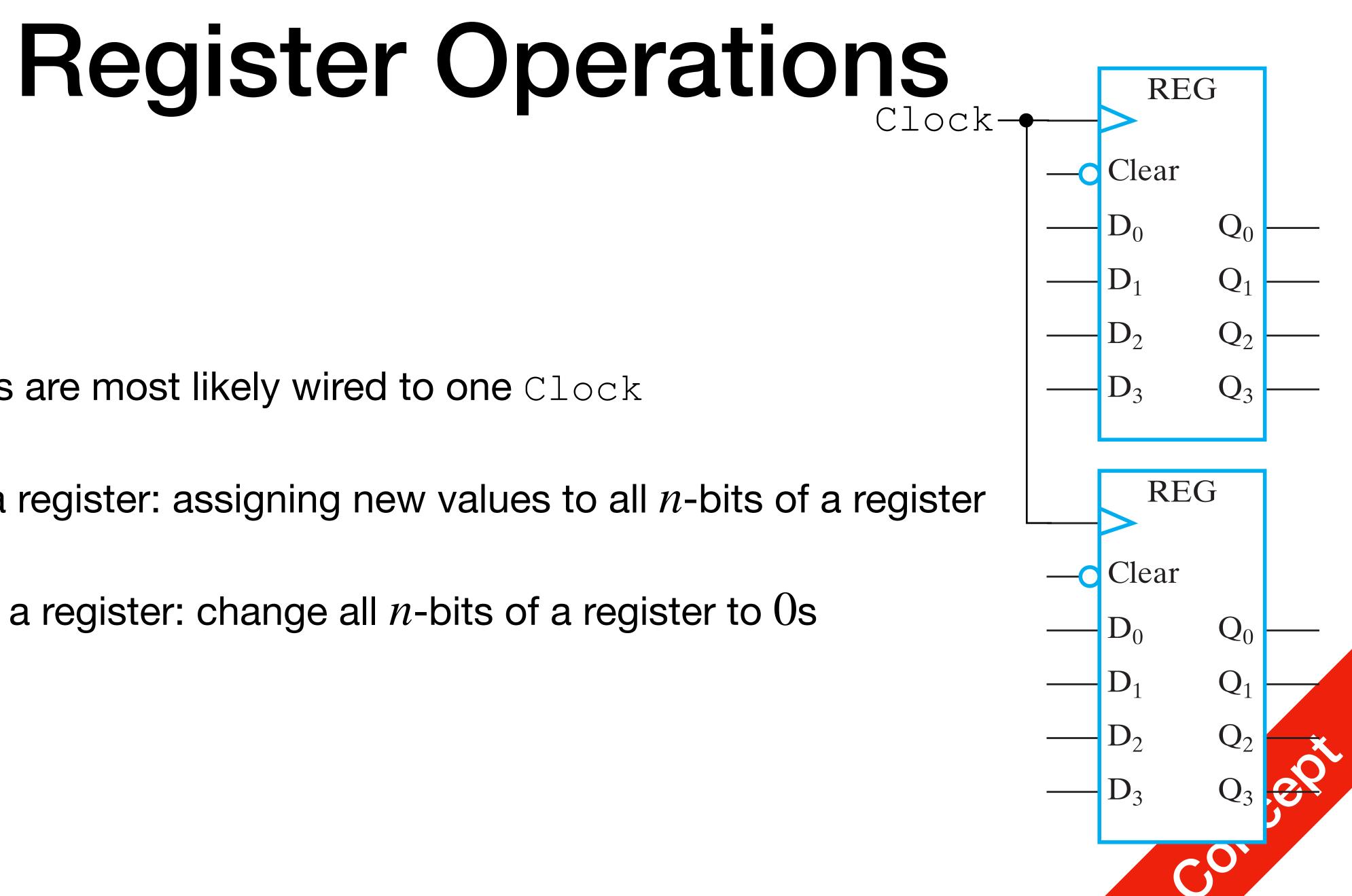

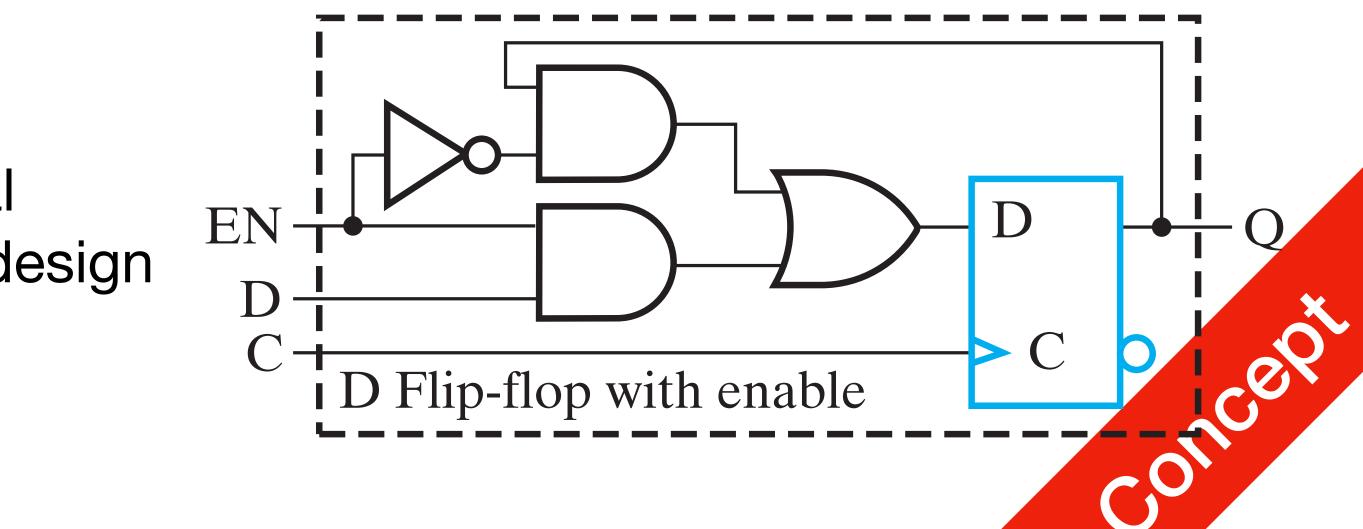

### What if we don't want to **P1** Registers change the value of a register?

- Clock: generates a constant train of pulses triggering the C of each registers

- **Clock gating**  $\bullet$

- Adding an Enabler to each C of each register

- Bad idea: leads to different propagation delay between the CLK and the Input D

### What if we don't want to **P1** Registers change the value of a register?

- Clock: generates a constant train of pulses triggering the C of each registers

- Use D flip-flops with **built-in Enabler (Correct!)**

- The CLK goes directly to C

- Input D combined with EN signal Ensure same propagation delay design

Why can't we use a regular enabler at D?

## Registers

- What is a register?

- Basic Functions of a single Register

- Loading: set values to input

- Clearing: set values to 0

- Enabling: preserving existing values

## **x86 Registers** And how addition is performed on your Computer CPU

## Common CPU Processor Architectures

- These are all von Neumann architecture designs

- X86 architecture (Intel CPUs, AMD CPUs)

**P2**

Example

- X86-64 architecture (64bit version of X86)

- ARM (iPhone, iPad, most Android devices)

- MIPS (Others, including instructional)

### **P2** Example

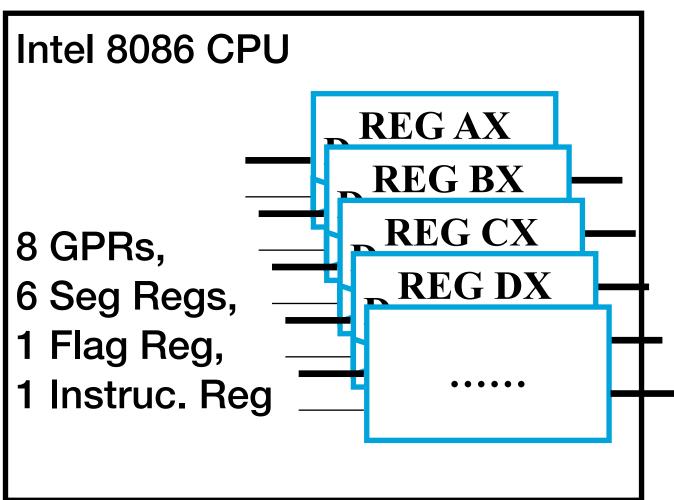

# X86 CPU Registers

- These registers are located on the CPU chips (in Datapath)

- 8 General-Purpose Registers (GPRs)

- **AX**: Accumulator register. Used in arithmetic operations

- **BX**: Base register. Used as a pointer to data

- **CX**: Counter register. Used in shift/rotate instructions and loops.

- **DX**: Data register. Used in arithmetic operations and I/O operations.

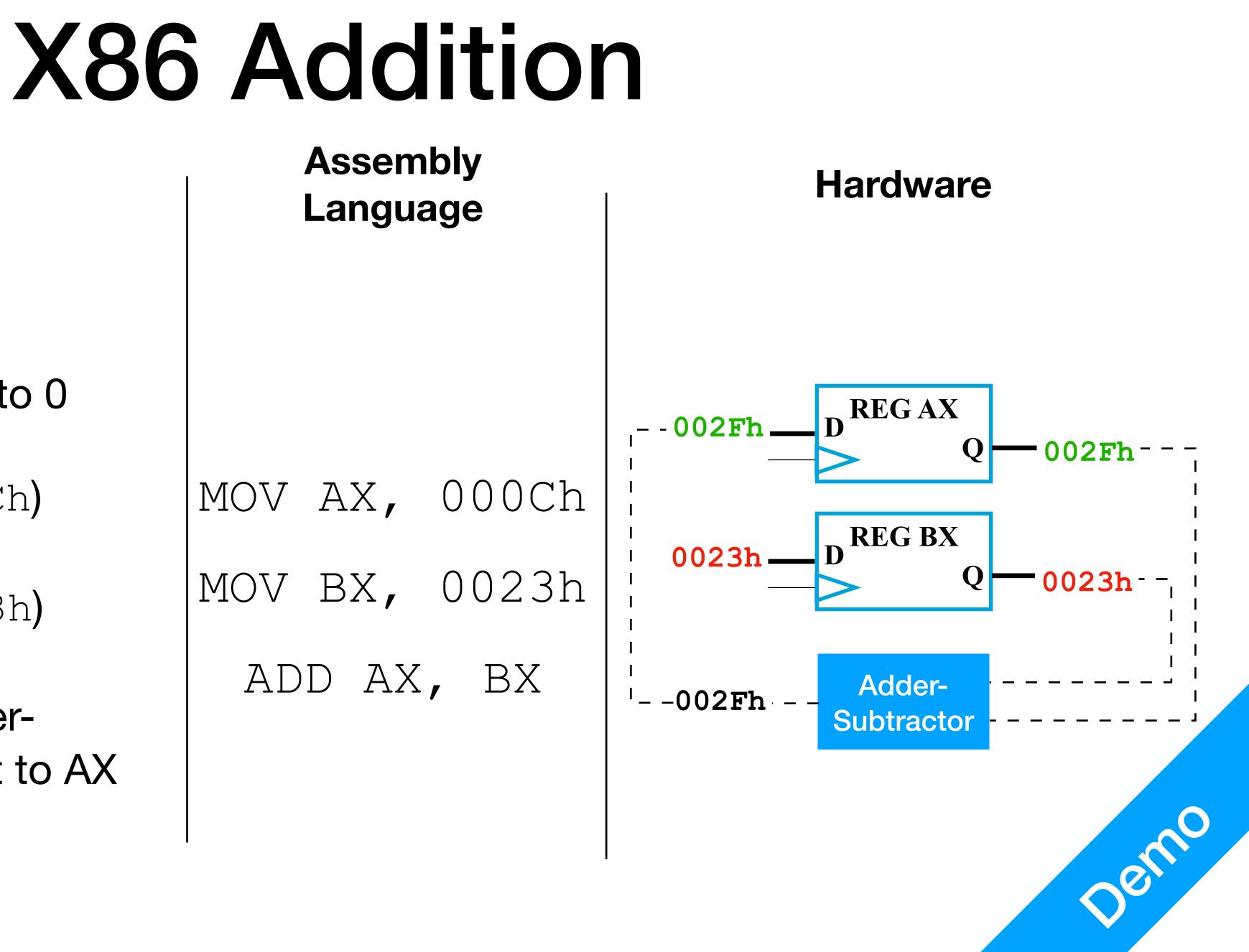

- 12 + 35

- Uses AX, BX: Cleared to 0

- 1. Load AX with 12 (000Ch)

- 2. Load BX with 35 (0023h)

- 3. Perform Add with Adder-Subtractor, Load result to AX

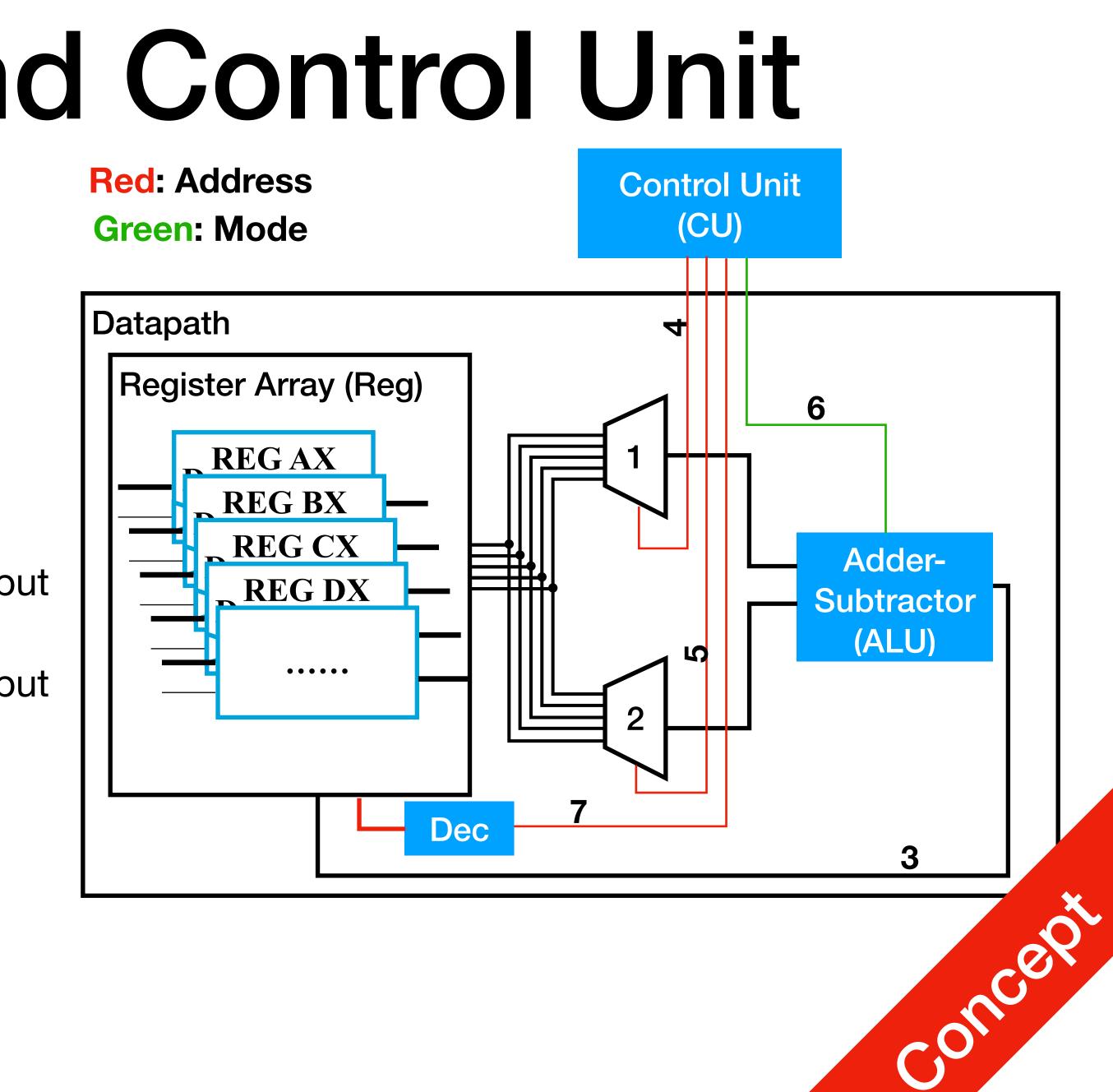

## **Example** Datapath and Control Unit

- Control Unit at each time step, provide

- Operation Code e.g. mov (66b8, etc.), add (6601, etc.)

- Parameters e.g. ax, bx, 12, 35

- Datapath

- Select Register for Input and Output (Multiplexer)

- Feed input into Register or Functional Blocks (Adder-Subtractor)

## **Example** Datapath and Control Unit

- ALU connected to Reg for 1st input

- 2. ALU connected to Reg for 2nd input

- 3. ALU connected to Reg to store result

- 4. CU tells ALU which register to take as 1st input

- 5. CU tells ALU which register to take as 2st input

- CU tells ALU which operation to do 6.

- CU tells which Reg to store result in Using decoder and EN on each Register

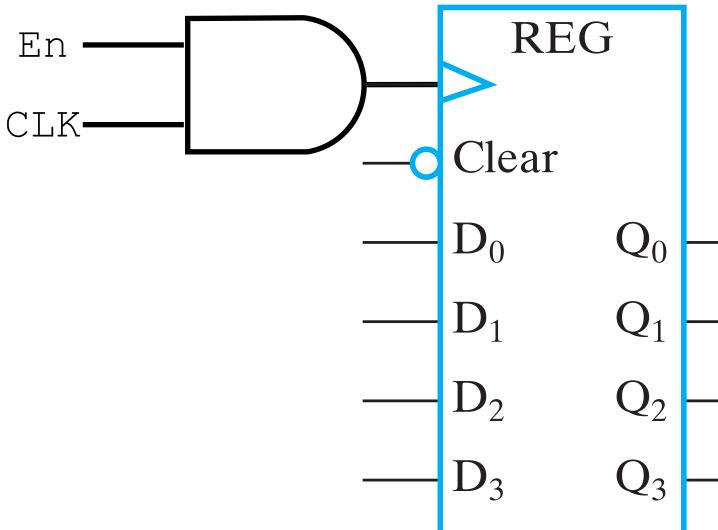

## Register Transferring Microoperations; Transferring Operations

# **Register Operations**

- Components

- set of registers in the system

- operations performed on the data

- control that supervises the sequence of operations in the system

Movement of data stored in registers and Processing performed on the data

- Microoperation: An elementary operation performed on data stored in registers

- Multiple Registers: add, subtract, etc.

## Microoperation

• Single Register (Transfer Operations): load, clear, shift, count, etc.

### P3 Transferring

# Register Transfer VHDL

|               | Operator | Example             |                    | Operator        | Example                             |

|---------------|----------|---------------------|--------------------|-----------------|-------------------------------------|

| Assignment    | <=       | ax <b>&lt;=</b> 12h | <b>Bitwise AND</b> | and             | ax <b>and</b> bx                    |

| Reg. Transfer | <=       | ax <b>&lt;=</b> bx  | <b>Bitwise OR</b>  | or              | ax <b>or</b> bx                     |

| Addition      | +        | ax + bx             | <b>Bitwise NOT</b> | not             | not ax                              |

| Subtration    |          | ax – bx             | <b>Bitwise XOR</b> | XOY             | ax <b>xor</b> bx                    |

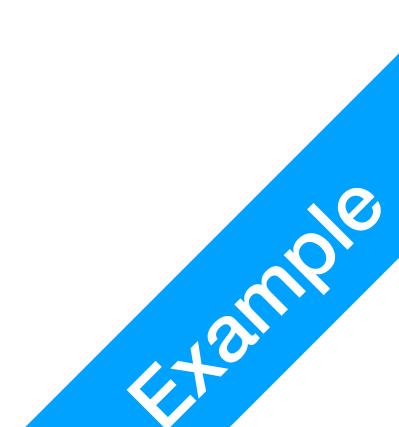

| Shift Left    | sll      | ax <b>sll</b> 2     | Vectors            | ax(3 down to 0) | ax(3 down to 0)                     |

| Shift Right   | srl      | ax <b>srl</b> 2     | Concatenate        | æ               | ax(7 down to 4)<br>&ax(3 down to 0) |

- 1) ax **<=** 12 2) bx <= 18 3) cx <= ax + bx 4) dx <= bx - ax

- What are the binary values after these operations? (Assuming 8bit registers)

- ax: 0000 1100

- bx: 0001 0010

- cx: 0001 1110

- dx: 0000 0110

• What are the binary values after these operations? (Assuming 8bit registers)

- ax: 0000 1100

- bx: 0011 0000

- cx: 0110 0000

- dx: 0000 0110

- 1) ax **<=** 12 2) bx <= 20 3) cx <= ax and bx 4) dx  $\leq$  ax or bx

- What are the binary values after these operations? (Assuming 8bit registers)

- ax: 0000 1100

- bx: 0001 0100

- cx: 0000 0100

- dx: 0001 1100

- 1) ax **<=** 12 2) bx <= 20 3) cx <= not ax 4) dx  $\leq$  ax **xor** bx

- What are the binary values after these operations? (Assuming 8bit registers)

- ax: 0000 1100 bx: 0001 0100 cx: 1111 0011

- dx: 0001 1000

- 1) ax **<=** 12 2) bx <= 20 3) cx <= ax(5 down to 2)4) dx  $\leq$  bx(7 down to 4) 5) bx <= ax(5 down to 2) & bx(7 down to 4)

- What are the binary values after these operations? (Assuming 8bit registers)

- Answer:

- ax: 0000 1100

- bx: 0001 0100

- cx: 0000 0011

- dx: 0000 0001

- bx: 0011 0001

### 1) ax **<=** 8 2) bx <= 23 3) cx <= bx(7 down to 4) & a(3 down to 0)4) dx <= ax(4 down to 1) sll 4

- Answer:

- ax: 0000 1000

- bx: 0001 0111

- cx: 0001 1000

- dx: 0100 0000

• What are the binary values after these operations? (Assuming 8bit registers)

- 1) ax **<=** 13 2) bx <= 27 3) cx <= bx srl 2 4) dx <= (ax and bx) xor (not cx)

- Answer:

- ax: 0000 1101

- bx: 0001 1011

- cx: 0000 0110

- dx: 1111 0000

• What are the binary values after these operations? (Assuming 8bit registers)

### 1) ax **<=** 2Eh 2) bx $\leq ax(7 \text{ down to } 4) xor ax(3 \text{ down to } 0)$ 3) cx <= (ax slr 2) or (ax sll 1) 4) dx <= bx and cx

- Answer:

- ax: 0010 1110

- bx: 0000 1100

- cx: (0000 1011) or (0101 1100): (0101 1111)

- dx: 0000 1100

• What are the binary values after these operations? (Assuming 8bit registers)

## Transferring Register Transfer Operations

|               | Operator | Example             |                    | Operator        | Example                             |

|---------------|----------|---------------------|--------------------|-----------------|-------------------------------------|

| Assignment    | <=       | ax <b>&lt;=</b> 12h | <b>Bitwise AND</b> | and             | ax <b>and</b> bx                    |

| Reg. Transfer | <=       | ax <b>&lt;=</b> bx  | <b>Bitwise OR</b>  | or              | ax <b>or</b> bx                     |

| Addition      | +        | ax + bx             | <b>Bitwise NOT</b> | not             | ax <b>not</b> bx                    |

| Subtration    |          | ax – bx             | <b>Bitwise XOR</b> | XOY             | ax <b>xor</b> bx                    |

| Shift Left    | sll      | ax <b>sll</b> 2     | Vectors            | ax(3 down to 0) | ax(3 down to 0)                     |

| Shift Right   | srl      | ax <b>srl</b> 2     | Concatenate        | &               | ax(7 down to 4)<br>&ax(3 down to 0) |