## CSCI 150 Introduction to Digital and Computer System Design Lecture 4: Sequential Circuit I

Jetic Gū 2020 Fall Semester (S3)

# Overview

- Focus: Basic Information Retaining Blocks

- Architecture: Sequential Circuit

- Textbook v4: Ch5 5.1, 5.2; v5: Ch4 4.1 4.2

- Core Ideas:

- Introduction 1.

- 2. *SR* and  $\overline{SR}$  Latches, *D* Latch

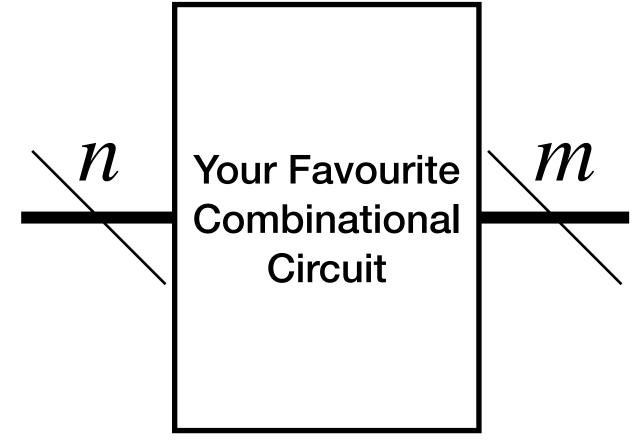

# **Combinational Logic Circuit** Design

• Design Principles

**P0**

Review

- Knows: fixed-Length input and output

- Knows: input/output mapping relations

- **Optimisation: Minimise overall delay**

• Features

**P0**

Review

- Fixed-Length input and output

- The same input will always give the same output

- Operations are simultaneous with minimum delay

# **Combinational Logic Circuit** Design

- Cannot handle variable length input

- Cannot store information

**P0**

Review

Cannot perform multi-step tasks

# **Combinational Logic Circuit** Design

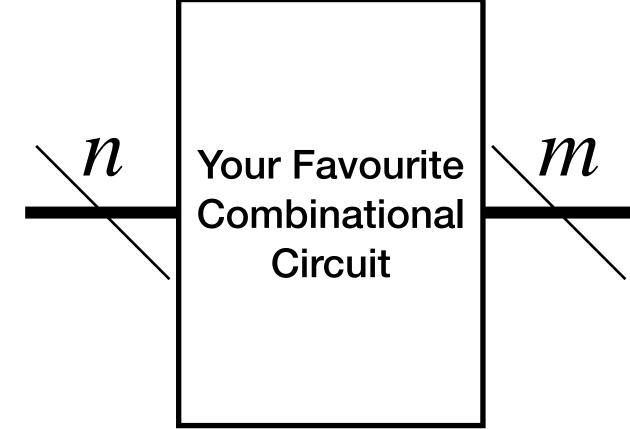

# Introduction to Sequential Circuit

# Solution

- Cannot handle variable length input

- Cannot store information

- Cannot perform multi-step tasks

# Solution: Storage!

- Cannot handle variable length input

- Cannot store information

- Cannot perform multi-step tasks

- Cannot handle variable length input

- Cannot store information

- Cannot perform multi-step tasks

- Storage of partial input

- Storage of partial results and states

- Storage of instructions

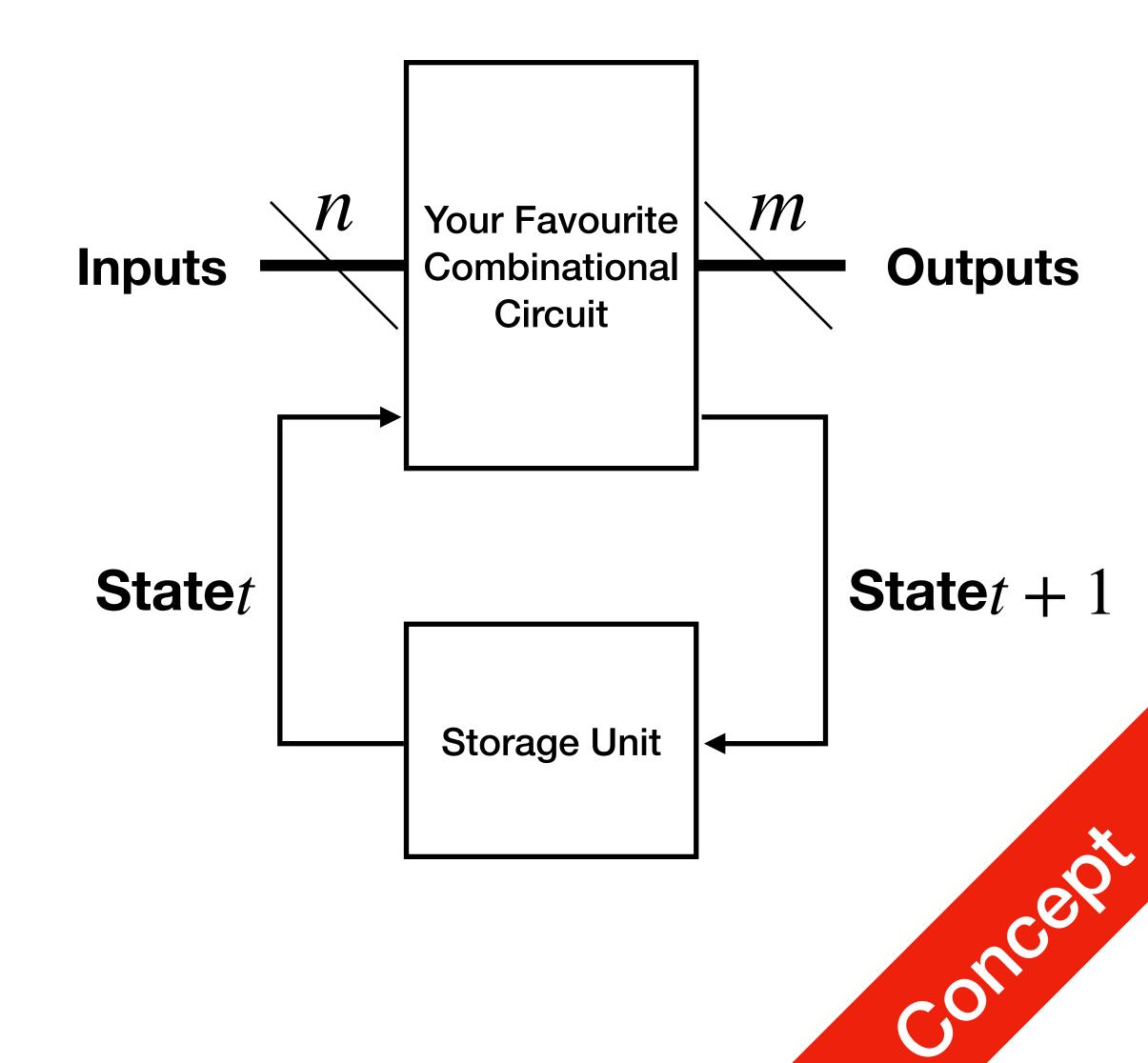

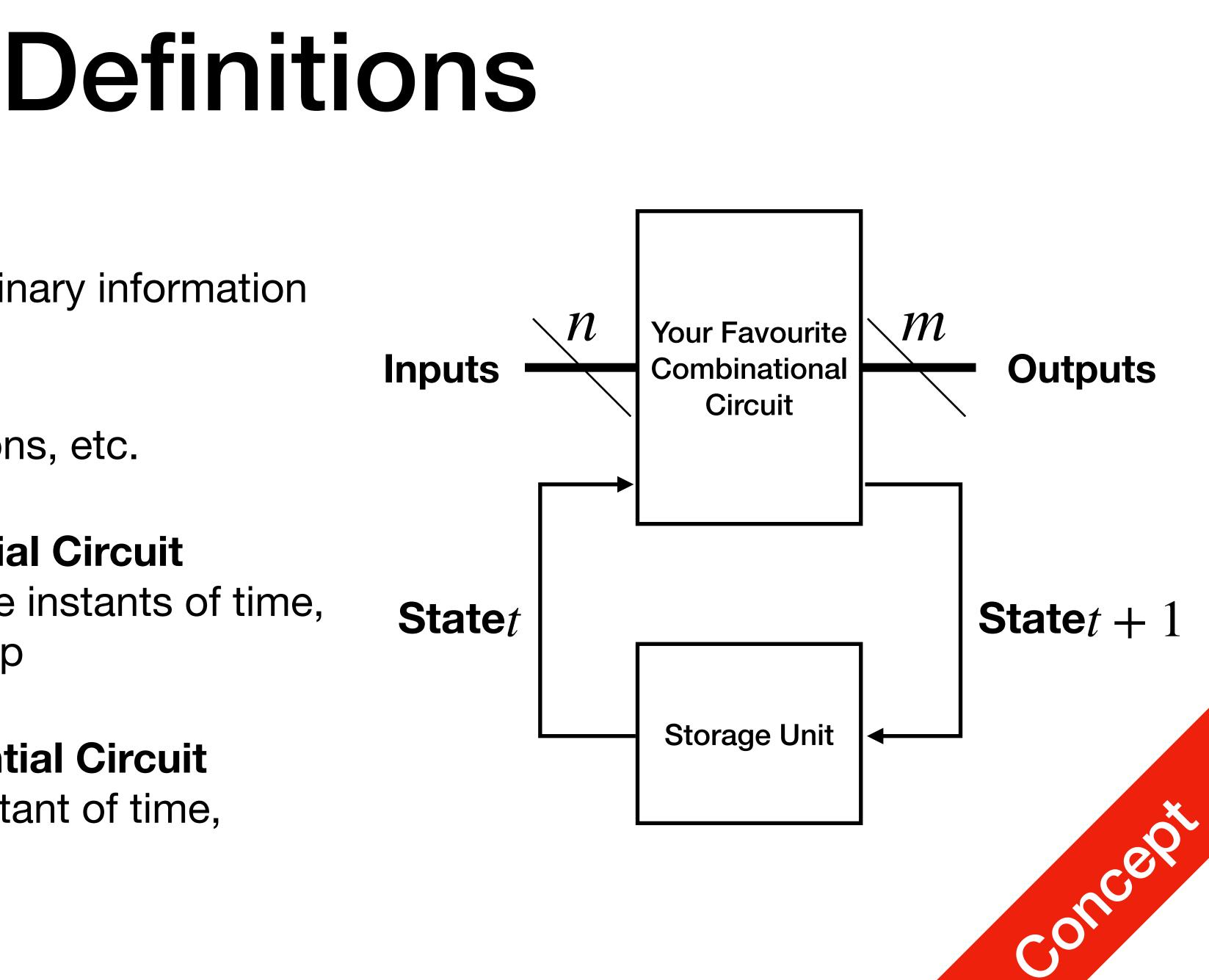

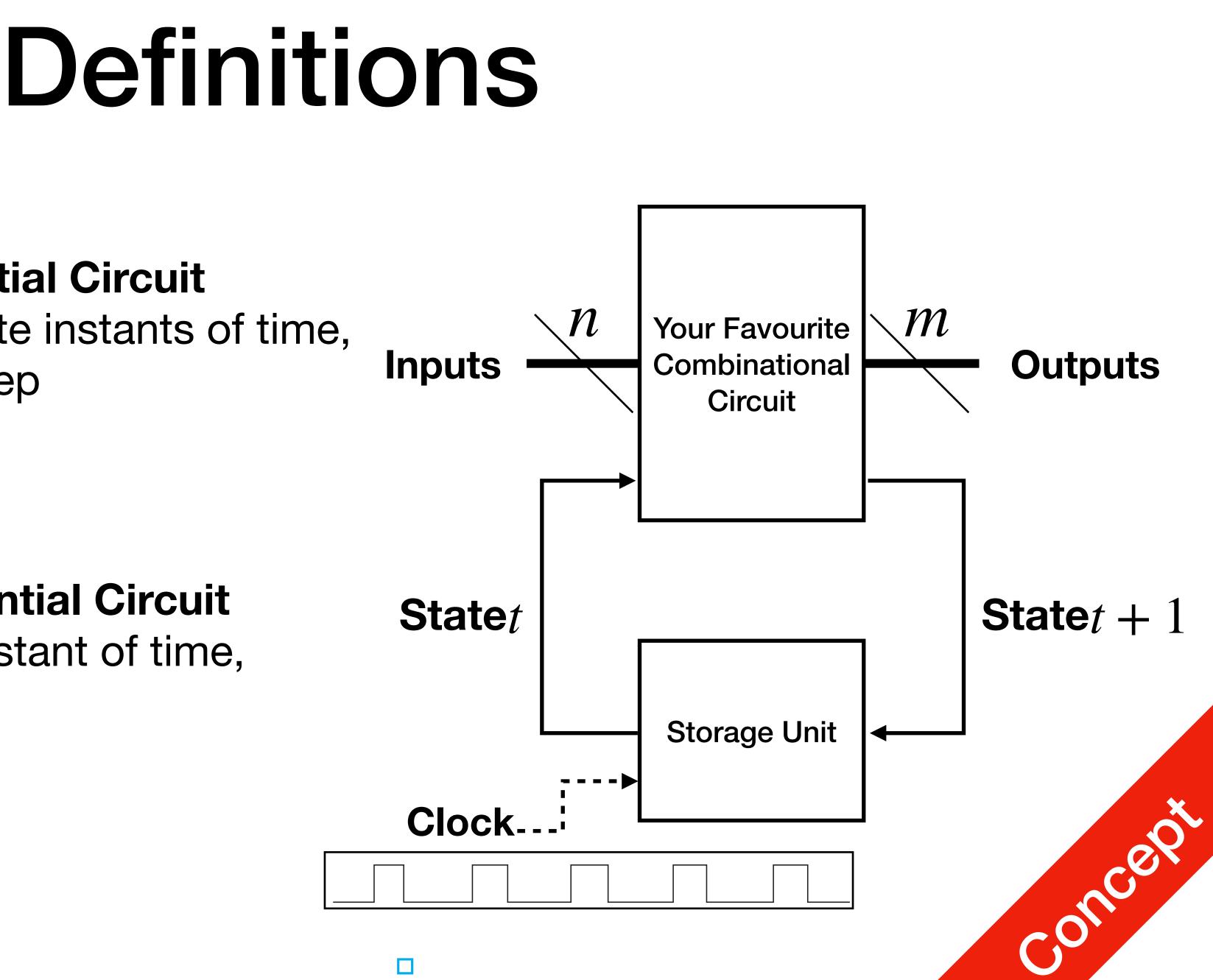

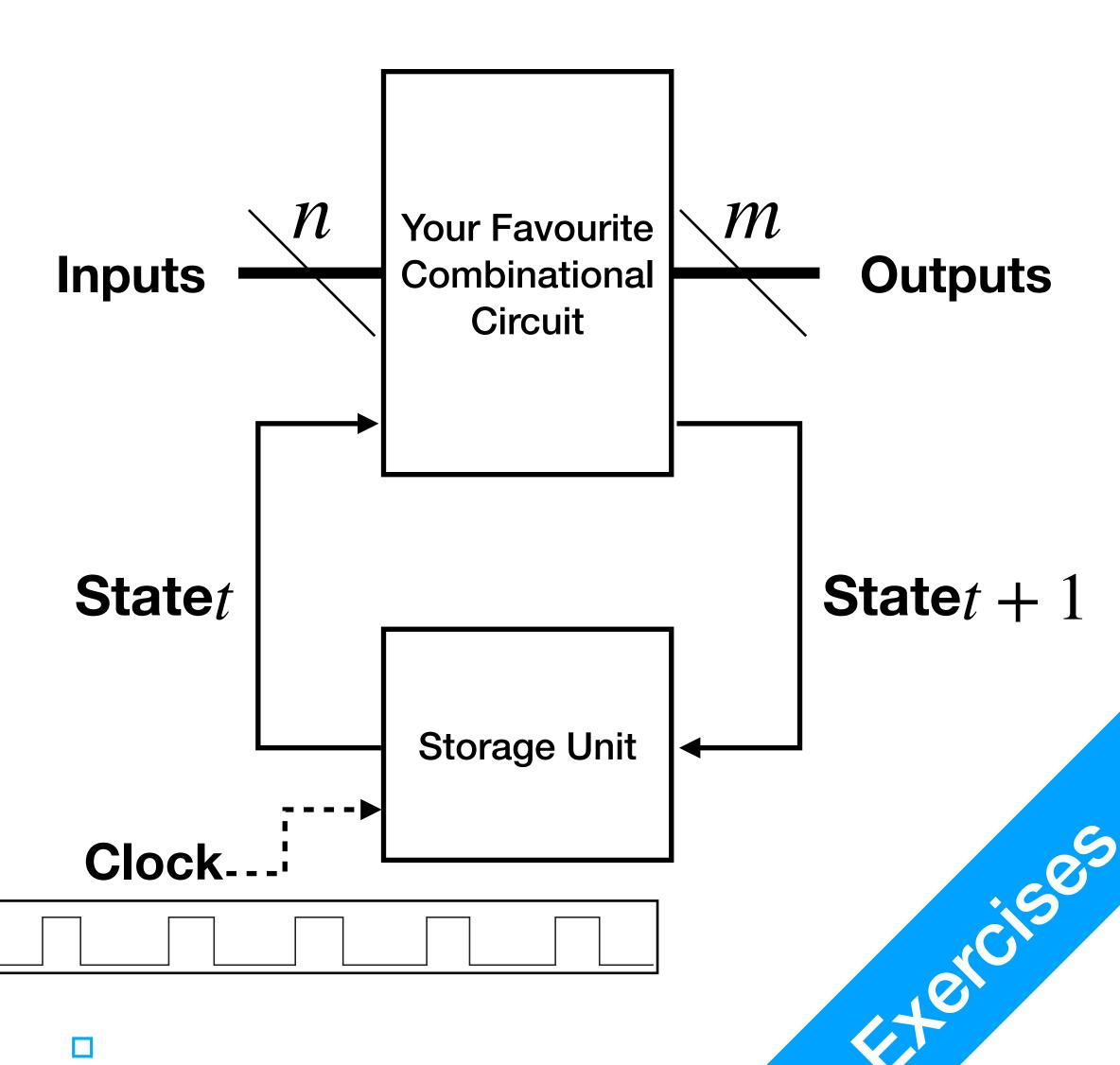

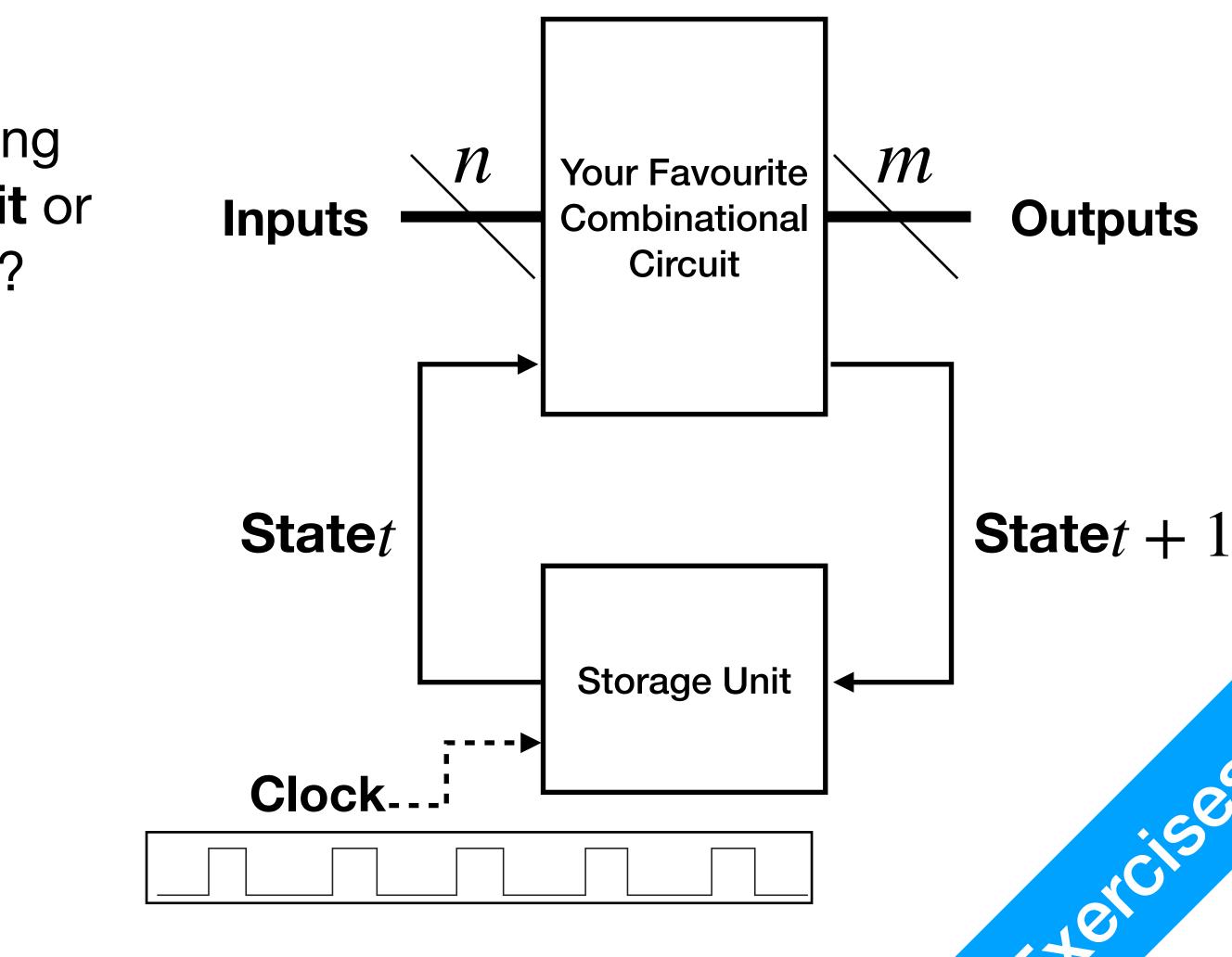

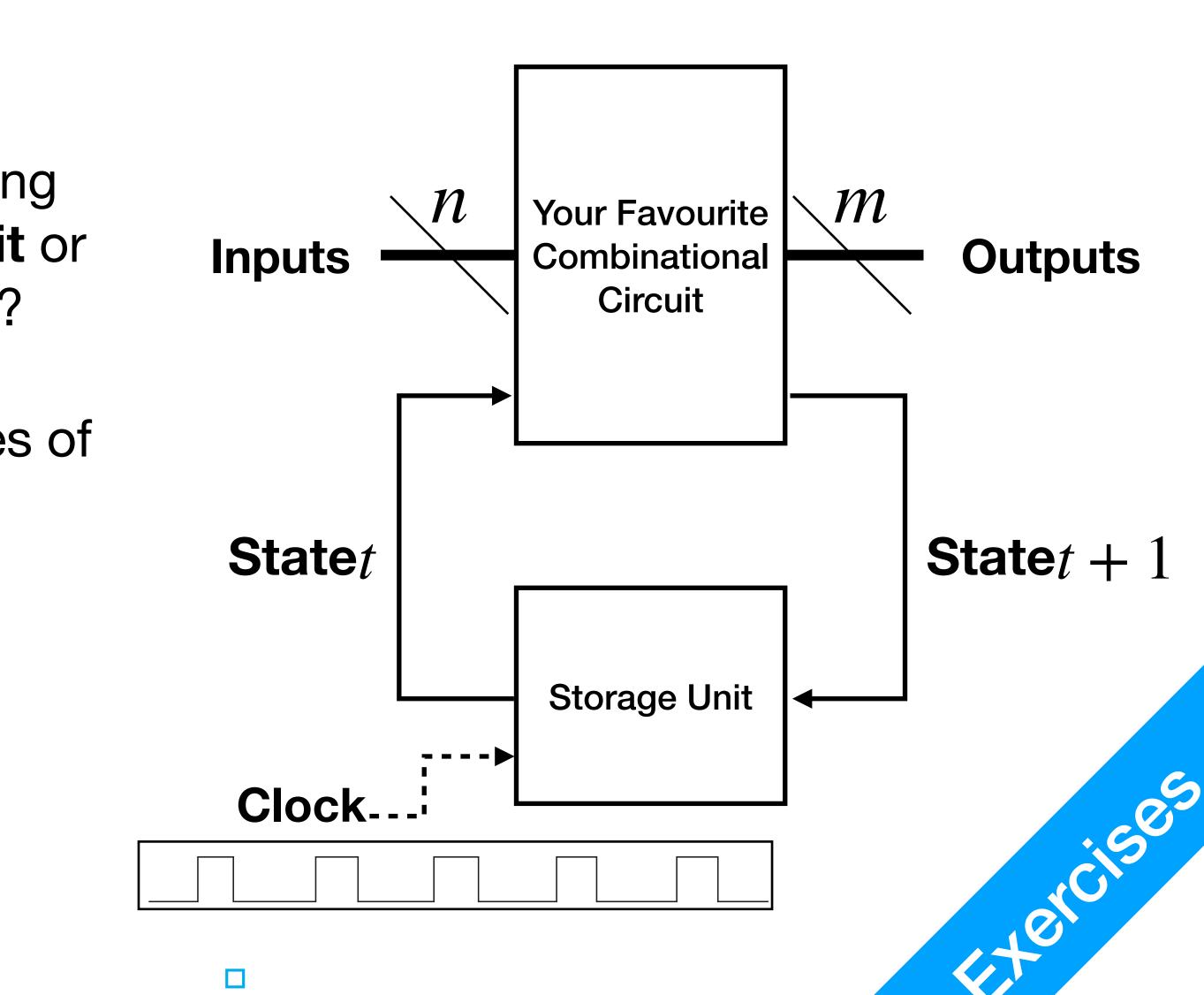

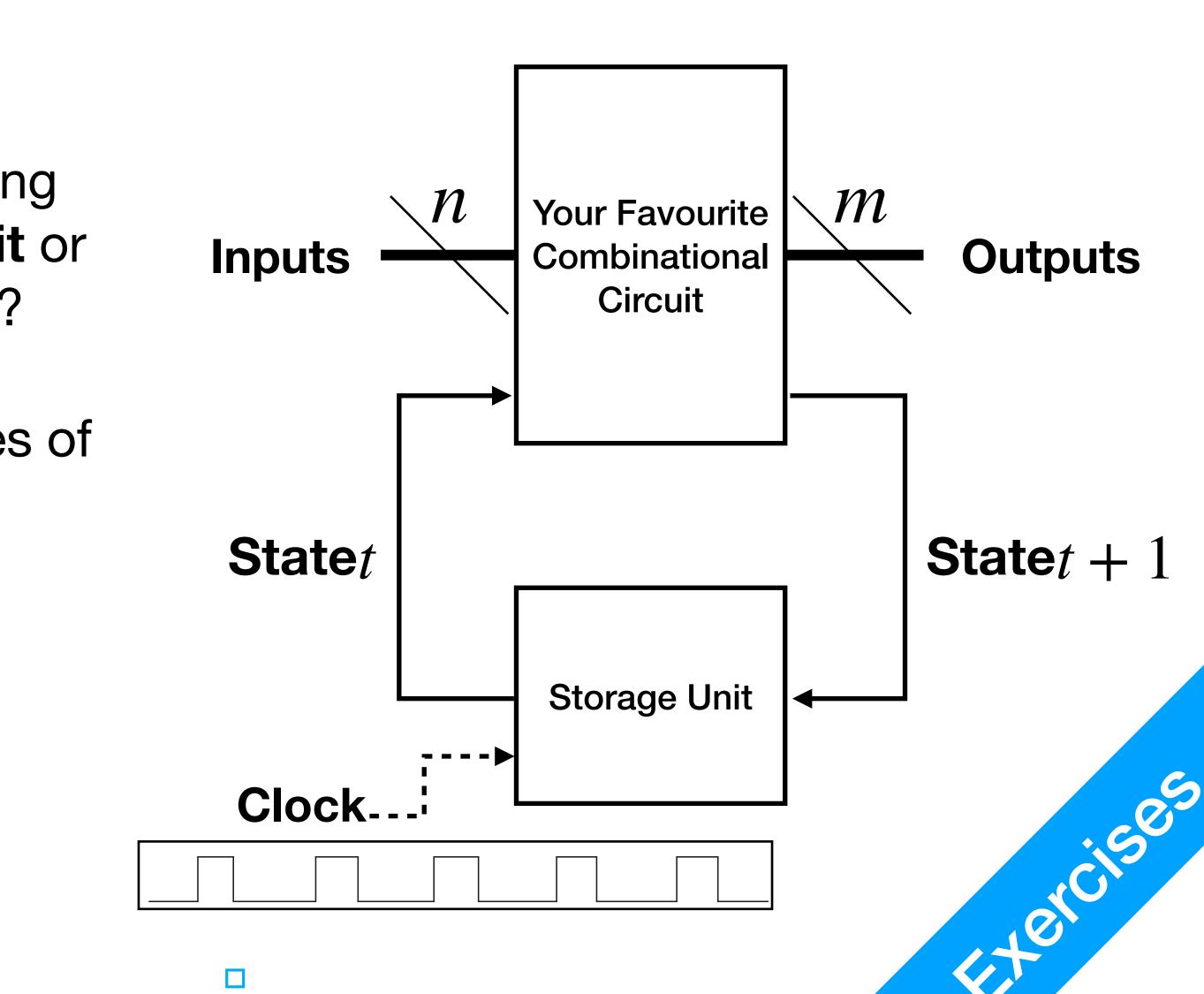

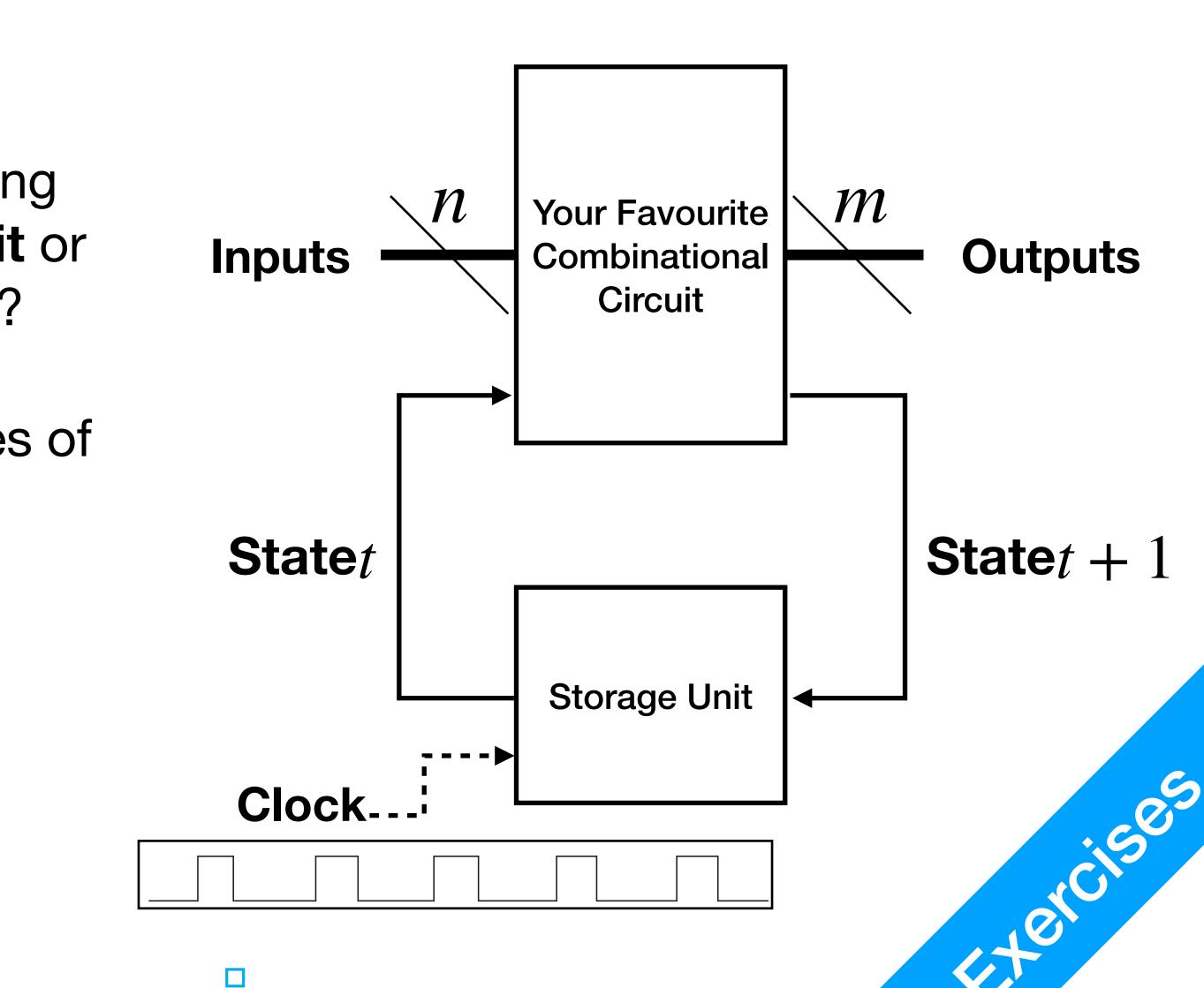

# Sequential Circuits

- Handle variable-length input

- Store information

- Multi-step tasks

- State Transition from time t to t + 1

### **Storage Elements** 1. circuits that can store binary information

## 2. State

partial results, instructions, etc.

- 3. Synchronous Sequential Circuit Signals arrive at discrete instants of time, outputs at next time step

- **Asynchronous Sequential Circuit** 4. Signals arrive at any instant of time, outputs when ready

- 3. Synchronous Sequential Circuit Signals arrive at discrete instants of time, outputs at next time step

- Has Clock

- 4. Asynchronous Sequential Circuit Signals arrive at any instant of time, outputs when ready

- May not have Clock

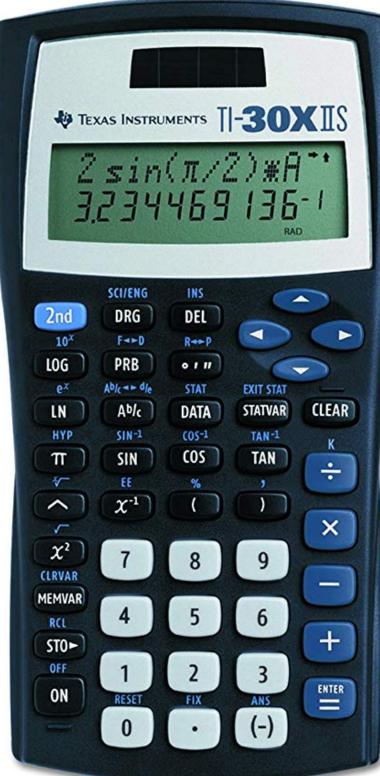

- 1. Are calculators designed using **Combinational Circuits** or **Sequential Circuits**?

- What about your microwave and toaster?

- What about your digital watch (not smart)?

- What about computers/smartphones?

# Question

# Question

## 2. Is this calculator using Asynchronous Sequential Circuit or Synchronous Sequential Circuit?

# Question

## 2. Is this calculator using Asynchronous Sequential Circuit or **Synchronous Sequential Circuit?**

• What are the states for this calculator?

- 2. Is this calculator using Asynchronous Sequential Circuit or **Synchronous Sequential Circuit?**

- What are the states for this calculator?

- What kind of information is stored?

# Question

# Question

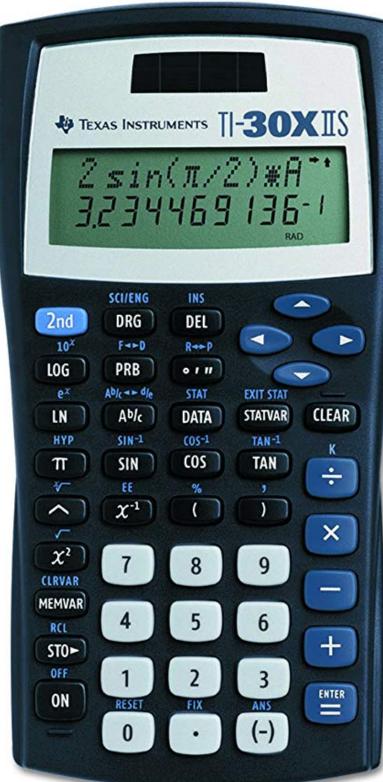

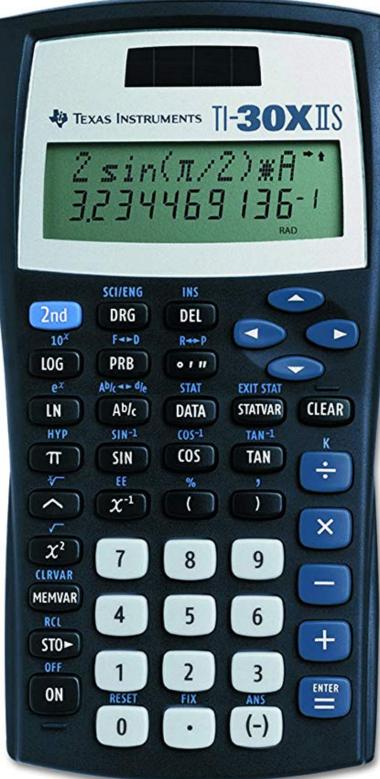

## 3. Is this calculator using **Asynchronous Sequential Circuit** or **Synchronous Sequential Circuit**?

# Question

## 3. Is this calculator using Asynchronous Sequential Circuit or **Synchronous Sequential Circuit?**

• What are the states for this calculator?

- 3. Is this calculator using Asynchronous Sequential Circuit or **Synchronous Sequential Circuit?**

- What are the states for this calculator?

- What kind of information is stored?

# Question

## 4. Is your laptop/PC/smartphone using Asynchronous Sequential Circuit or **Synchronous Sequential Circuit?**

# Question

- 4. Is your laptop/PC/smartphone using Asynchronous Sequential Circuit or Synchronous Sequential Circuit?

- What are the Input/Output devices of these computers?

- 4. Is your laptop/PC/smartphone using Asynchronous Sequential Circuit or Synchronous Sequential Circuit?

- What are the Input/Output devices of these computers?

- What are the storage devices?

- 4. Is your laptop/PC/smartphone using Asynchronous Sequential Circuit or Synchronous Sequential Circuit?

- What are the Input/Output devices of these computers?

- What are the storage devices?

- What about CPU?

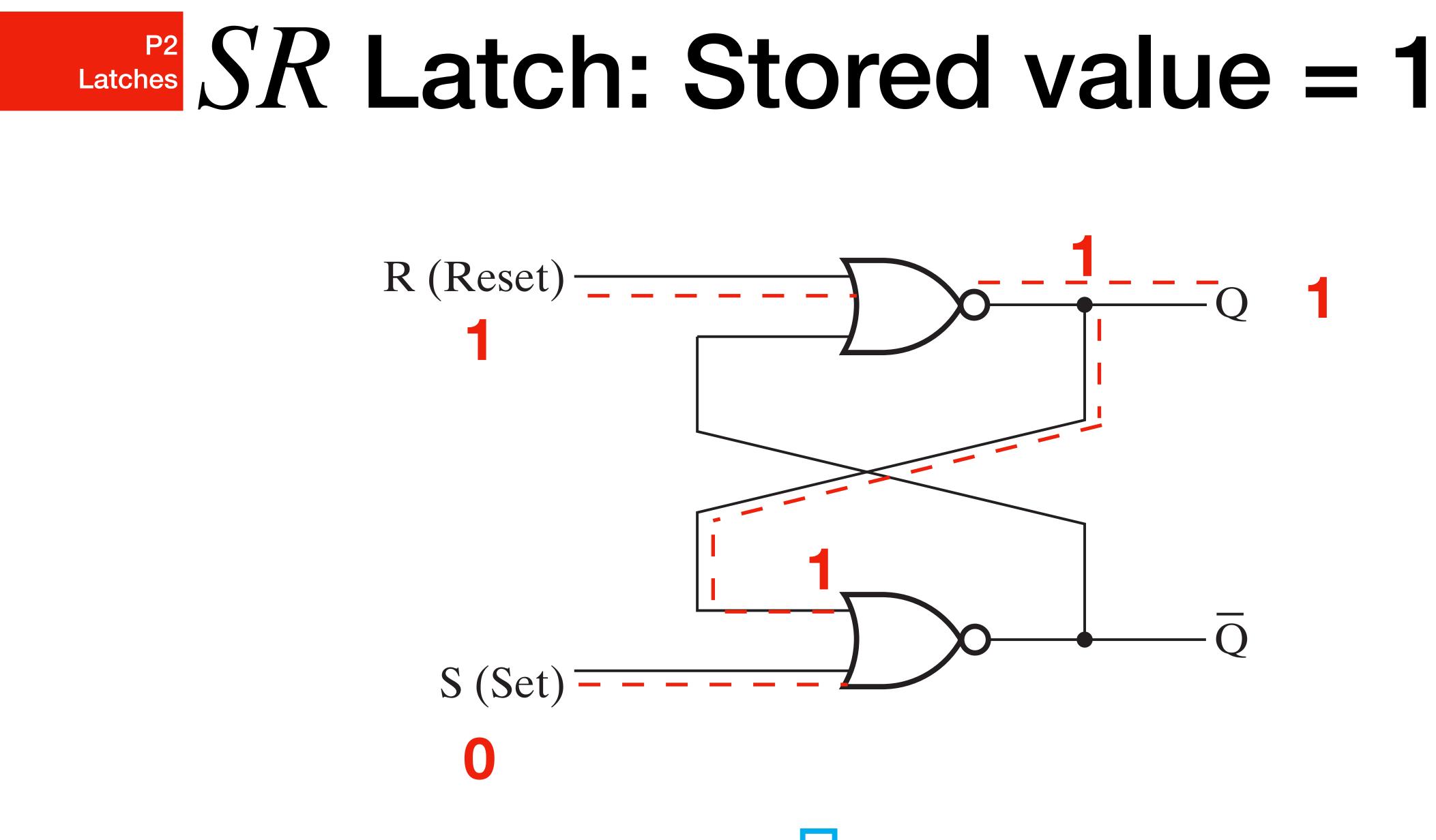

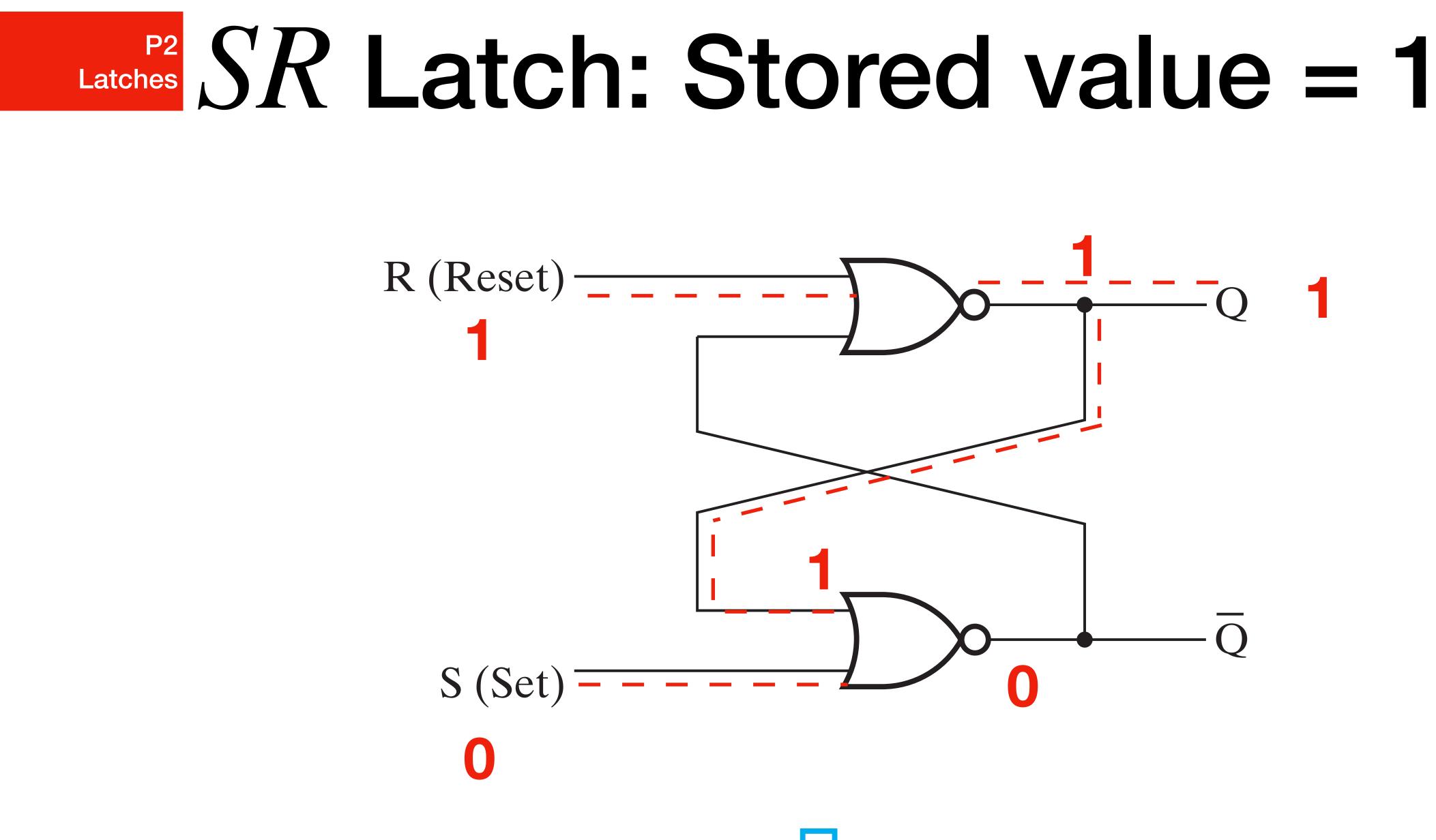

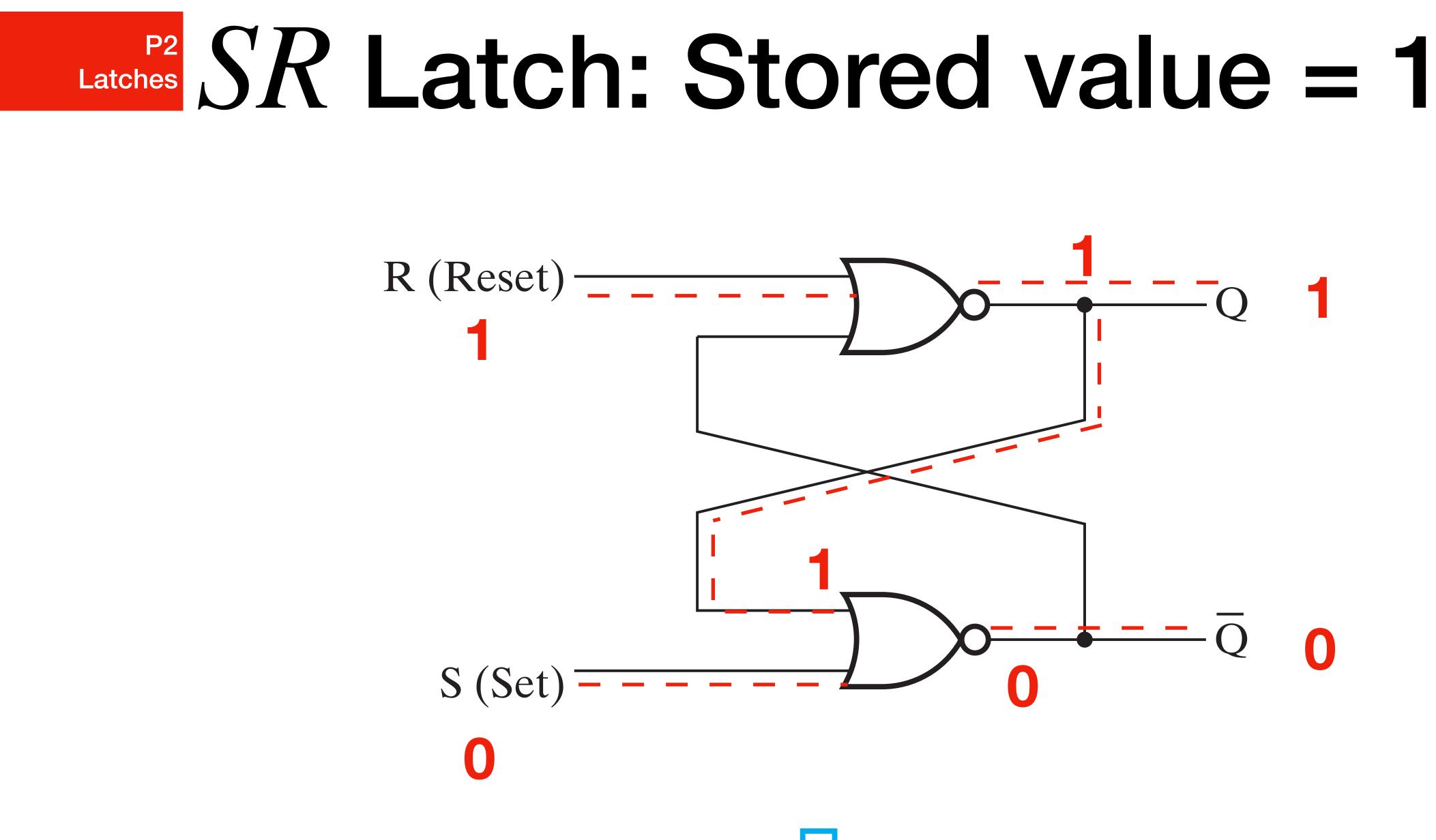

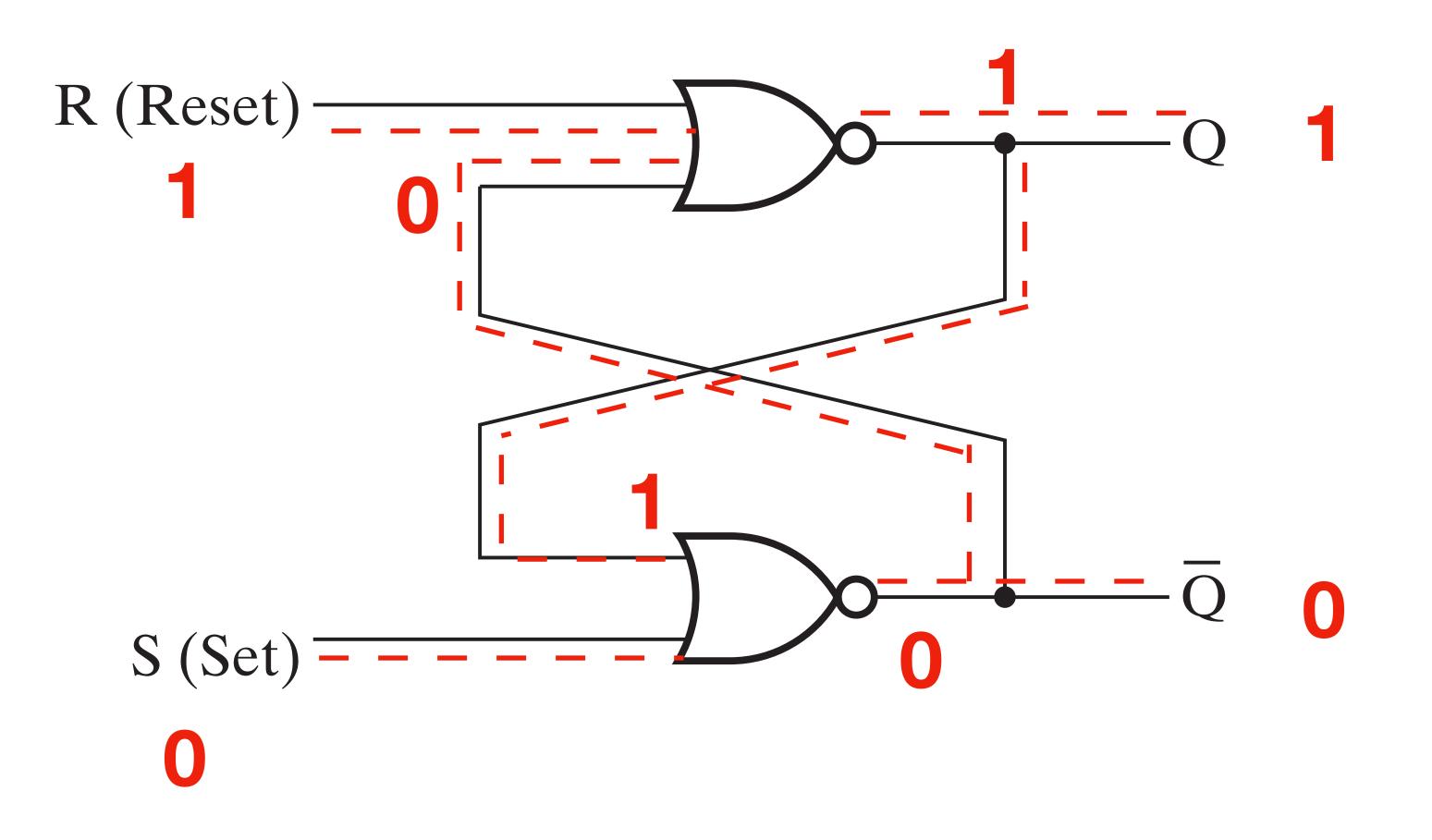

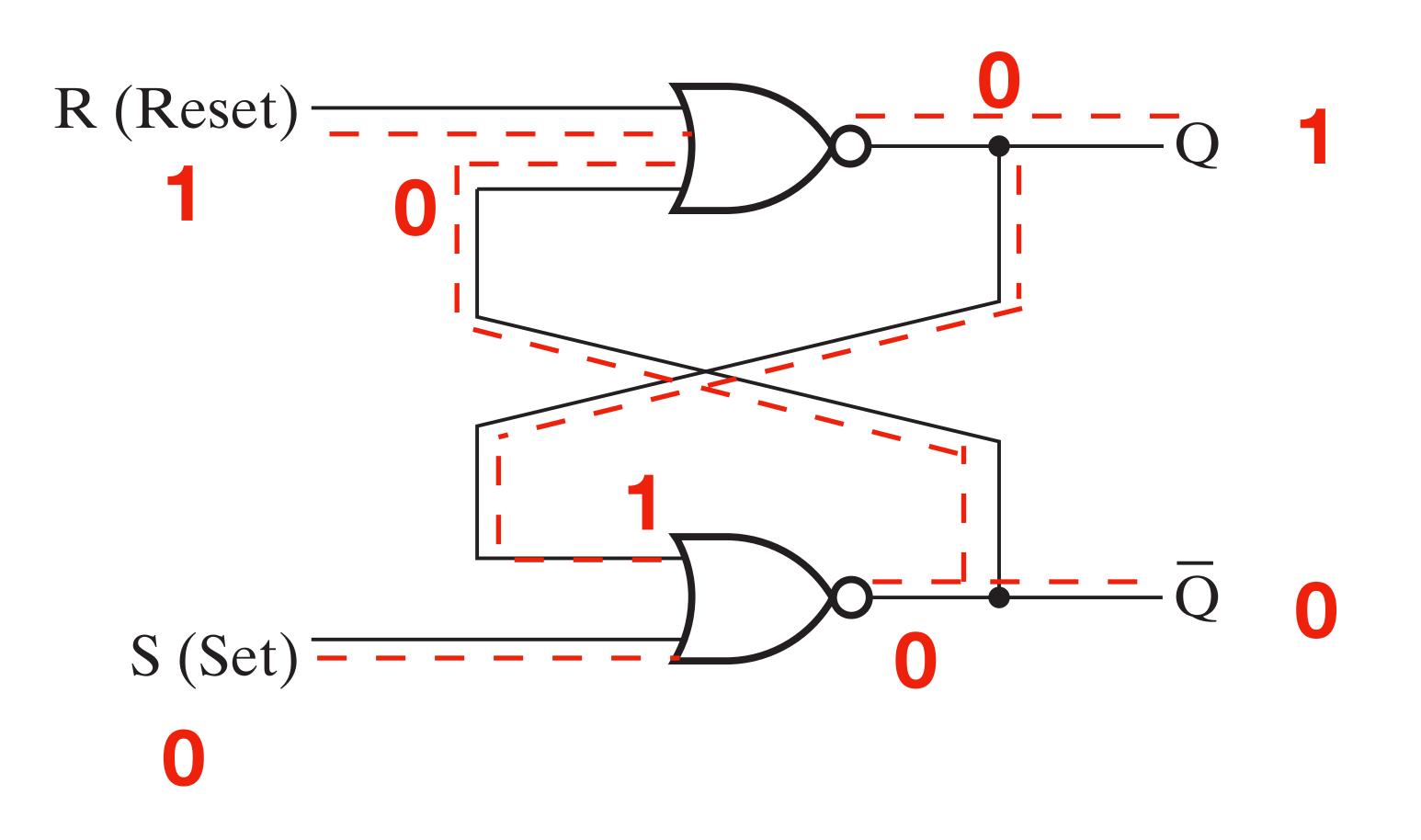

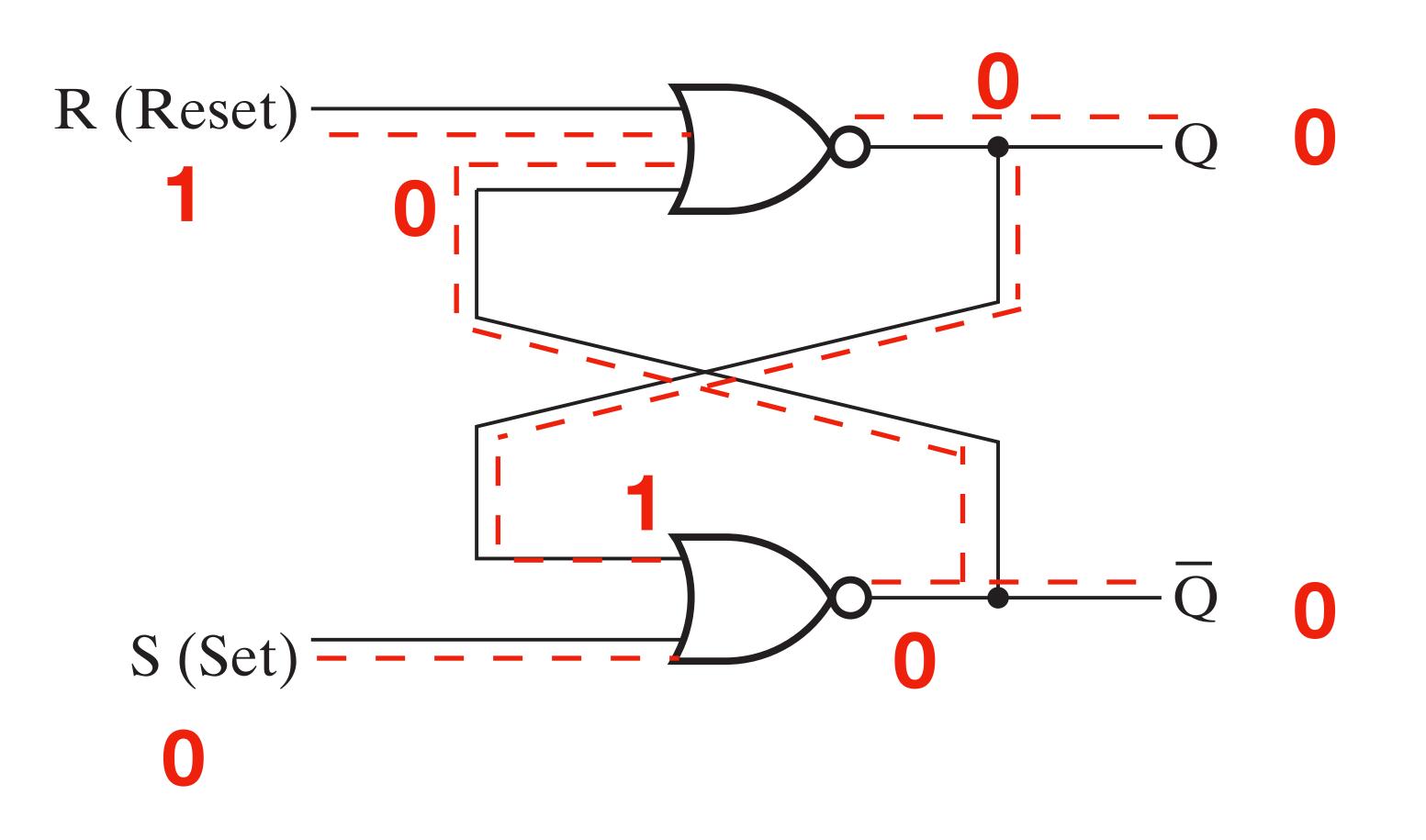

## Latches SR and SR Latches, D Latch

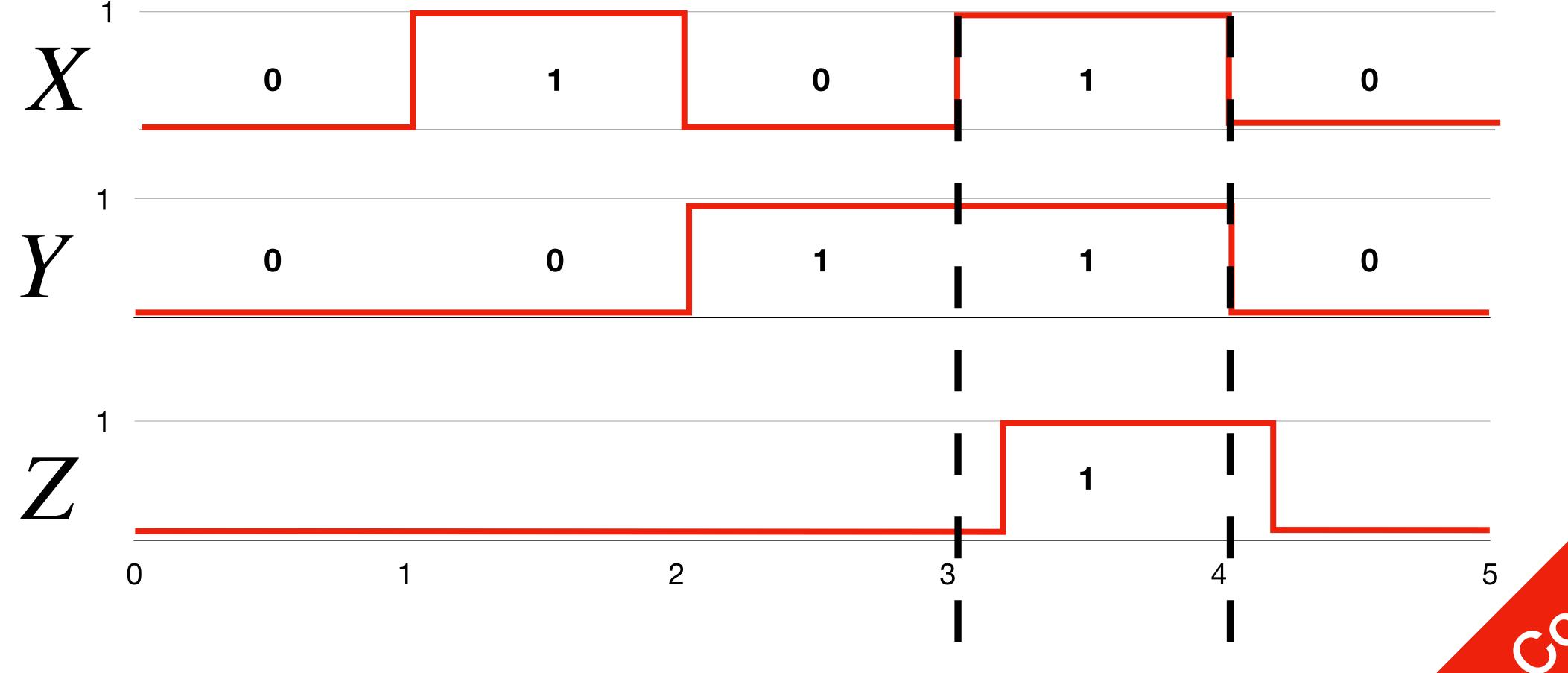

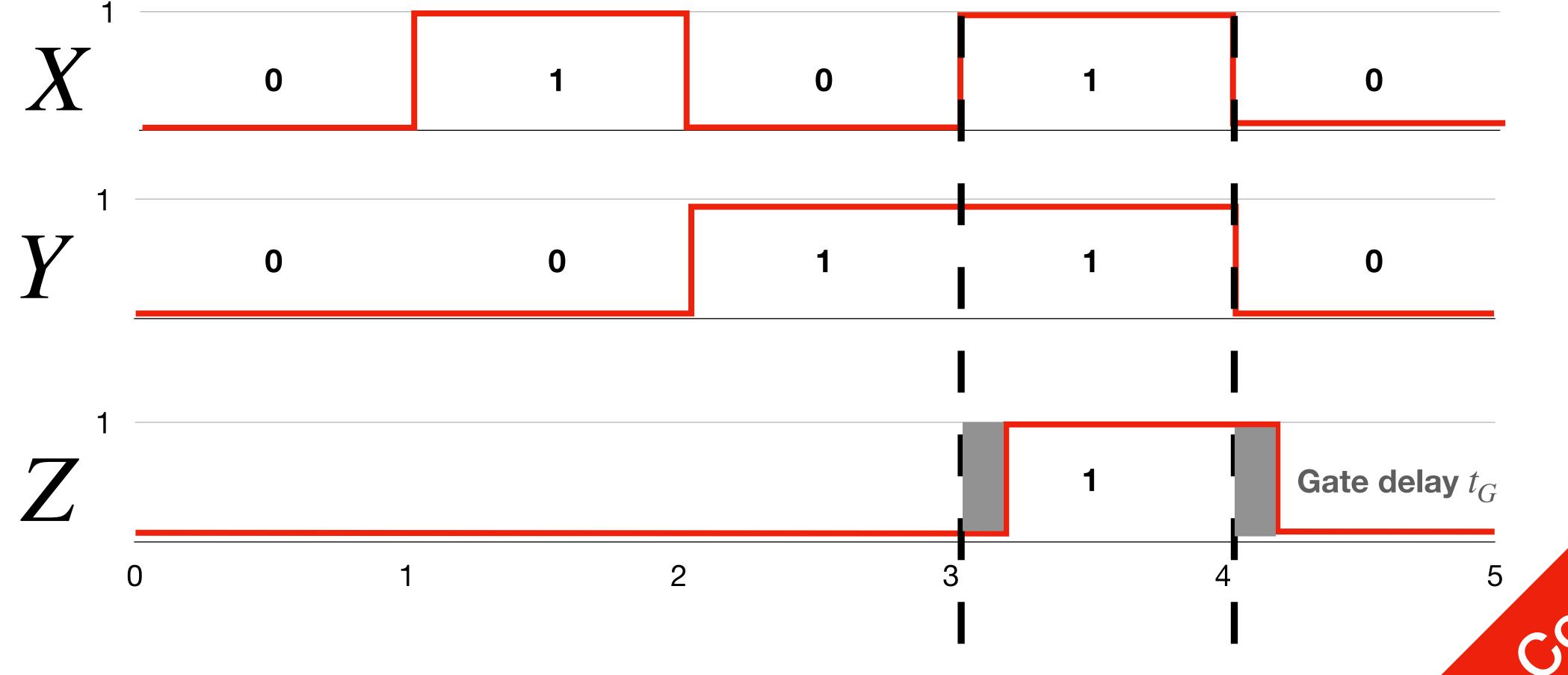

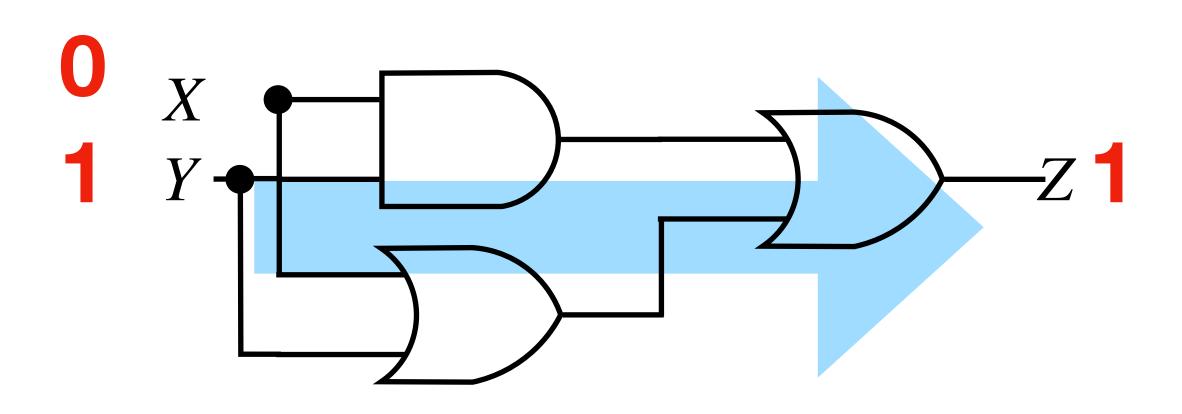

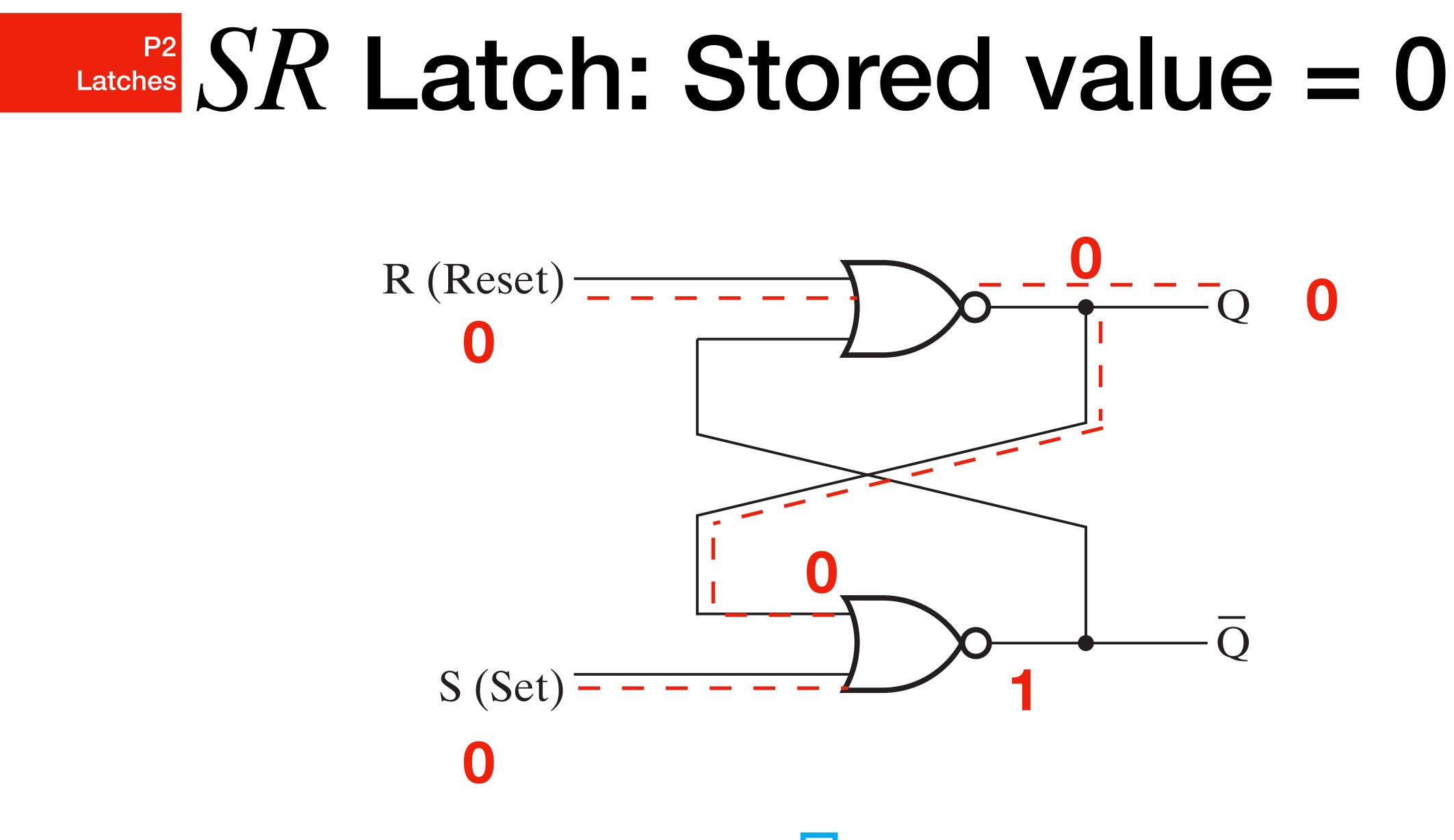

Stable State: the values in a circuit after brief changing due to delay in passing information, reaches a state where it doesn't change anymore -

Stable State: the values in a circuit after brief changing due to delay in passing information, reaches a state where it doesn't change anymore -

Stable State: the values in a circuit after brief changing due to delay in passing information, reaches a state where it doesn't change anymore -

signals, reach a state where they don't anymore

signals, reach a state where they don't anymore

signals, reach a state where they don't anymore

signals, reach a state where they don't anymore

What other scenarios might bring about these instabilities?

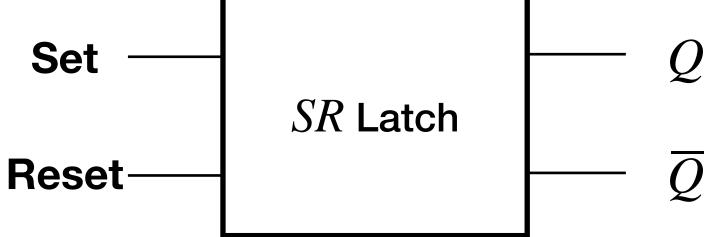

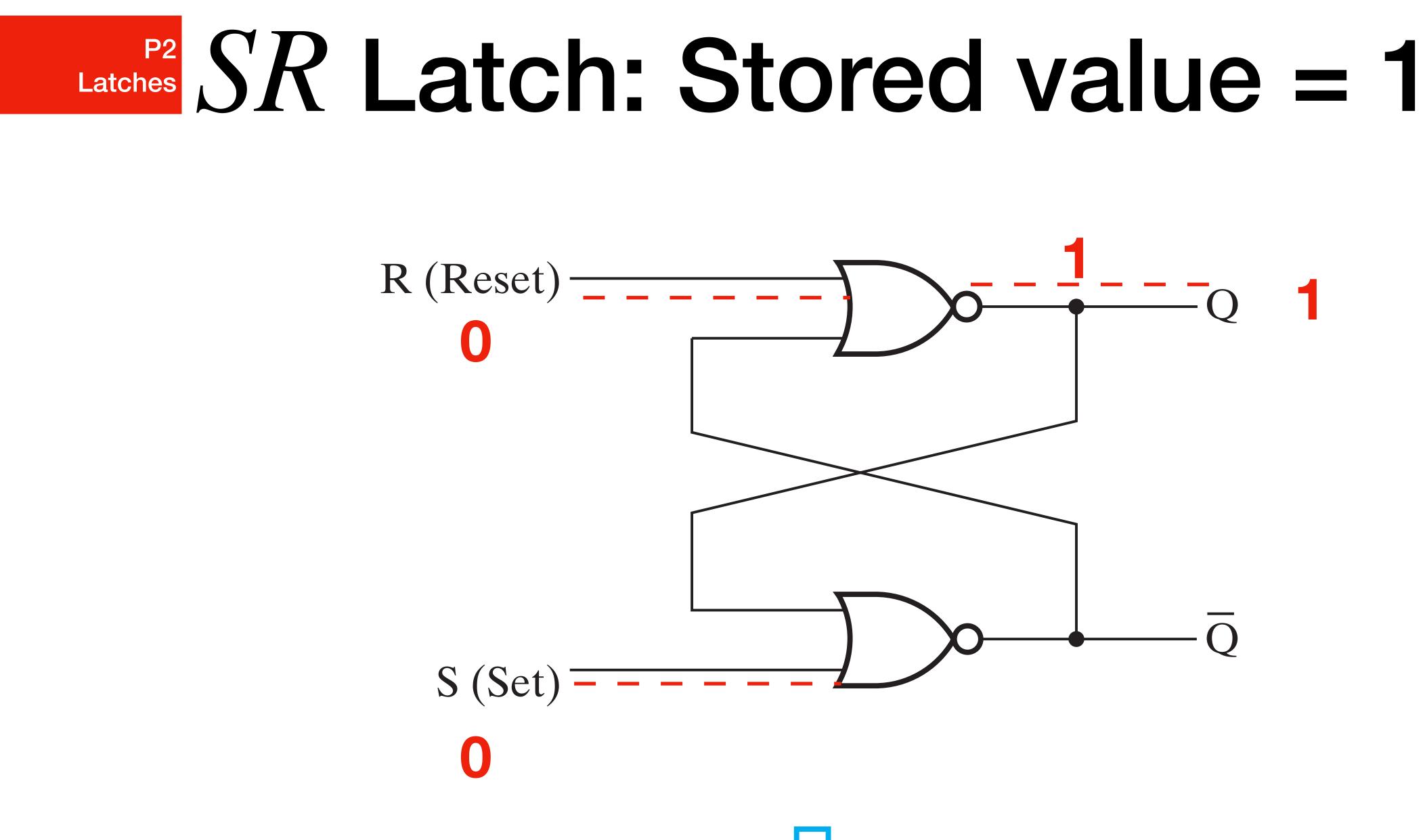

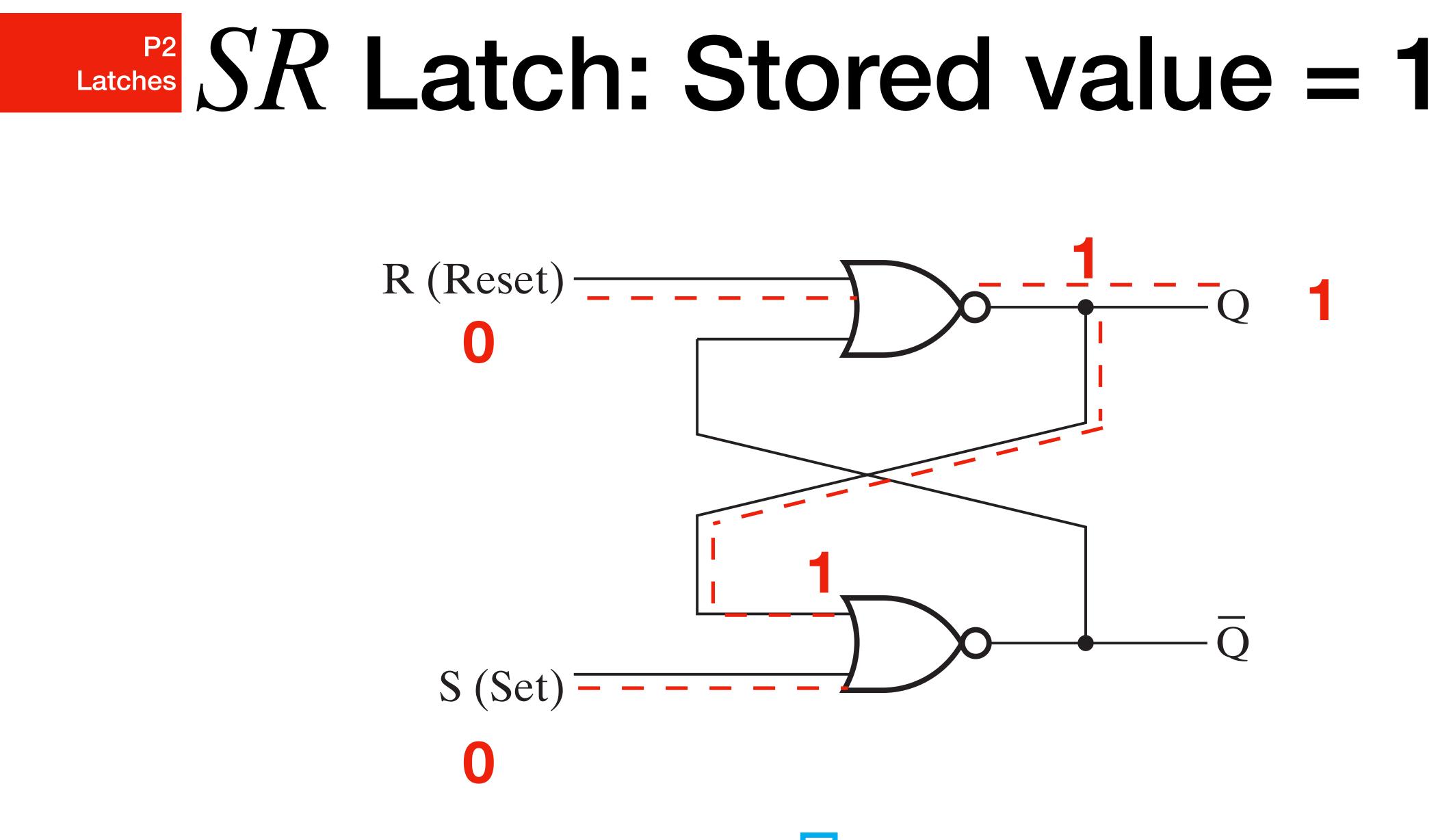

# Latches

- Basic Storage Elements

- Maintain a binary state indefinitely, as long as there's power

- The binary state inside can be changed

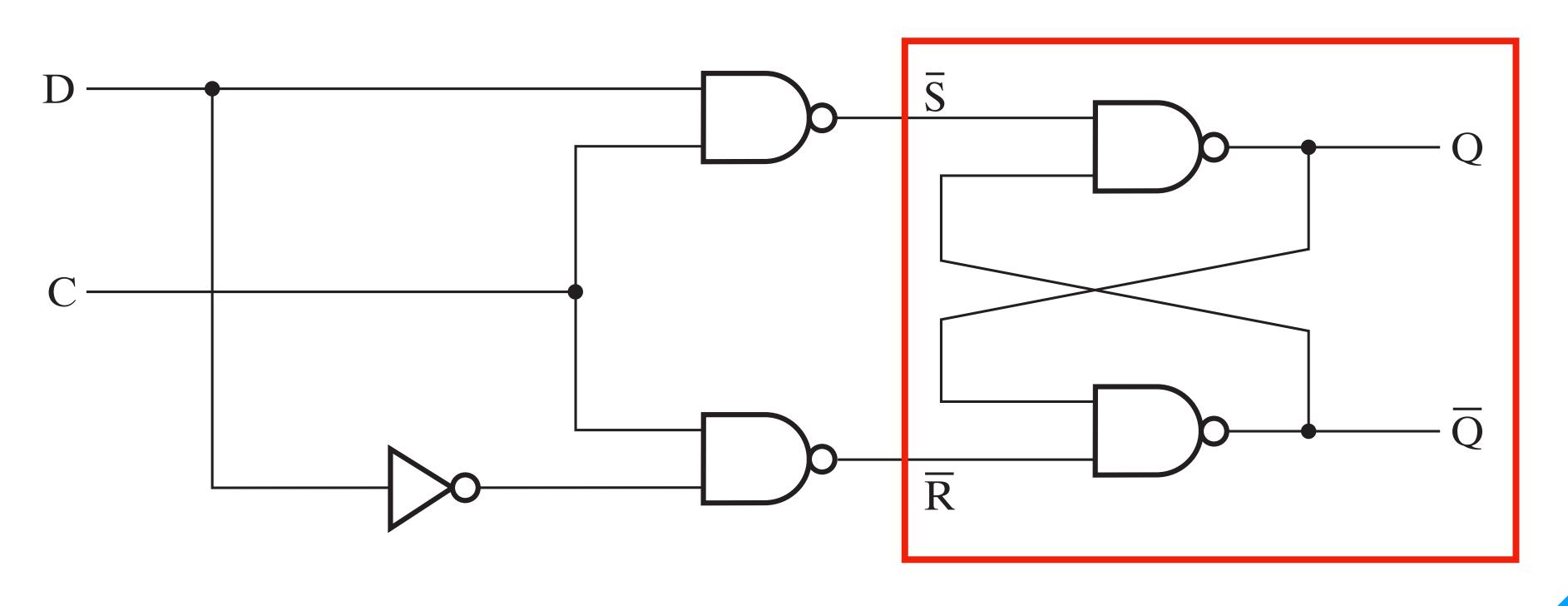

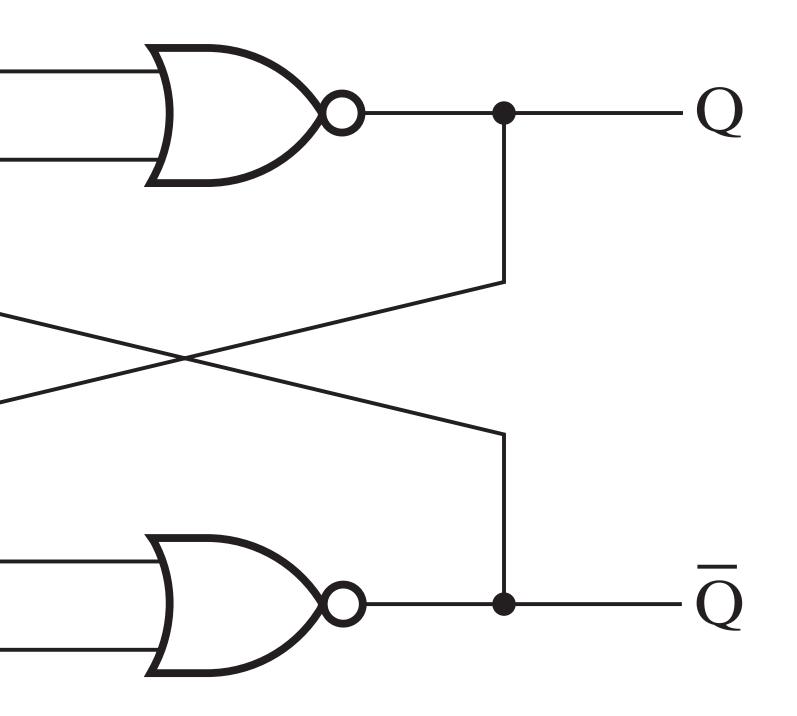

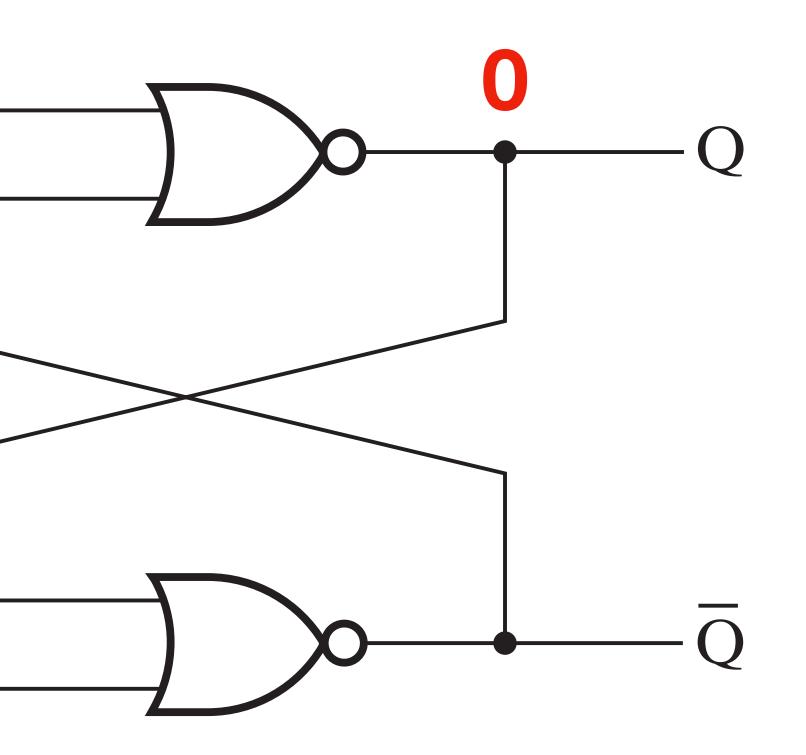

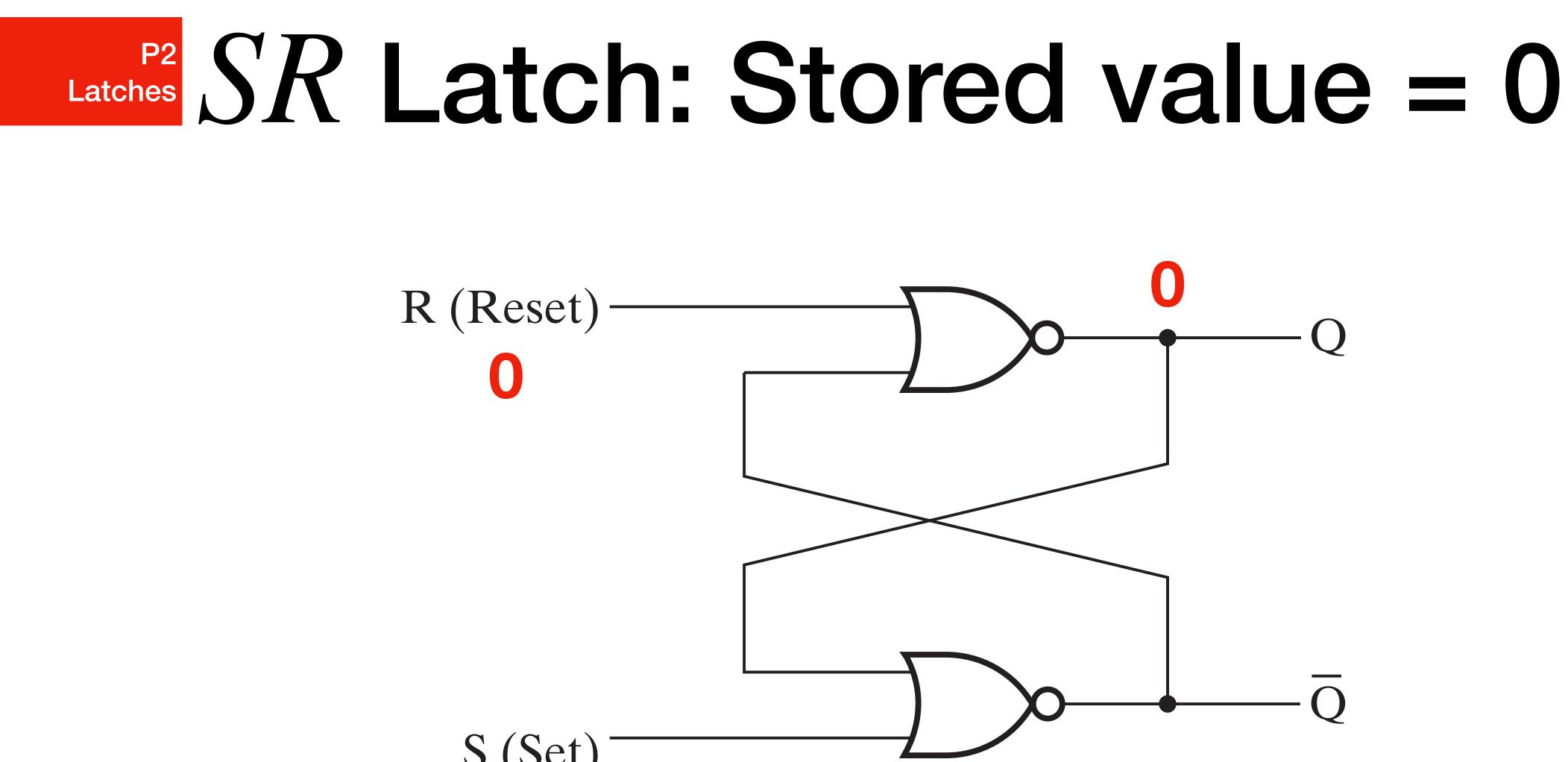

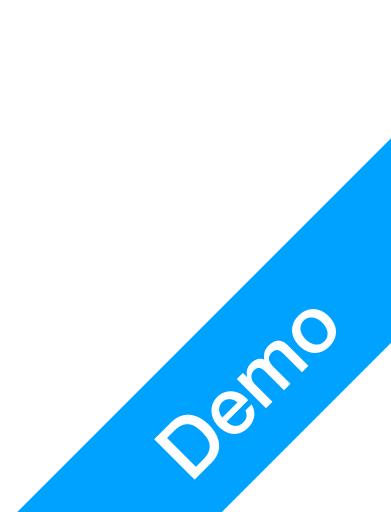

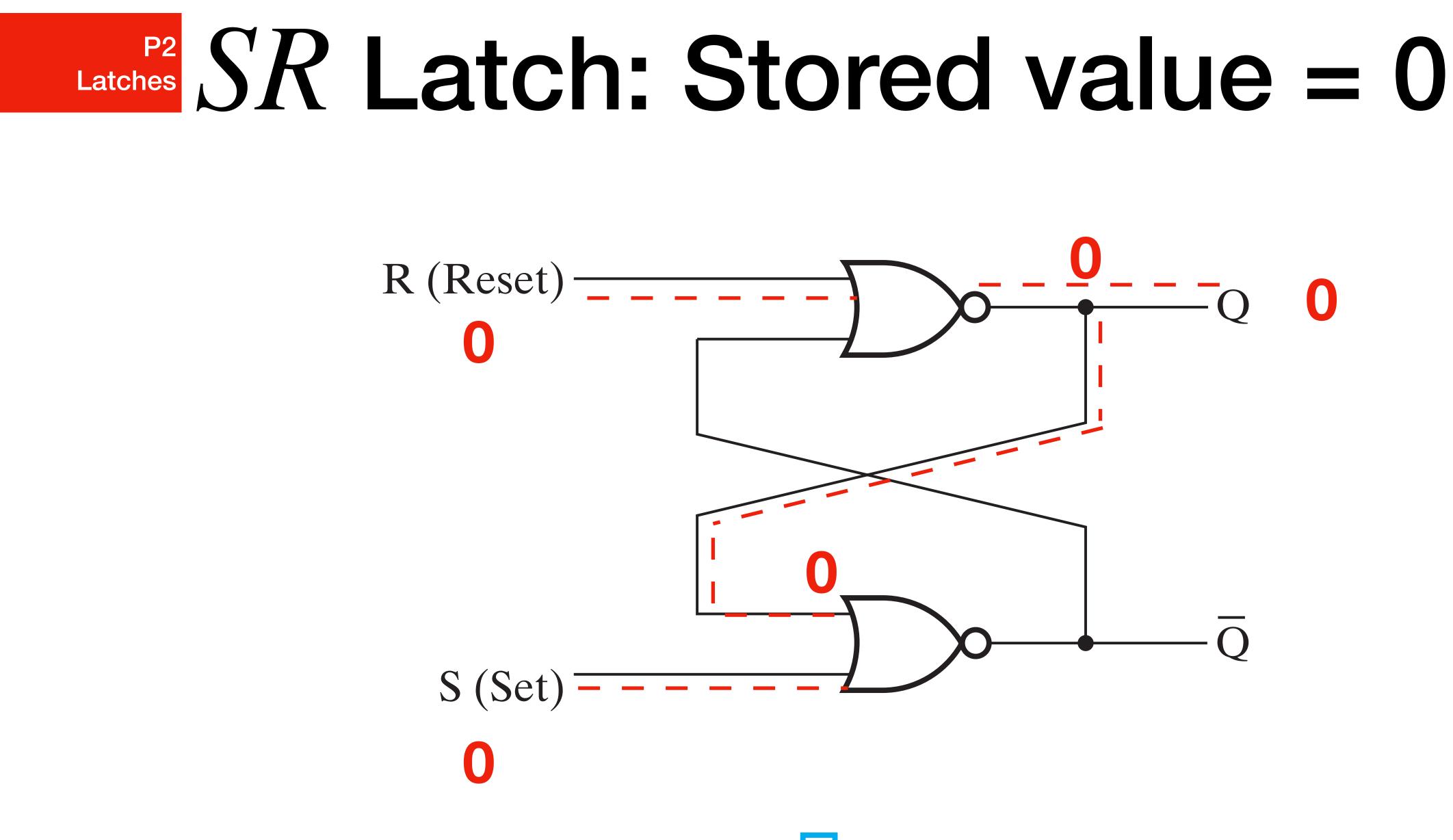

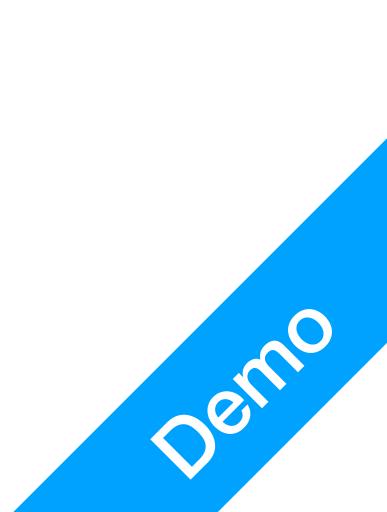

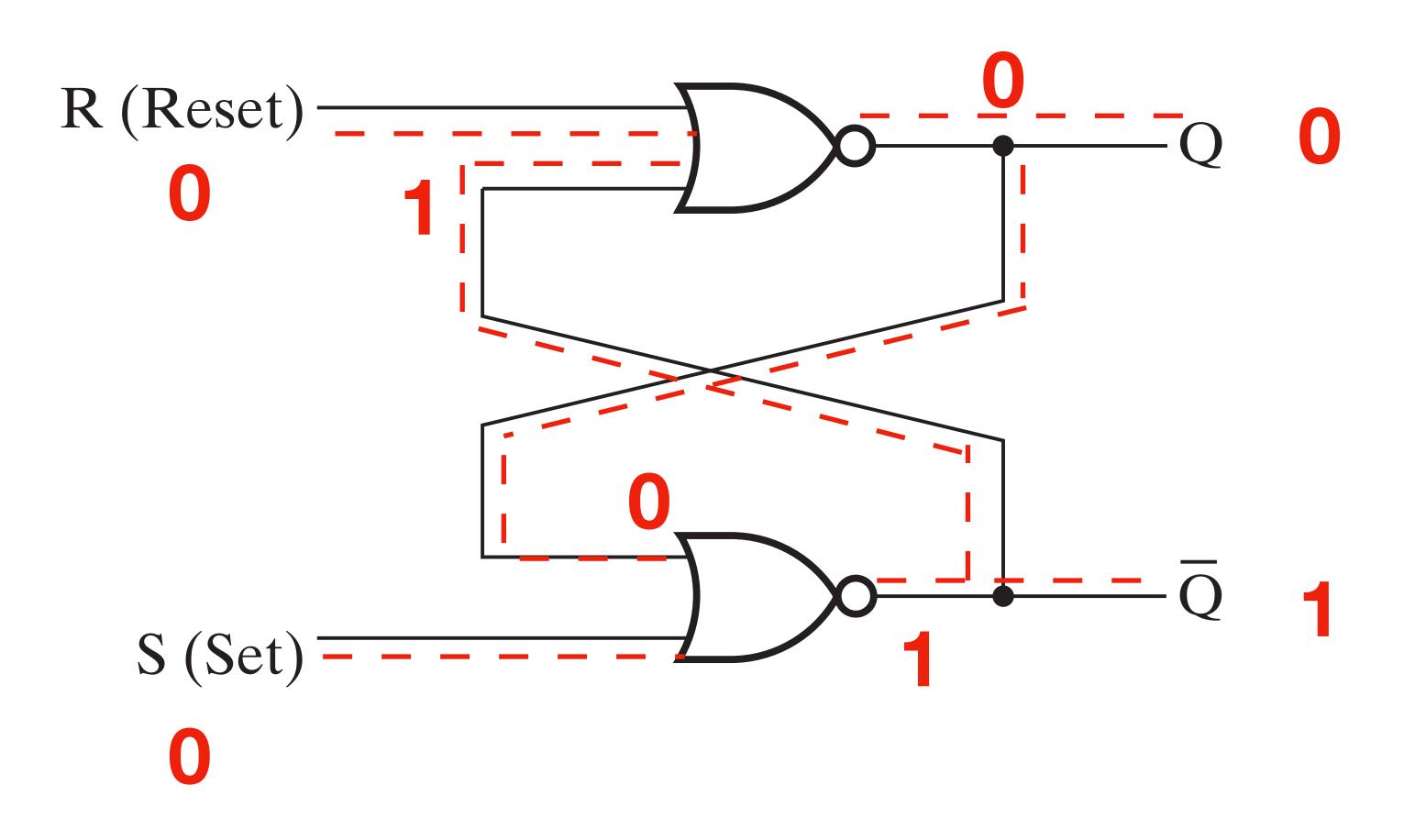

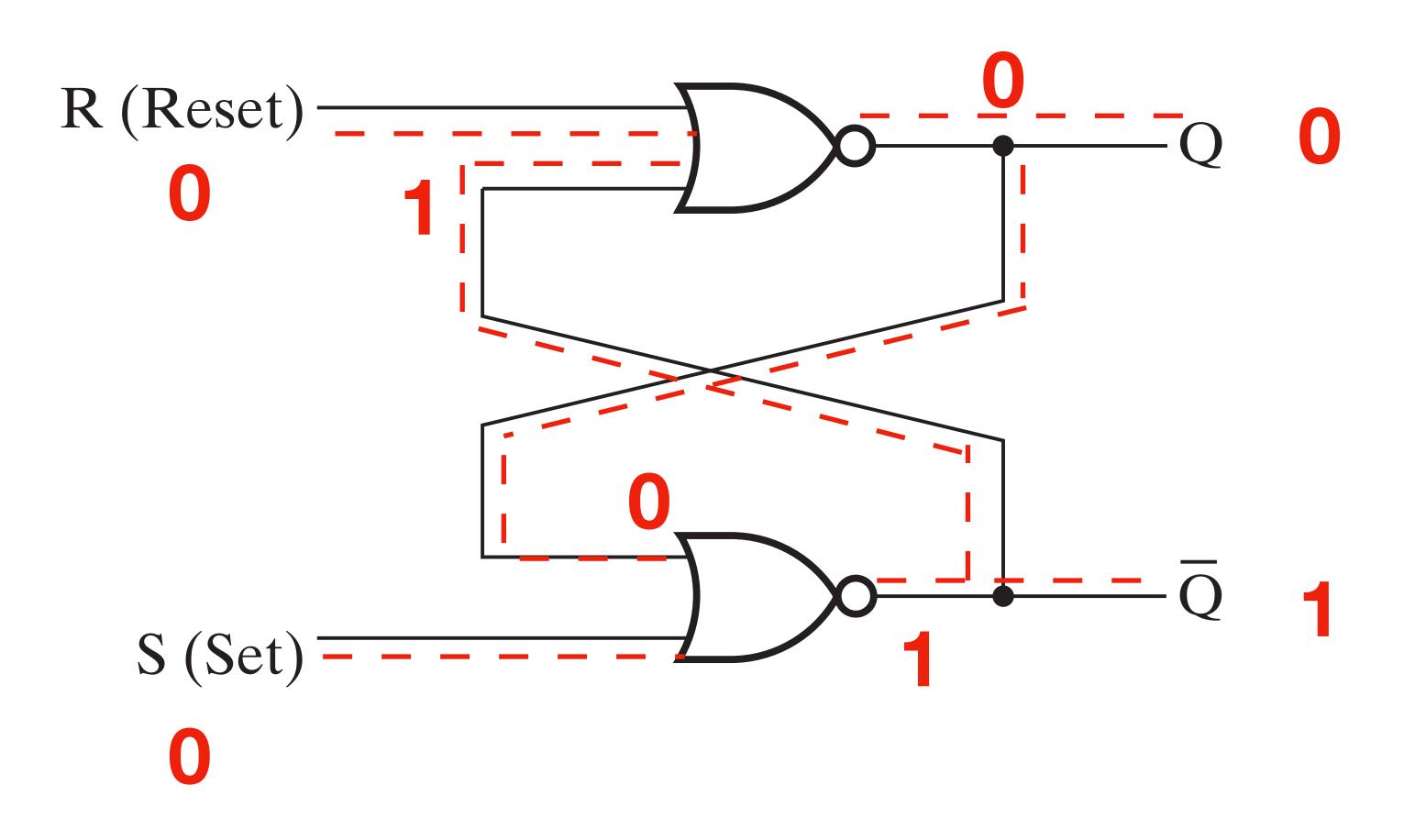

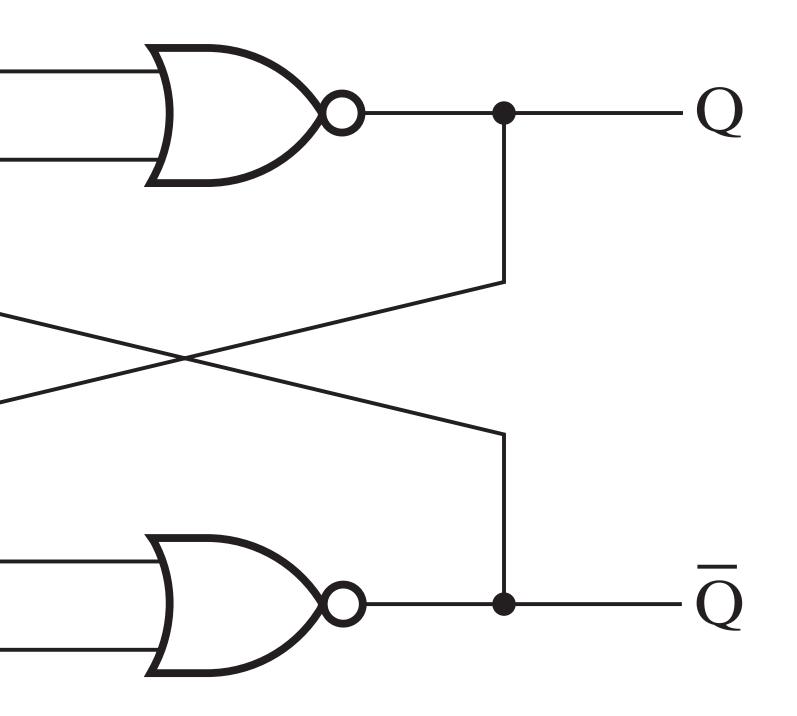

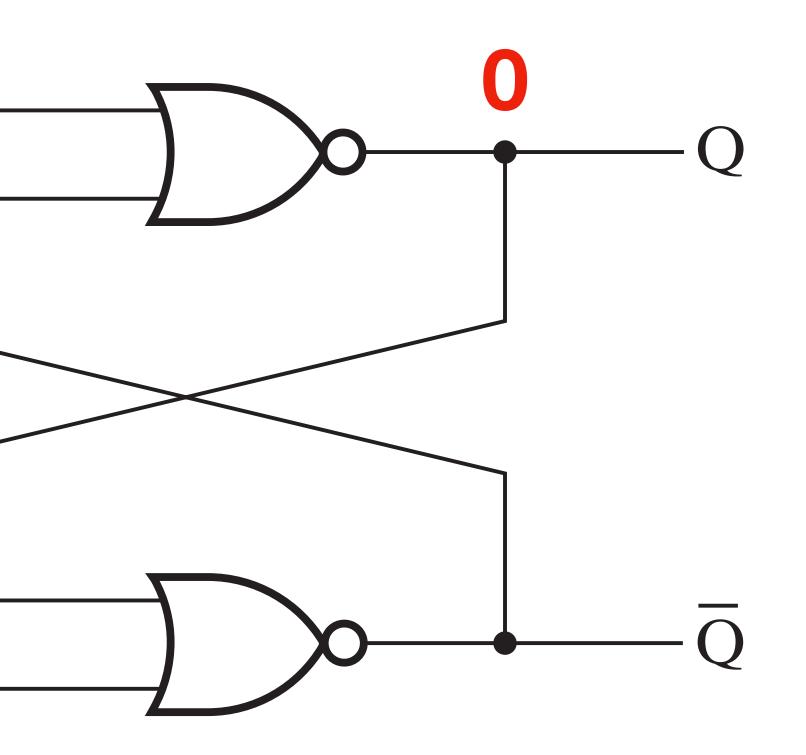

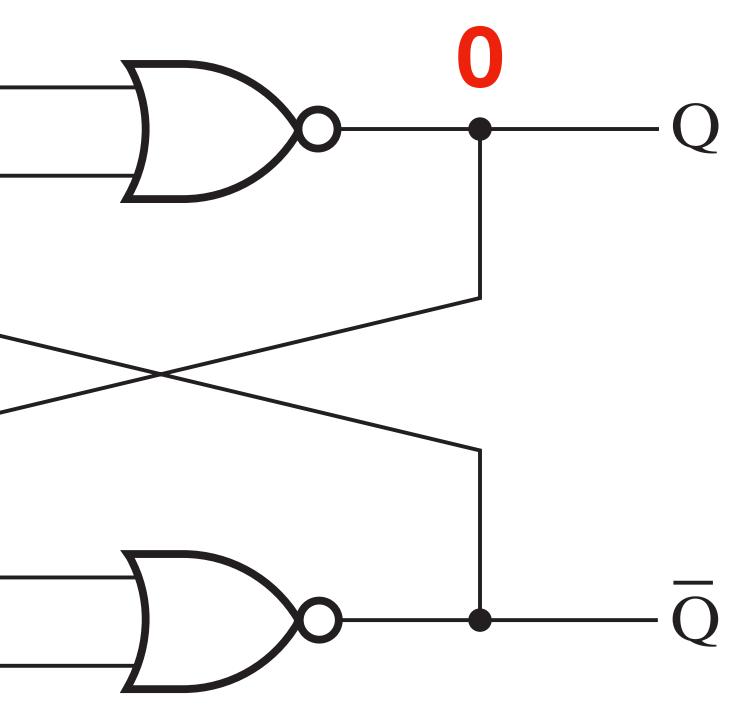

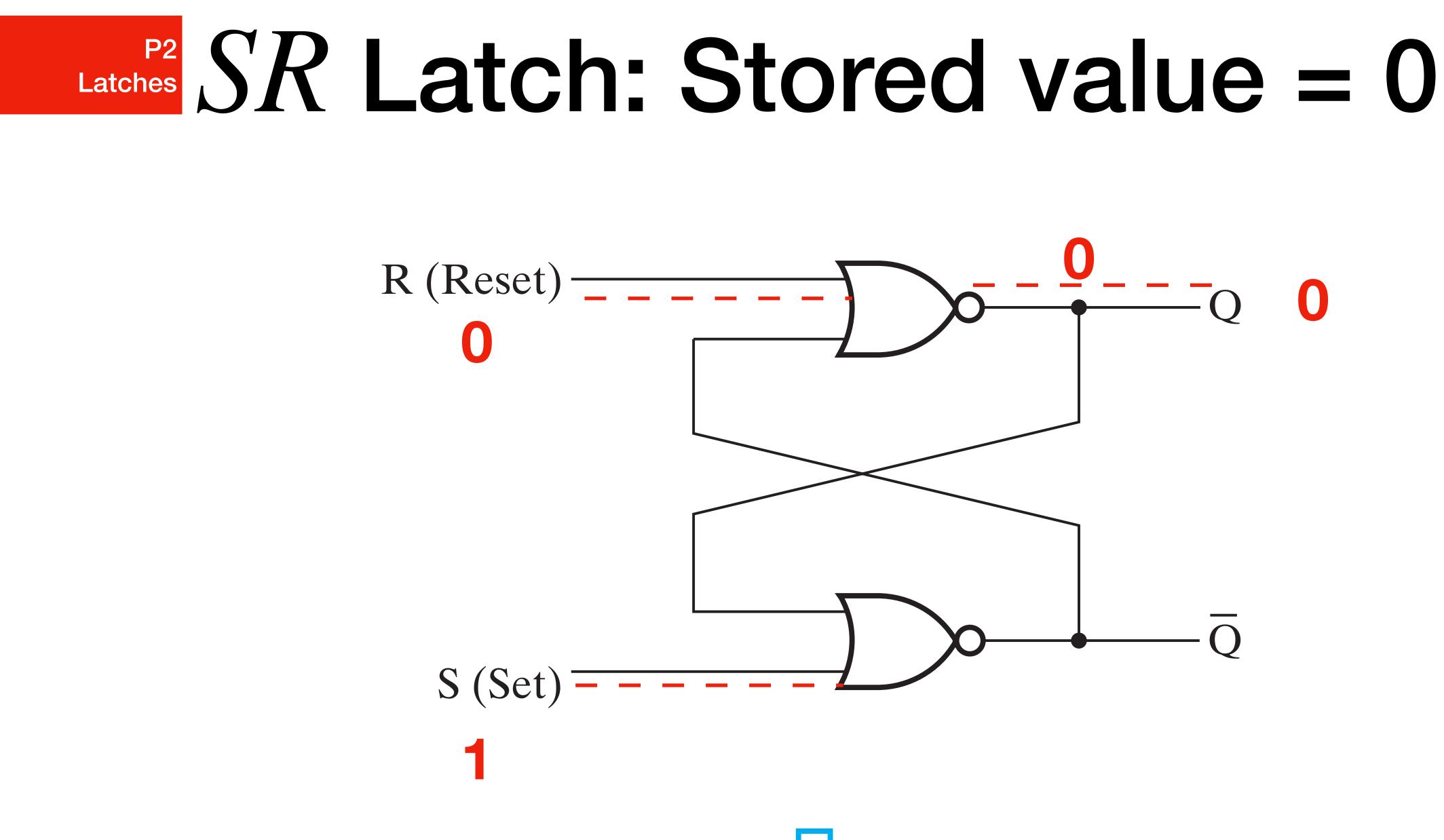

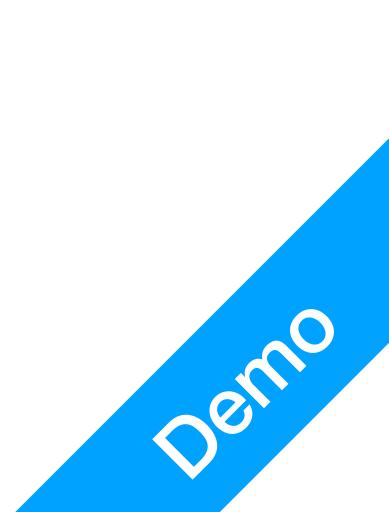

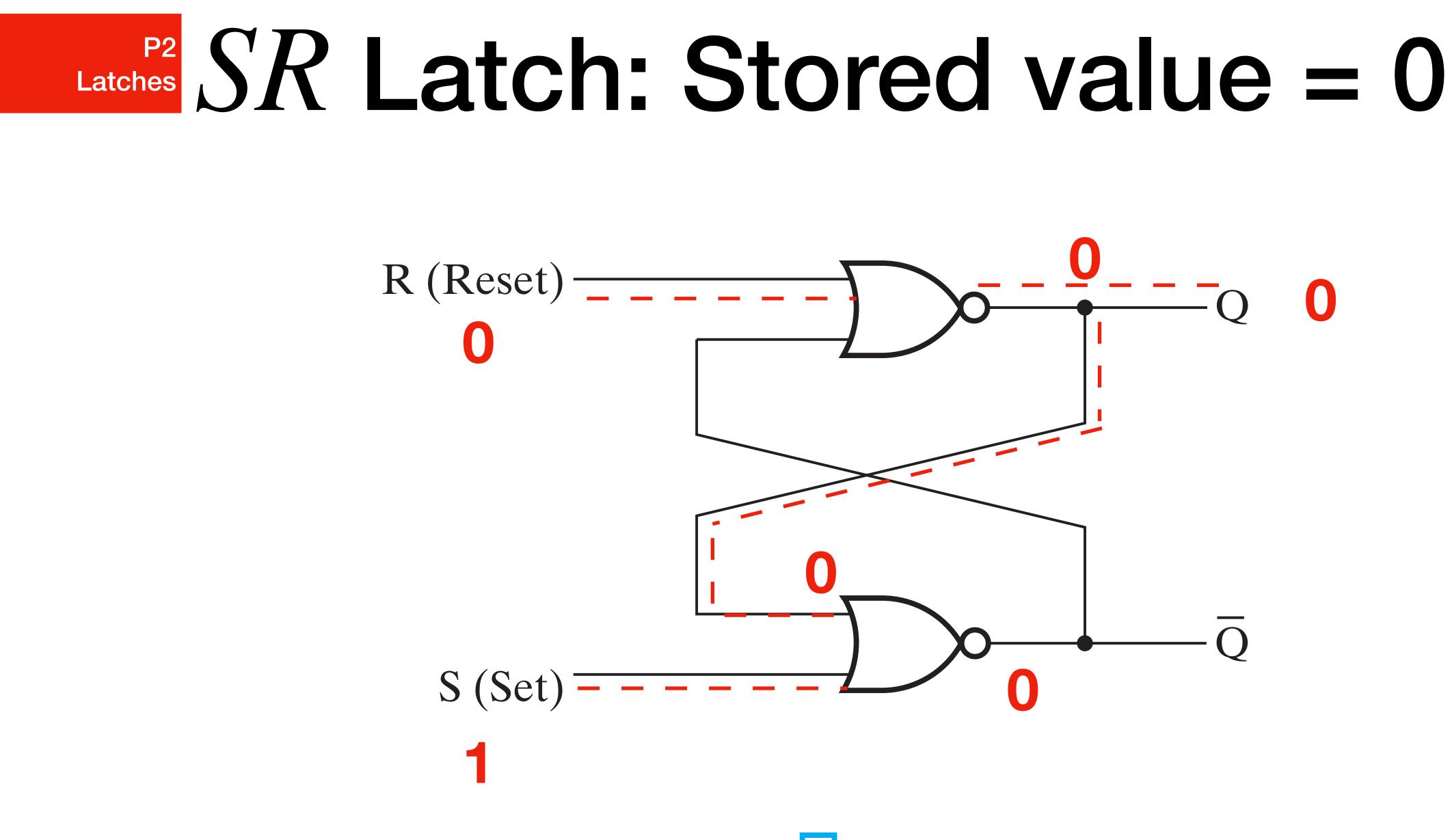

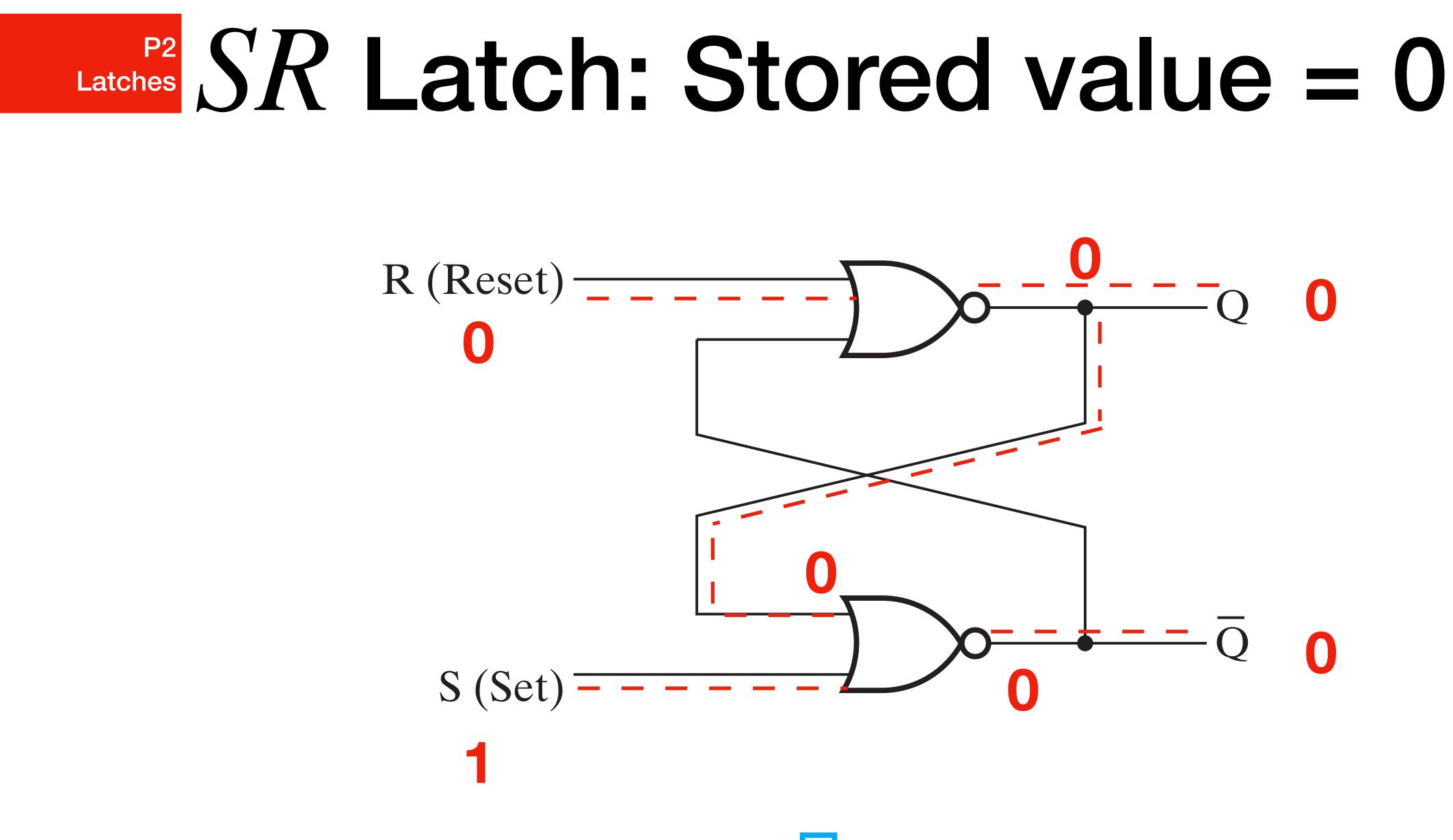

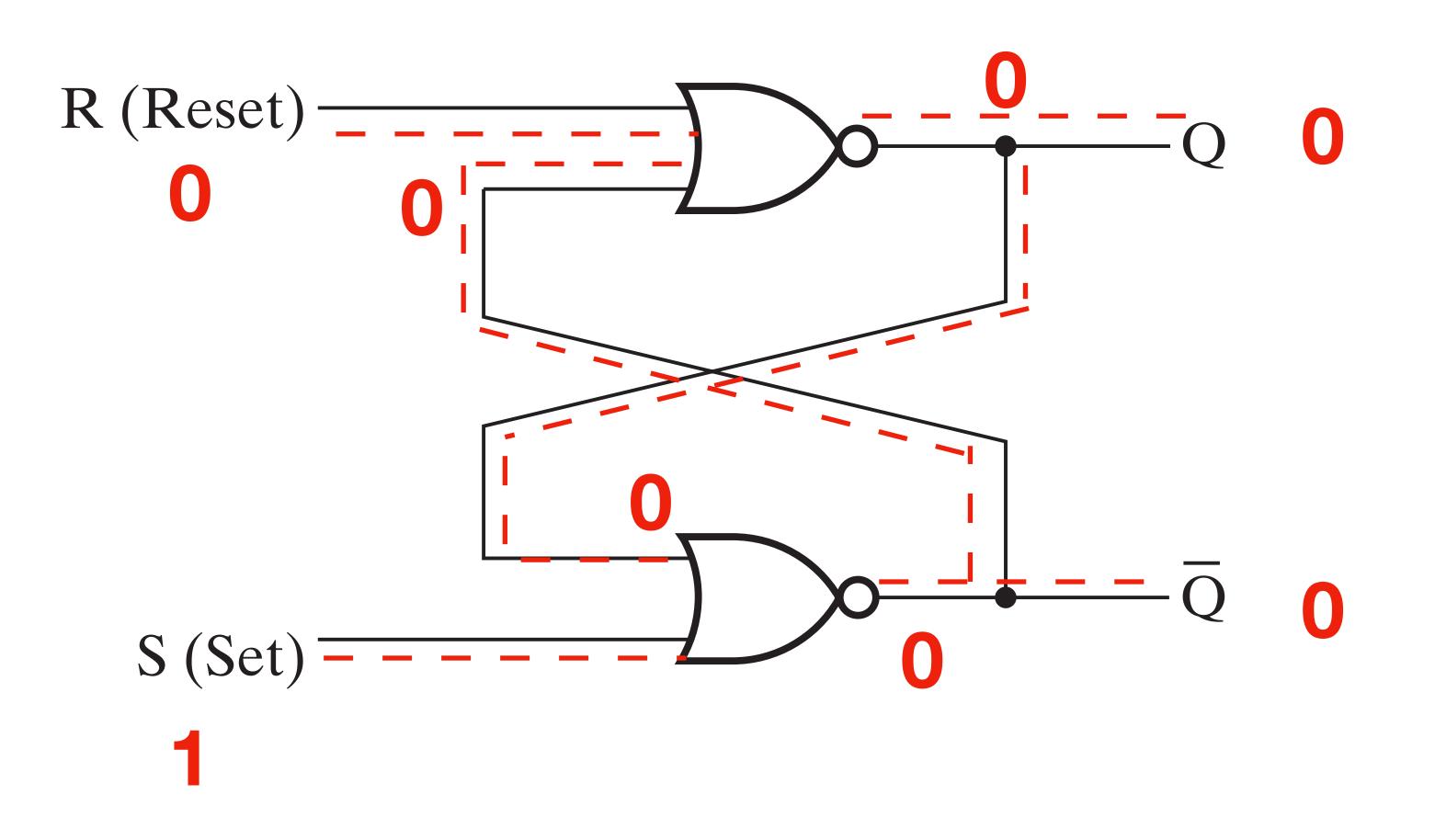

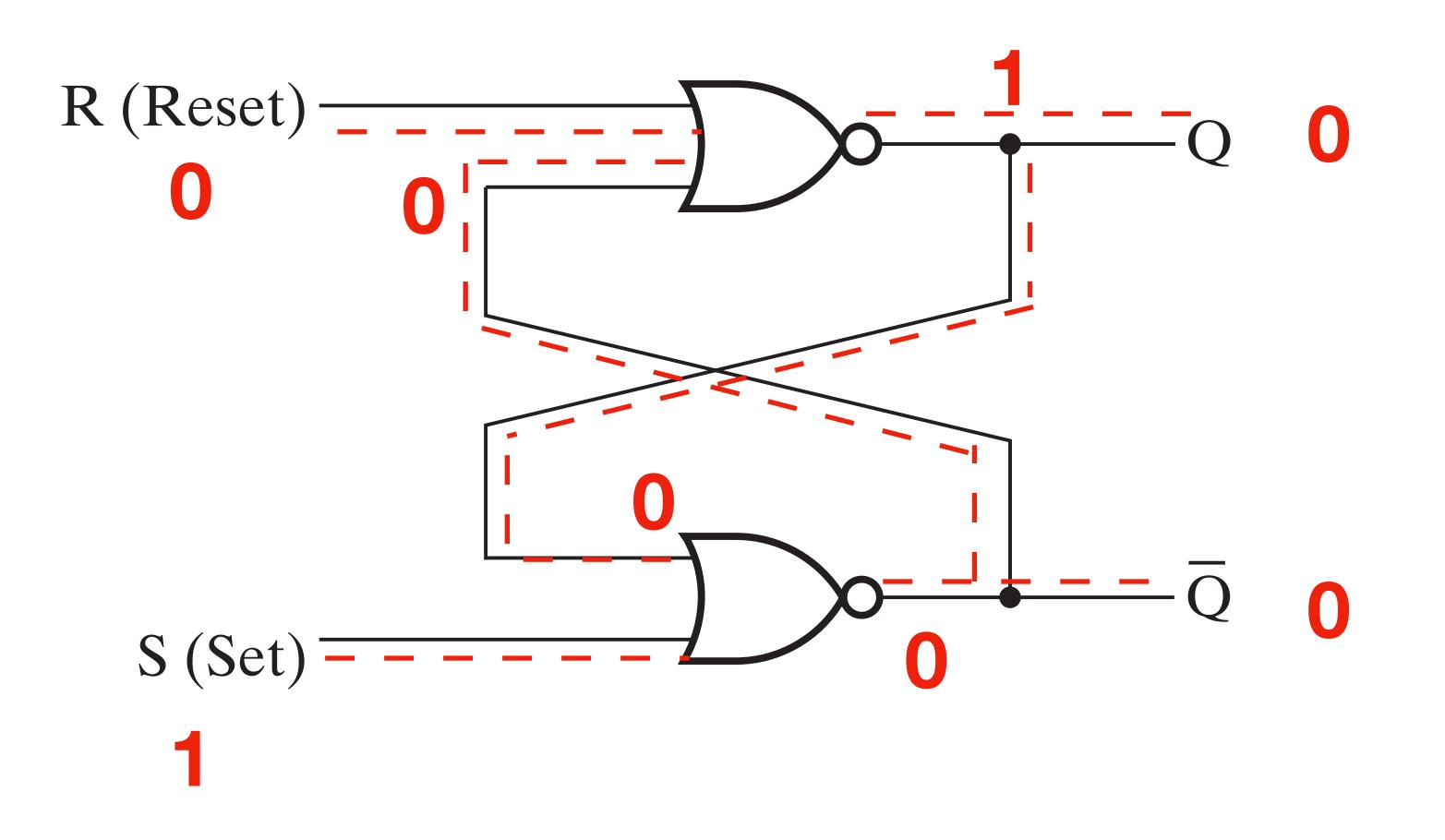

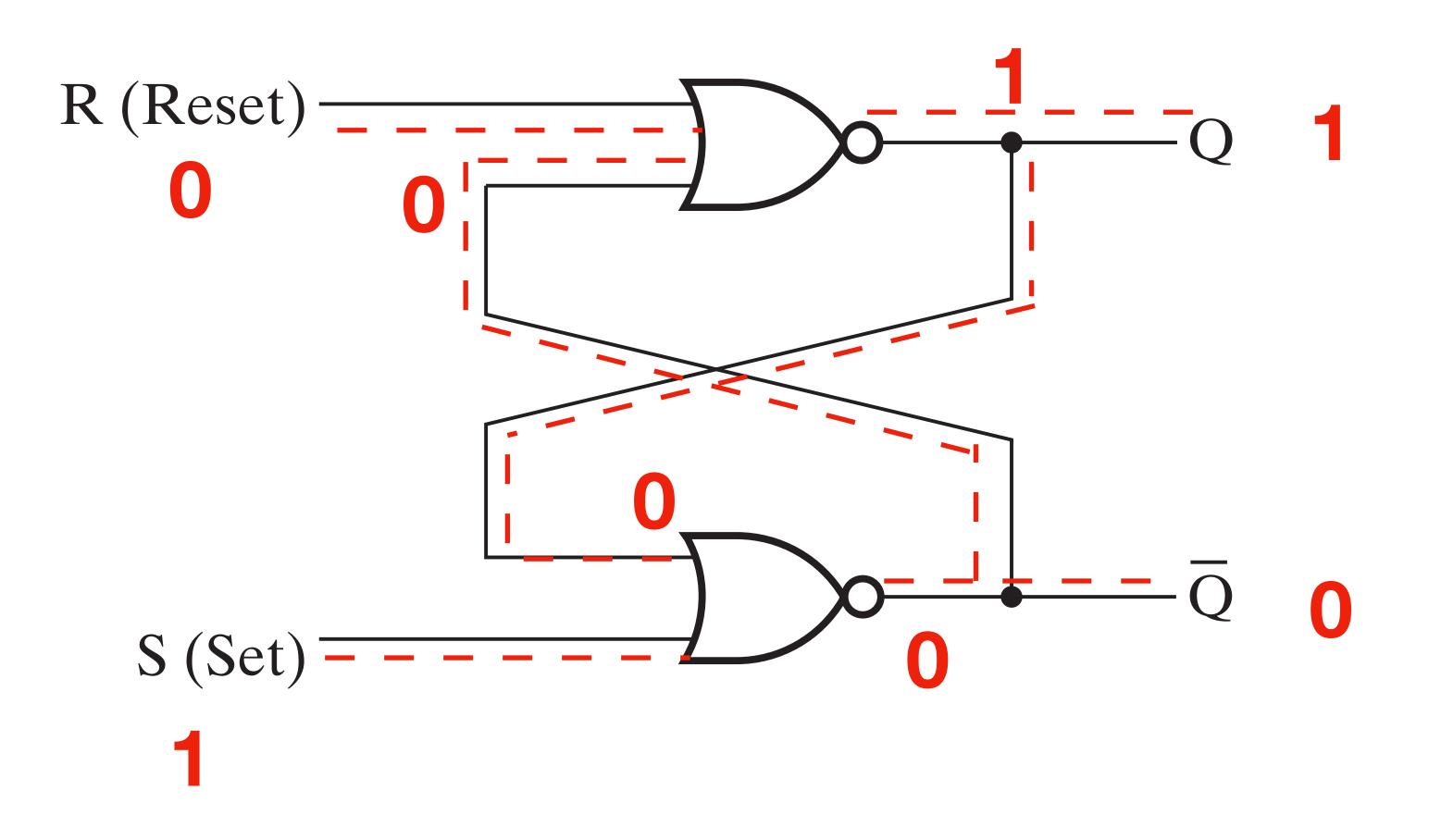

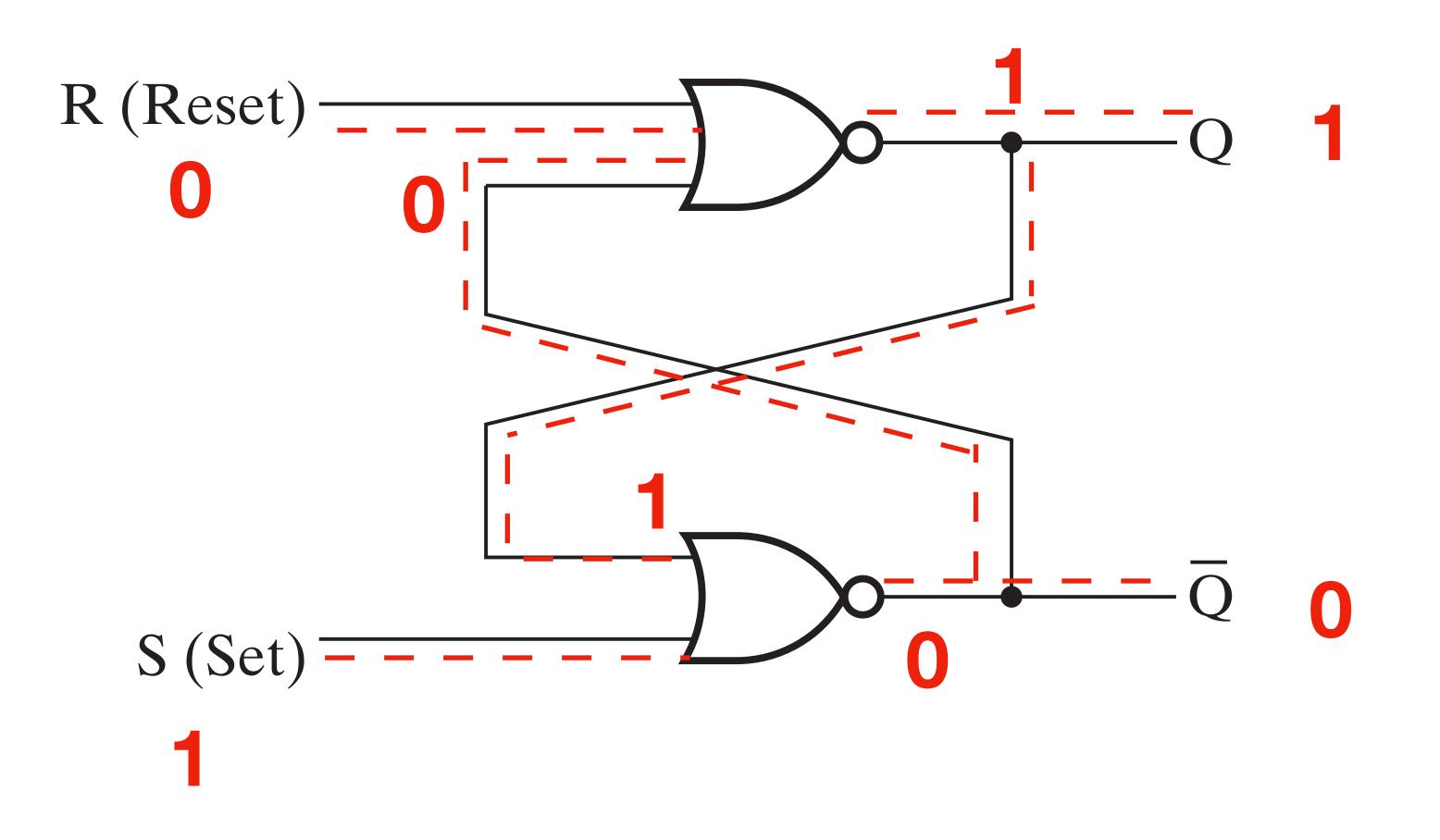

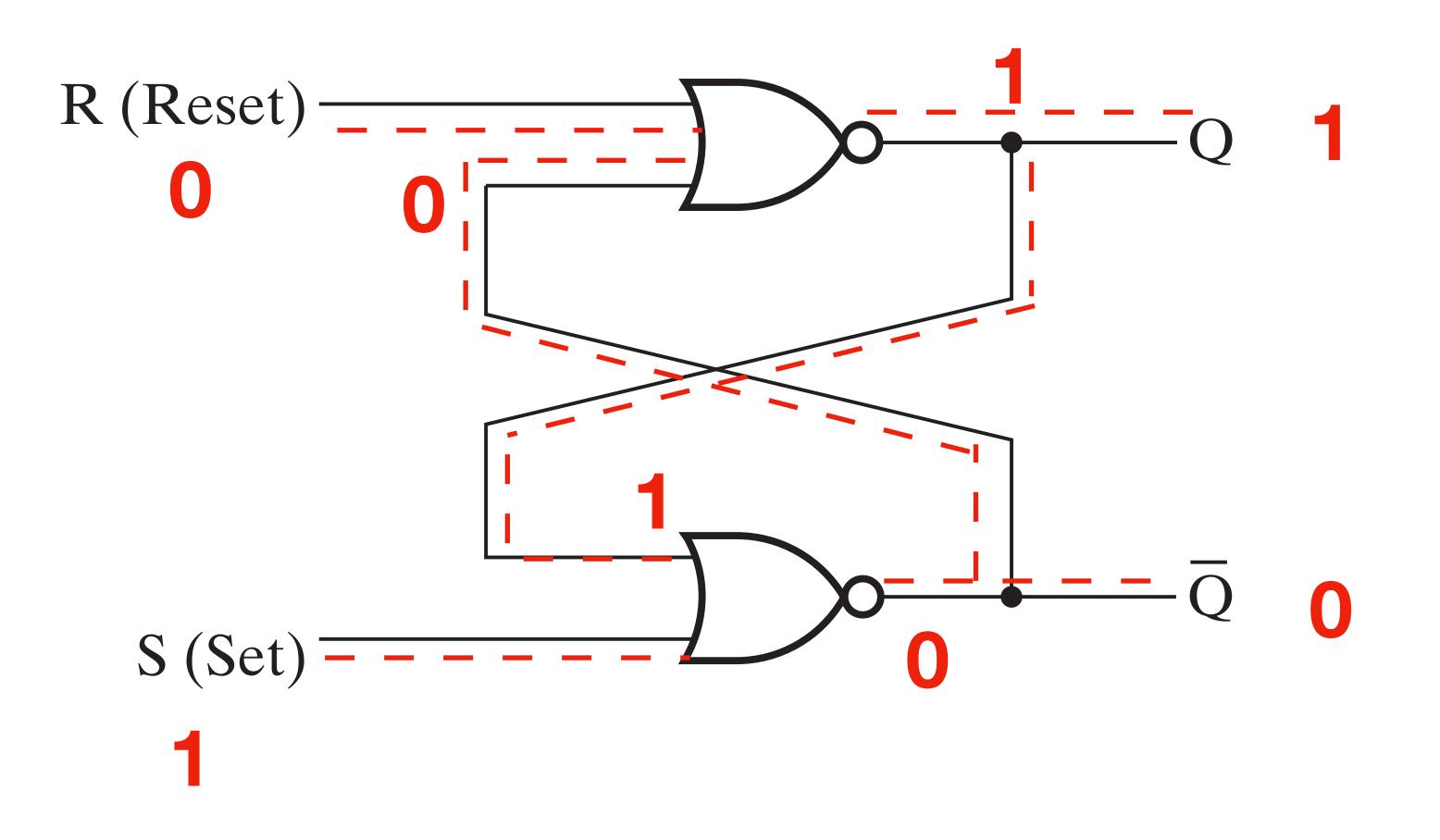

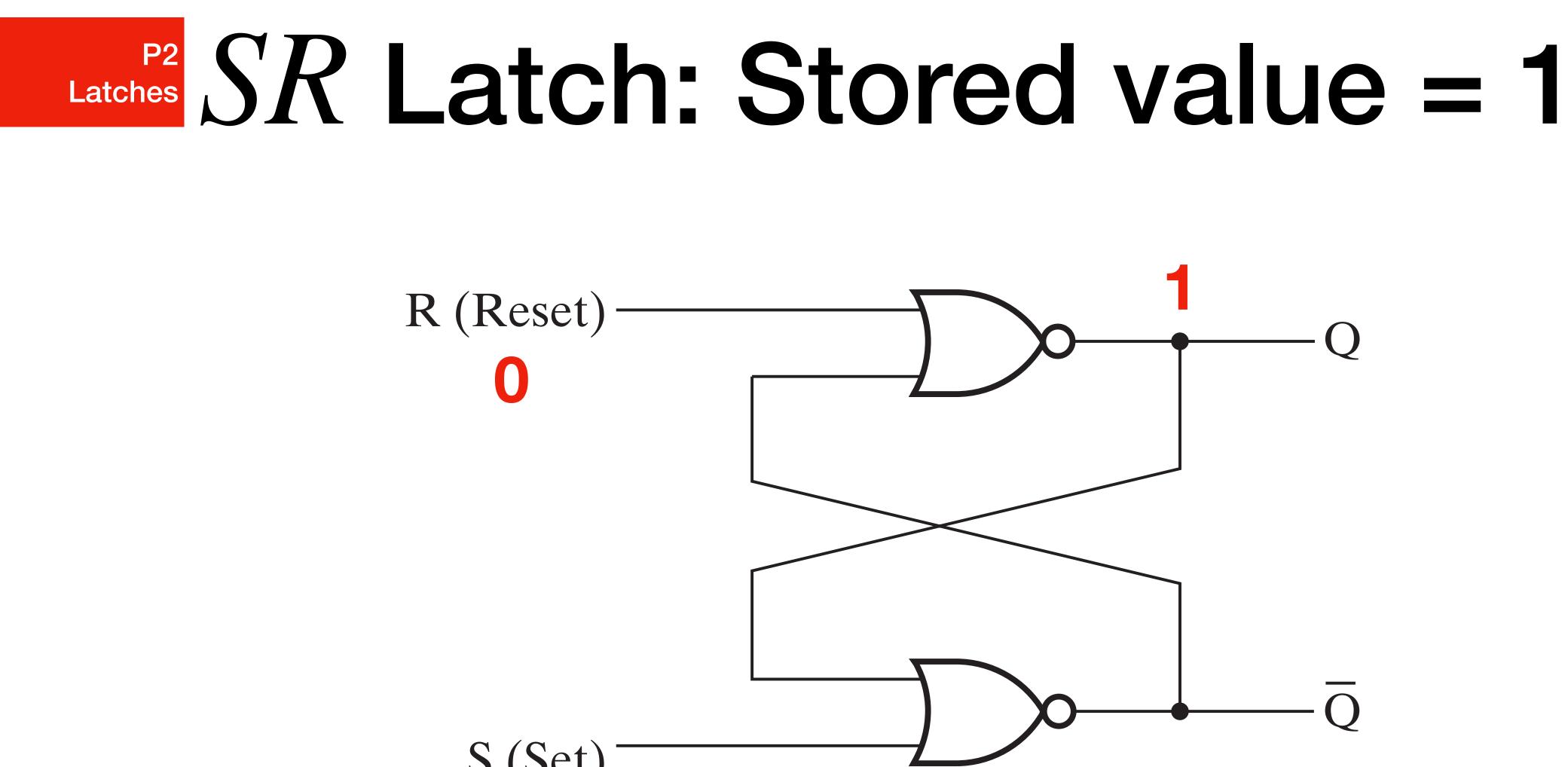

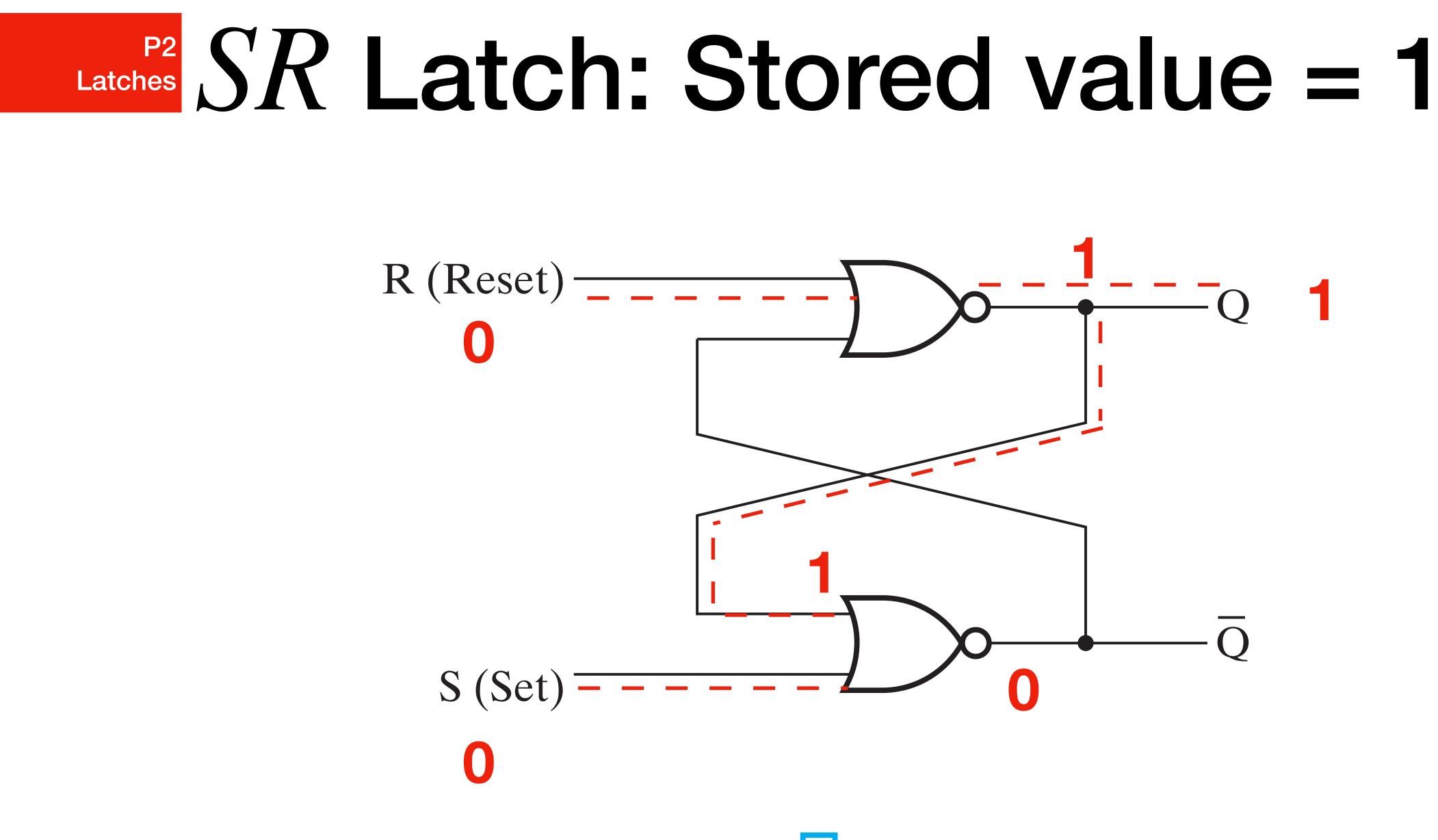

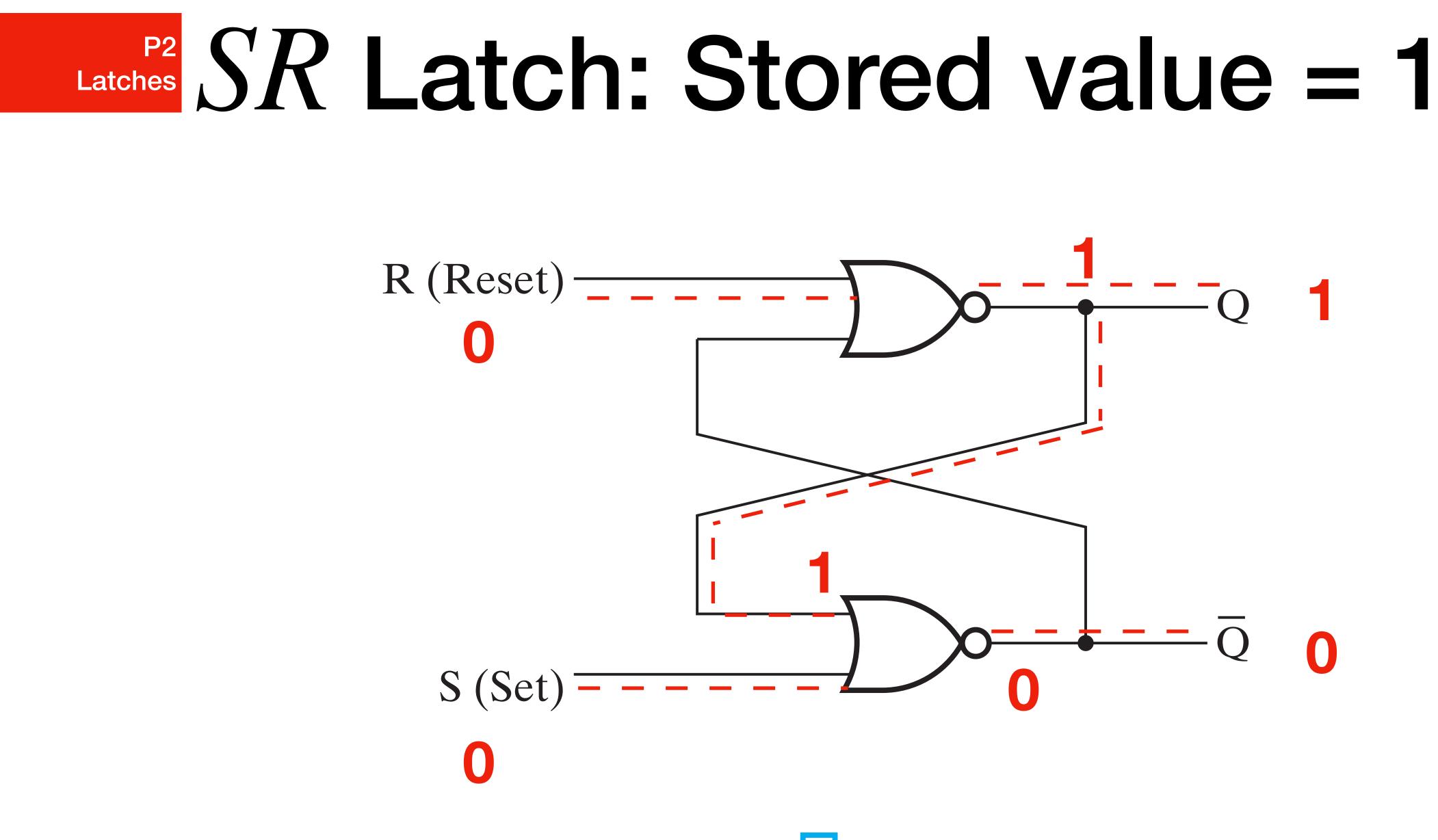

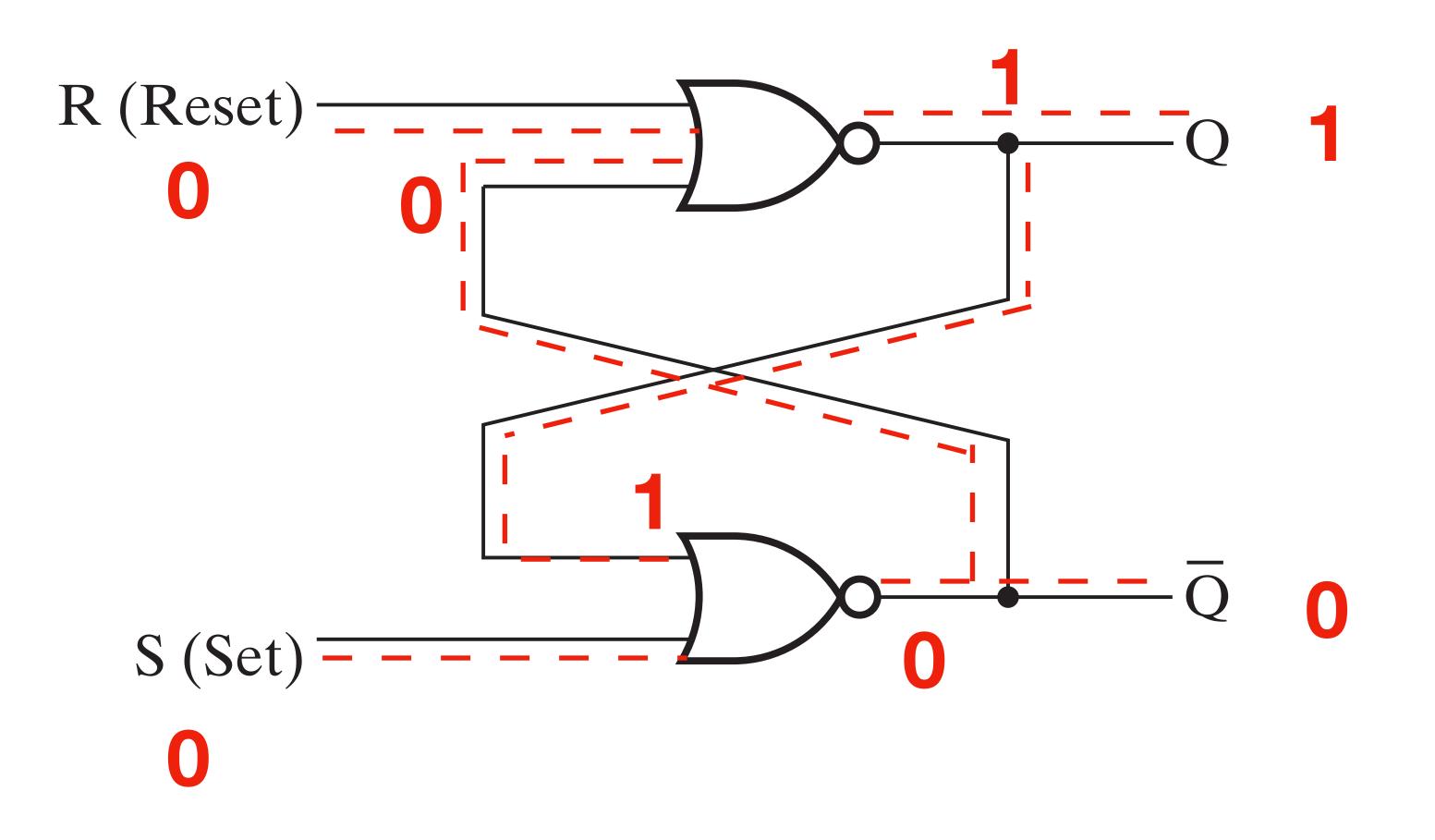

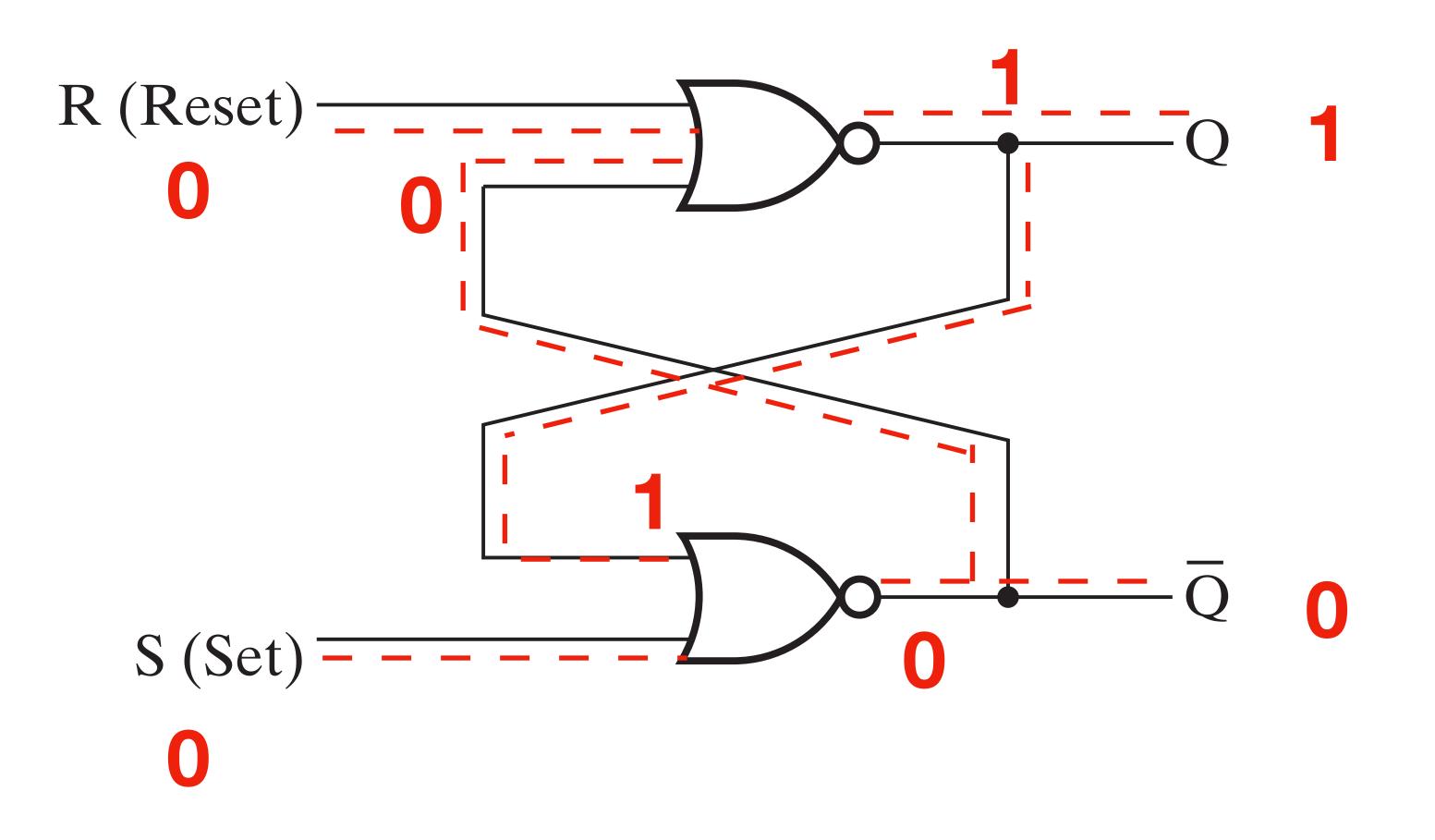

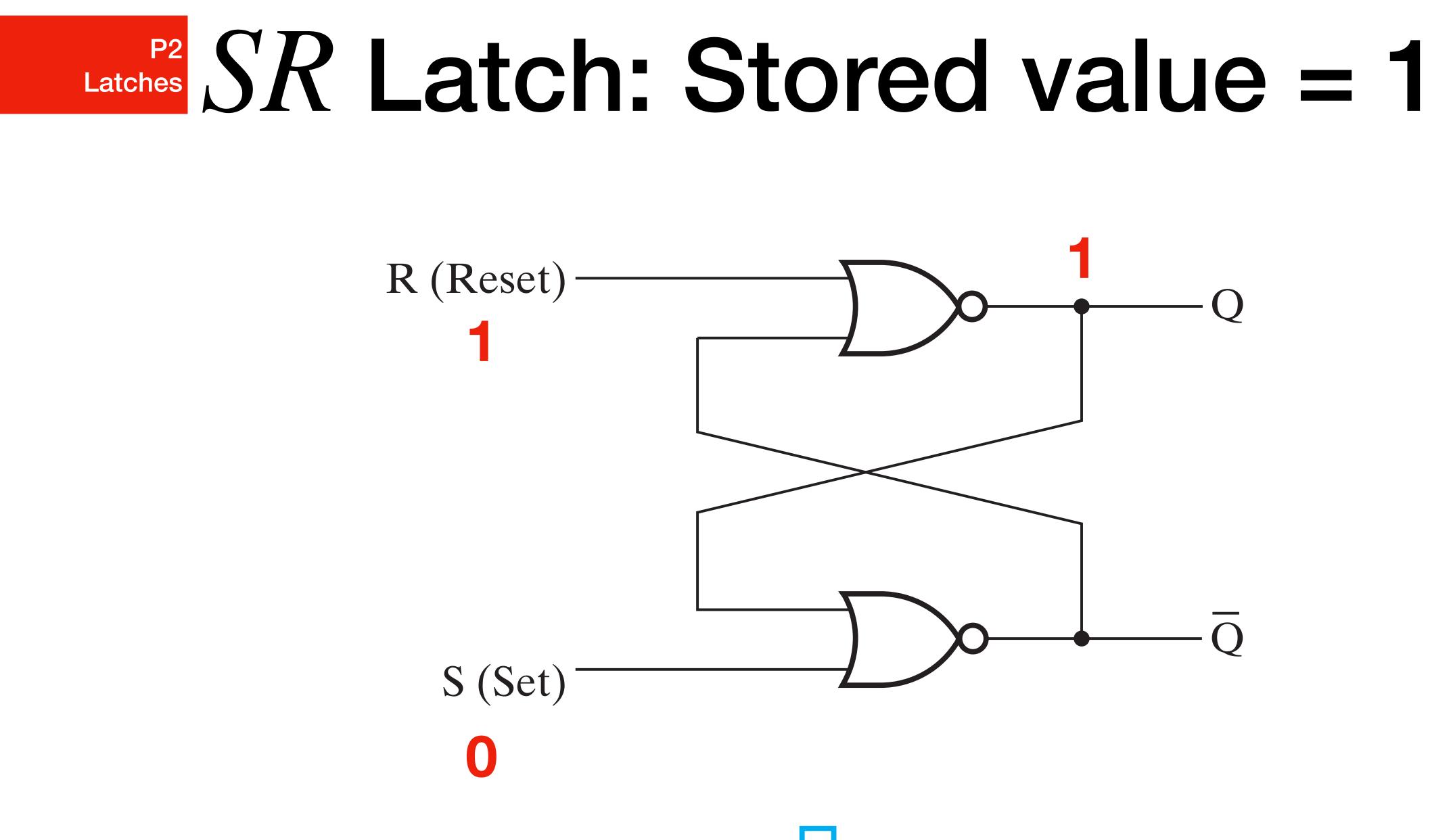

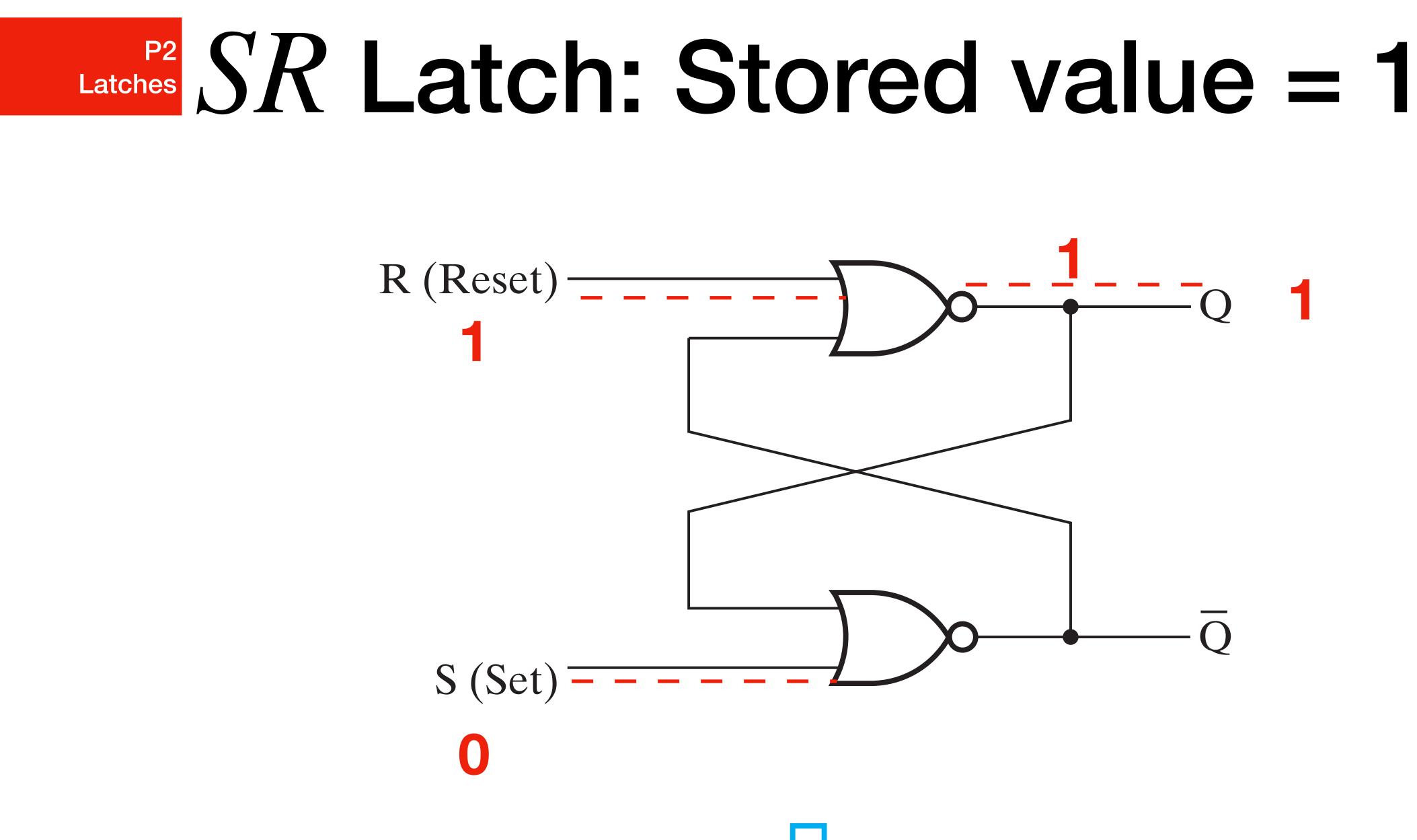

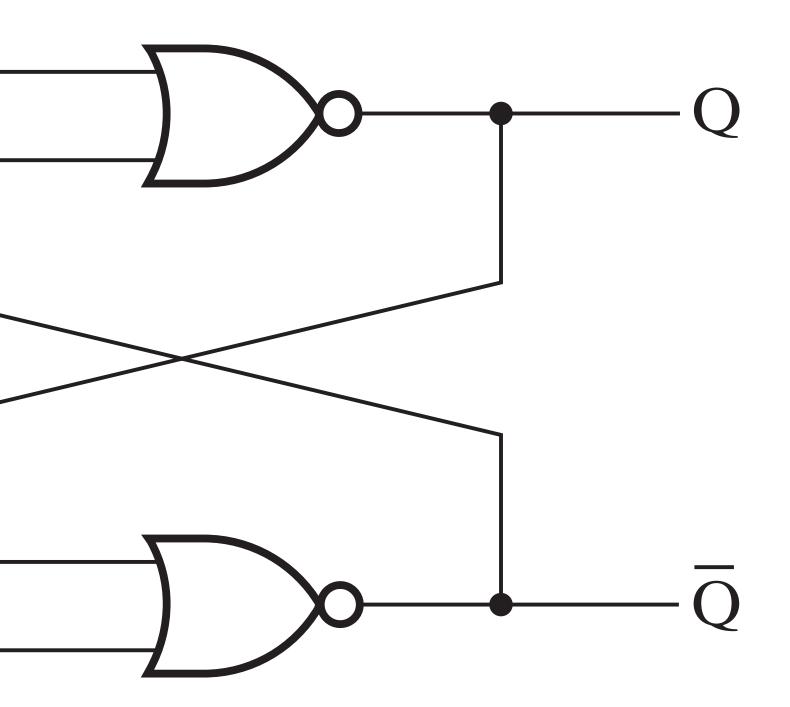

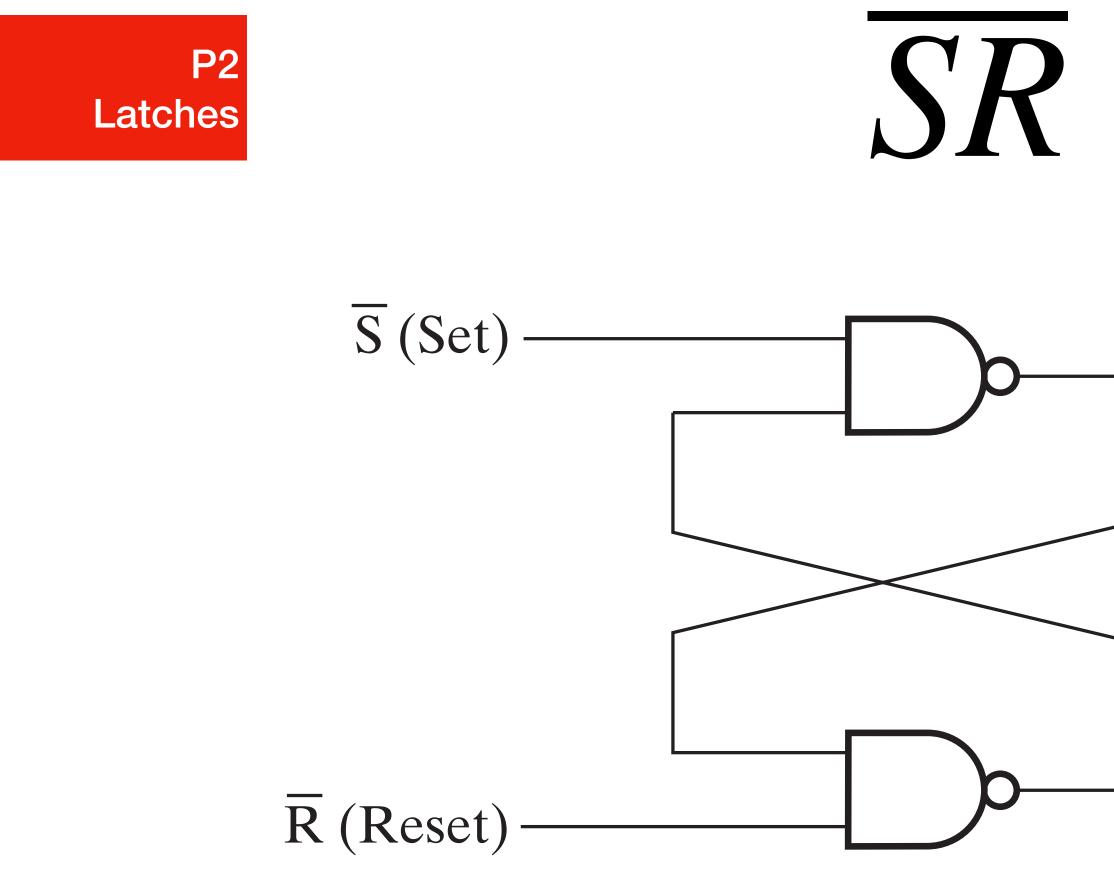

## • SR Latches and $\overline{SR}$ Latches

• *D* Latches

# Summary

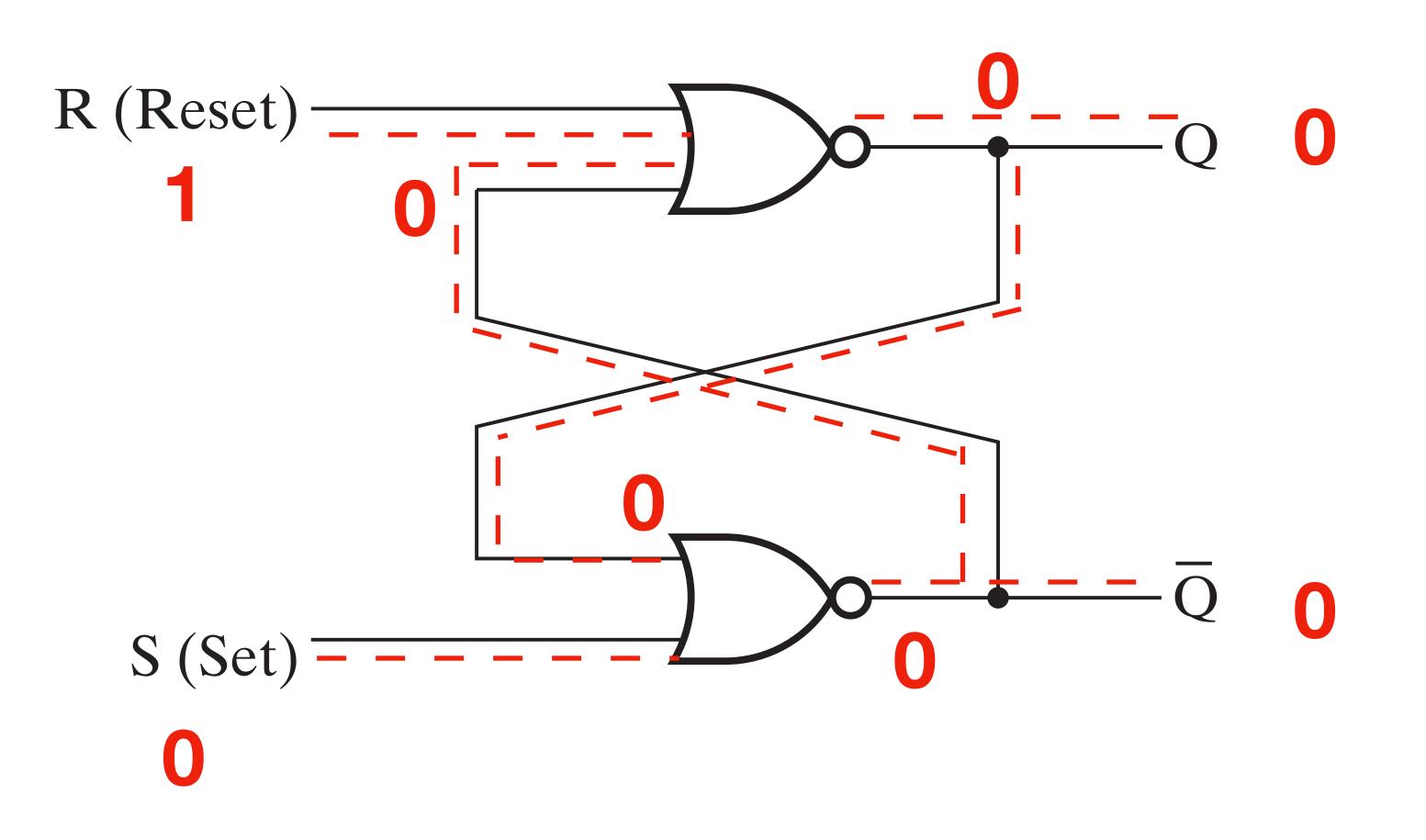

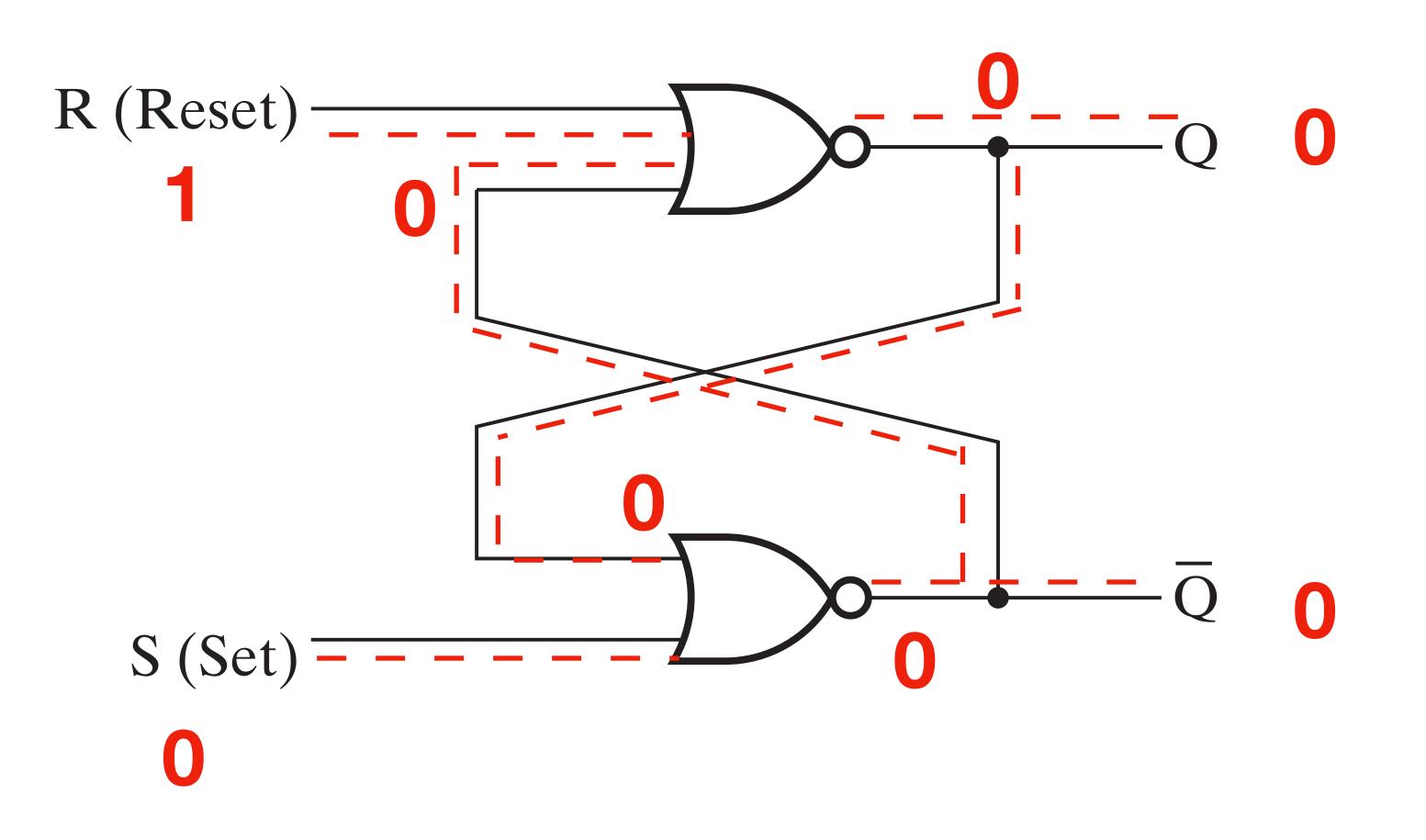

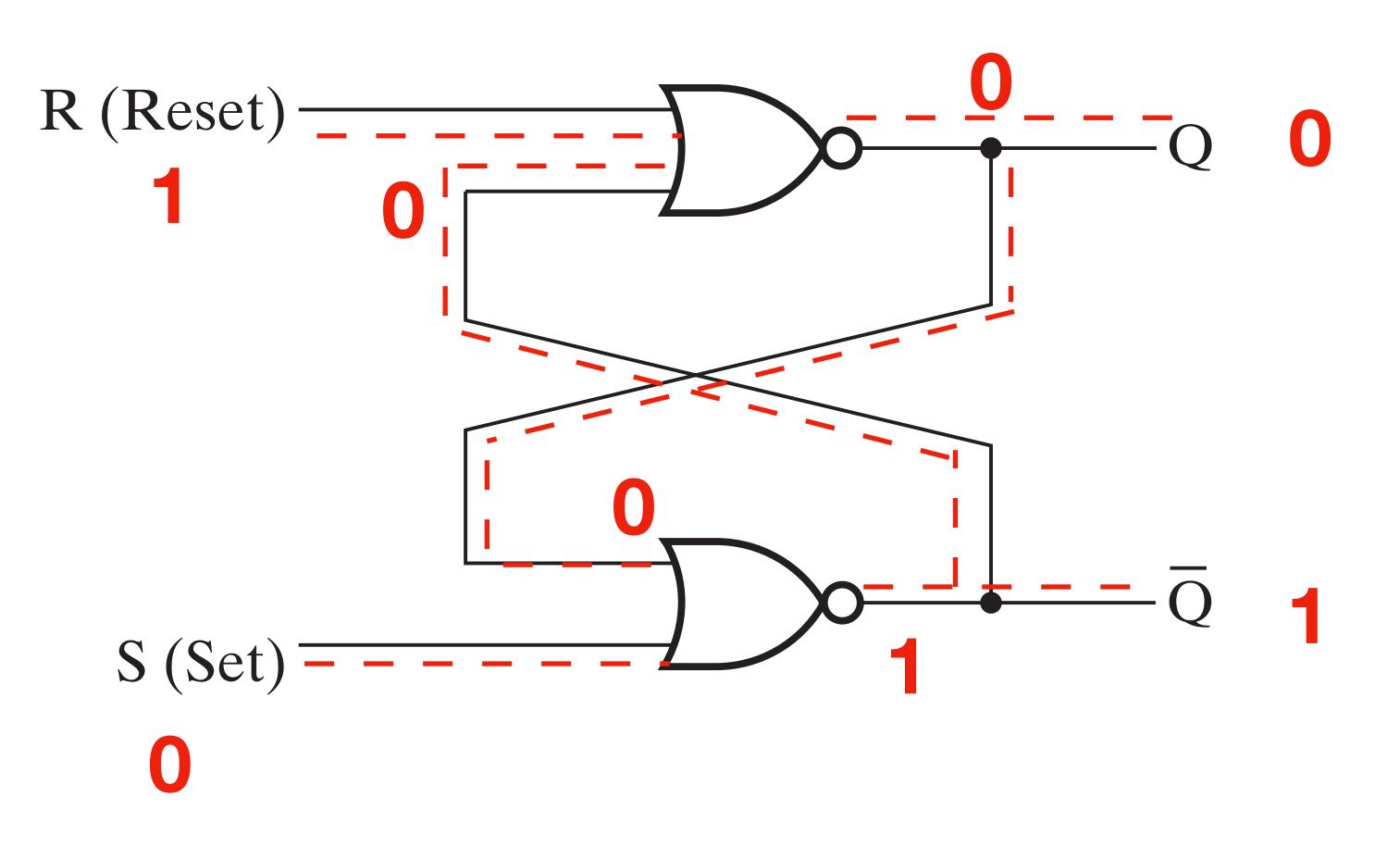

## R (Reset)

## R (Reset)

## S (Set) 0

## R (Reset)

## R (Reset)

## R (Reset) 0

S (Set)

## S (Set) 0

R (Reset)

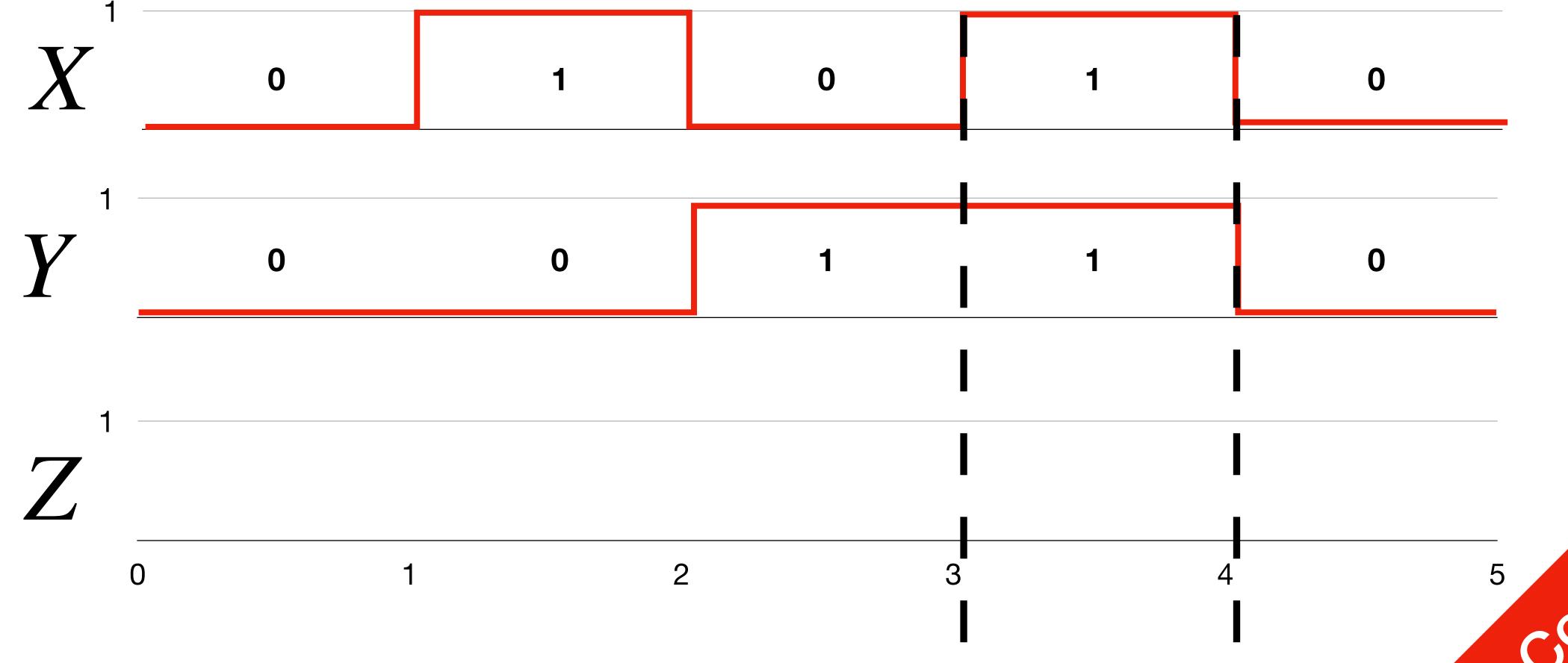

## Exercise

• Draw the SR Latch in LogicWorks as below, make sure it works as intended

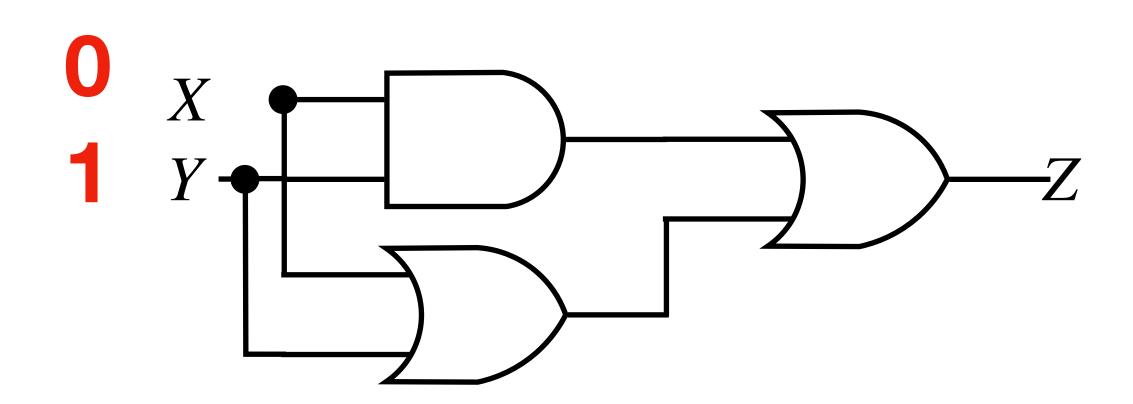

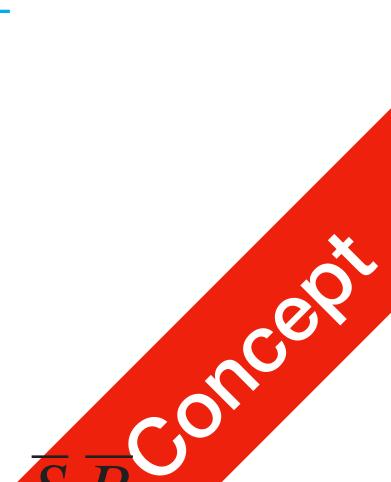

- Design similar to *SR* latches, but with NANDS

- Functions equivalent to  $S\overline{R}^{R}$  atches with S and R inverted

| Latch                   |                             |                                                 |             |  |

|-------------------------|-----------------------------|-------------------------------------------------|-------------|--|

|                         | $\overline{S} \overline{R}$ | QQ                                              |             |  |

| Q                       | 0 1<br>1 1                  | $\begin{array}{ccc} 1 & 0 \\ 1 & 0 \end{array}$ | Set state   |  |

|                         | 1 0<br>1 1                  | 0 1<br>0 1                                      | Reset state |  |

| $\overline{\mathbf{Q}}$ | 0 0                         | 1 1                                             | Undefined   |  |

- Implemented using  $\overline{SR}$  latches

- C: Signals changes to the stored states; D the value to change to S R

| С      | D      | Next state of C                          |

|--------|--------|------------------------------------------|

| 0<br>1 | X<br>0 | No change<br>Q = 0; Reset s <sup>2</sup> |

| 1      | 1      | Q = 1; Set stat                          |

## Latches

- Implement  $\overline{SR}$  latch, save as a component in your library

- Implement D latch, save as a component in your library