# CSCI 150 Introduction to Digital and Computer System Design Midterm Review II

Jetic Gū 2020 Fall Semester (S3)

#### Overview

- Focus: Review

- Architecture: Combinational Logic Circuit

- Textbook v4: Ch1-4; v5: Ch1-3

- Core Ideas:

- 1. Digital Information Representation (Lecture 1)

- 2. Combinational Logic Circuits (Lecture 2)

- 3. Combinational Functional Blocks, Arithmetic Blocks (Lecture 3)

# Lecture 3: Combinational Logic Design

5 Steps Systematic Design Procedures; Functional Blocks; Decoder, Enabler, Multiplexer; Arithmetic Blocks

#### Systematic Design Procedures

- **Specification**: Write a specification for the circuit

- 2. **Formulation**: Derive relationship between inputs and outputs of the system e.g. using truth table or Boolean expressions

- 3. **Optimisation**: Apply optimisation, minimise the number of logic gates and literals required

- 4. **Technology Mapping**: Transform design to new diagram using available implementation technology

- 5. Verification: Verify the correctness of the final design in meeting the specifications

### Hierarchical Design

- "divide-and-conquer"

- Circuit is broken up into individual functional pieces (blocks)

- Each block has explicitly defined Interface (I/O) and Behaviour

- A single block can be reused multiple times to simplify design process

- If a single block is too complex, it can be further divided into smaller blocks, to allow for easier designs

Cervi

# Value-Fixing, Transferring, and Inverting

- 1 Value-Fixing: giving a constant value to a wire

- F = 0; F = 1;

- 2 Transferring: giving a variable (wire) value from another variable (wire)

- F = X;

- 3 Inverting: inverting the value of a variable

- $F = \overline{X}$

#### Vector Denotation

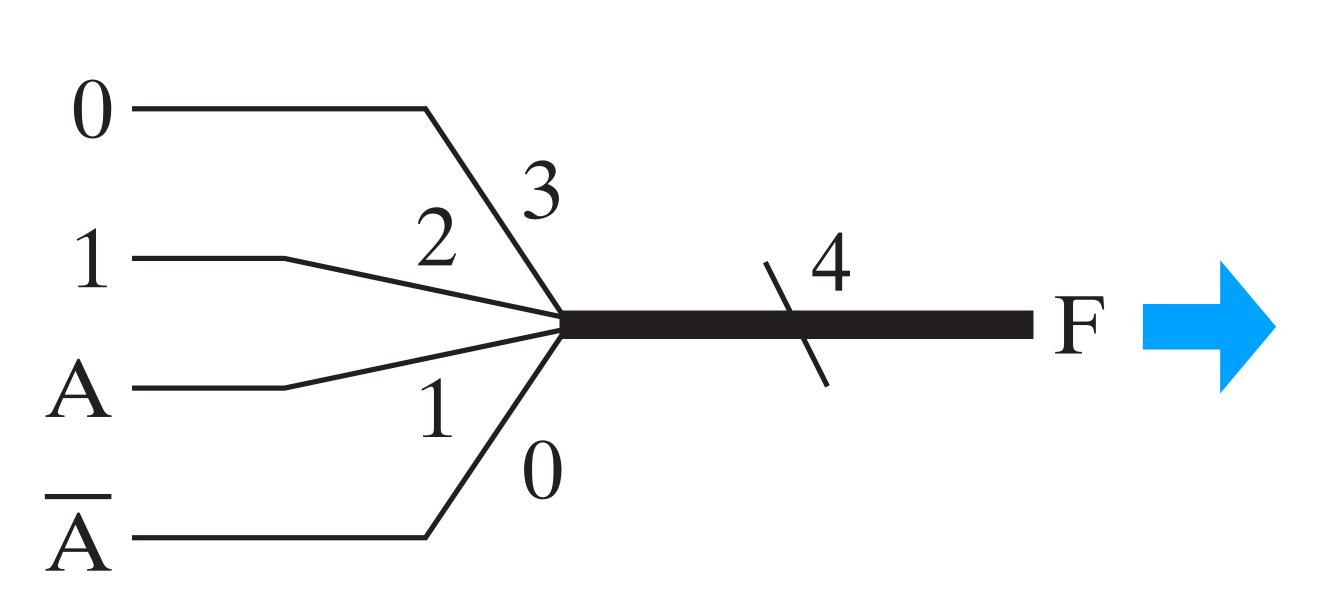

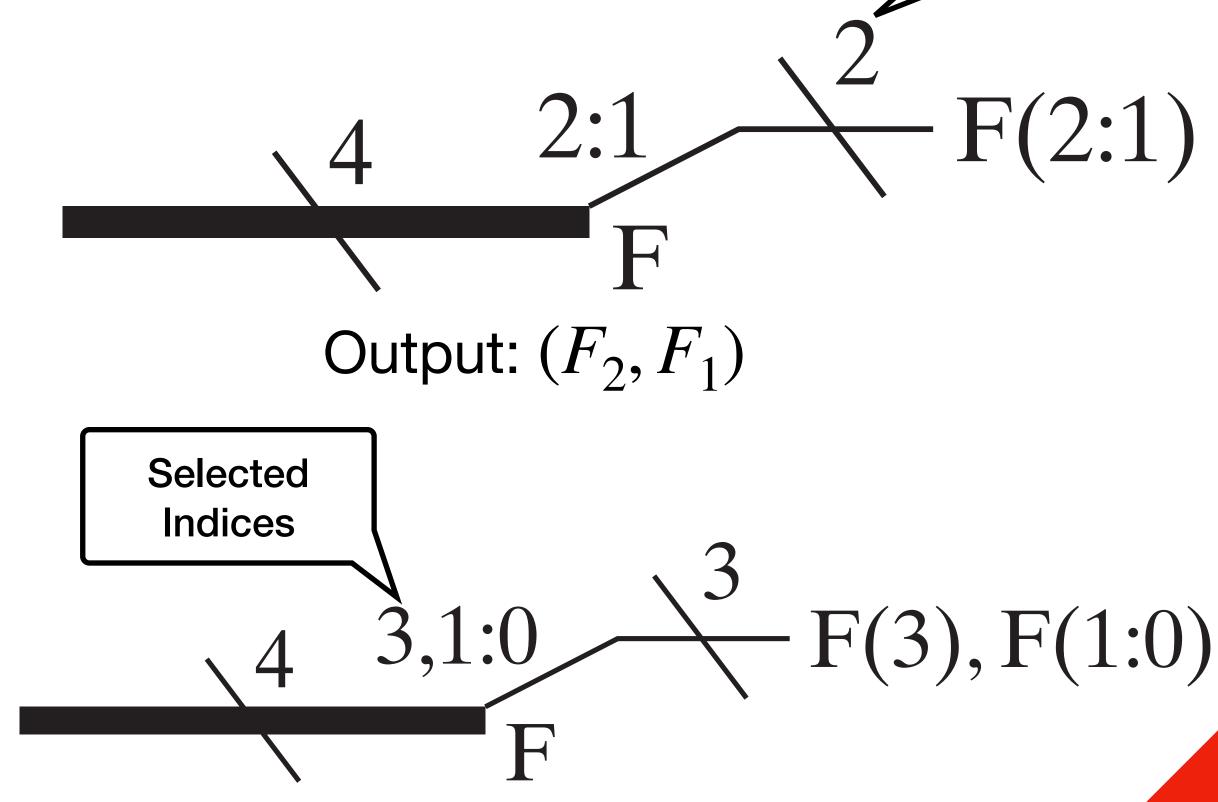

#### 4 Multiple-bit Function

- Functions we've seen so far has only one-bit output: 0/1

- Certain functions may have *n*-bit output

- $F(n-1:0) = (F_{n-1}, F_{n-2}, \dots, F_0)$ , each  $F_i$  is a one-bit function

- Curtain Motor Control Circuit:  $F = (F_{\text{Motor}_1}, F_{\text{Motor}_2}, F_{\text{Light}})$

Elementary Func.

## Taking part of the Vector

4 Multiple-bit Function

Output:  $(F_3, F_1, F_0)$

6000

**Dimension**

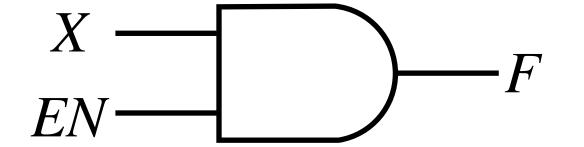

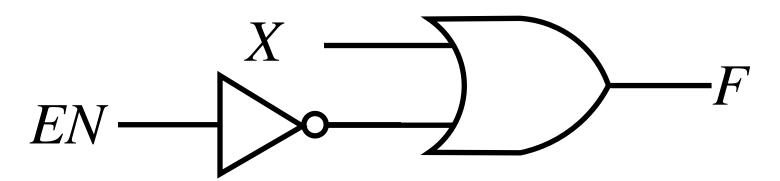

#### Enabler

#### **5** Enabler

• Transferring function, but with an additional EN signal acting as switch

| EN | X | F |

|----|---|---|

| 0  |   | 0 |

| 1  | 0 | 0 |

| 1  | 1 | 1 |

Color

#### Enabler

#### **5** Enabler

ullet Transferring function, but with an additional EN signal acting as switch

Colocolo

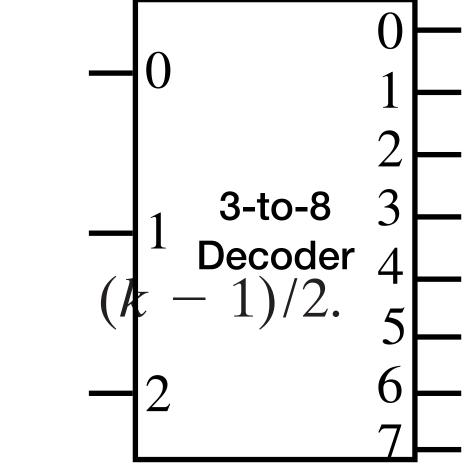

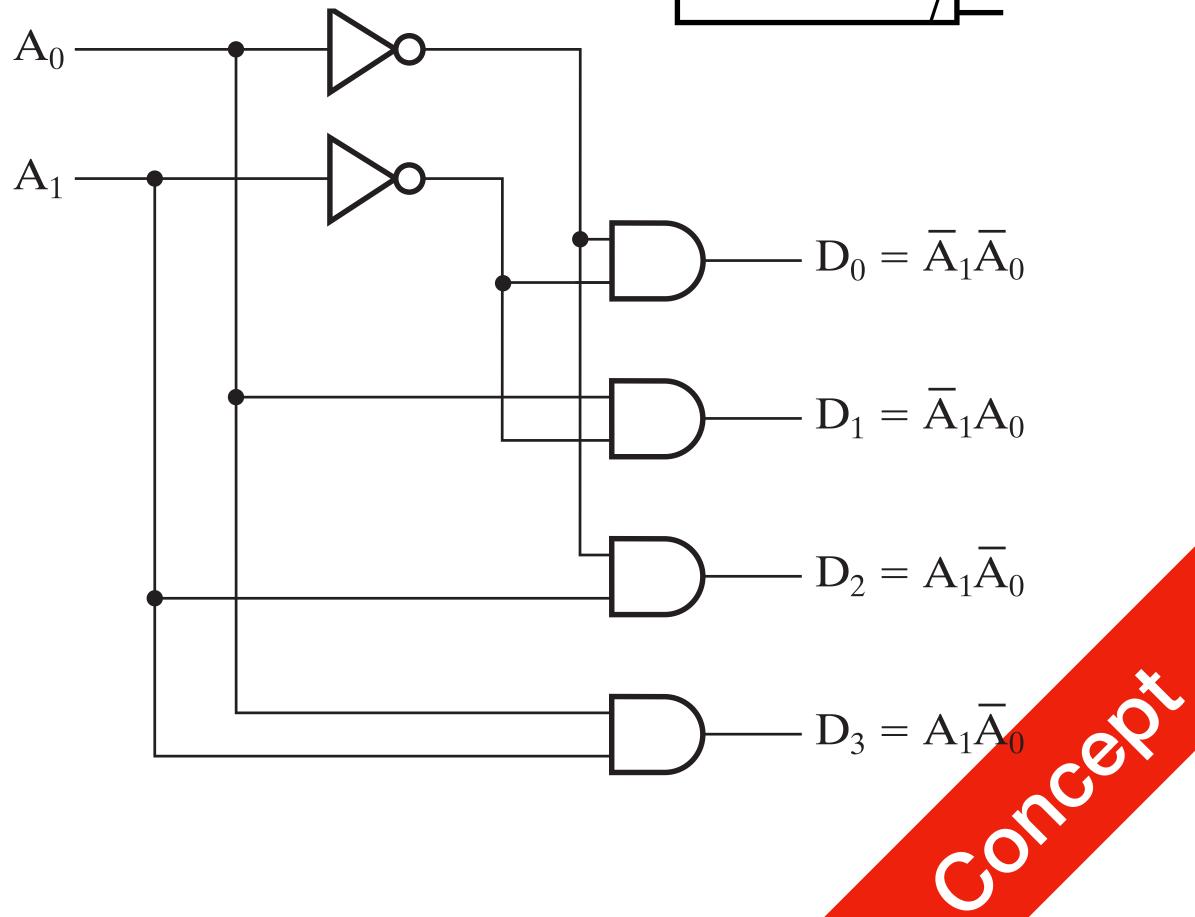

#### k = n Decoder

- n-bit input,  $2^n$ bits output

- $D_i = m_i$

- Design: use hierarchical designs!

| A <sub>1</sub> | A <sub>0</sub> | D <sub>0</sub> | D <sub>1</sub> | D <sub>2</sub> | D <sub>3</sub> |

|----------------|----------------|----------------|----------------|----------------|----------------|

| 0              | 0              | 1              | 0              | 0              | 0              |

| 0              | 1              | 0              | 1              | 0              | 0              |

| 1              | 0              | 0              | 0              | 1              | 0              |

| 1              | 1              | 0              | 0              | 0              | 1              |

(k + 1)/2

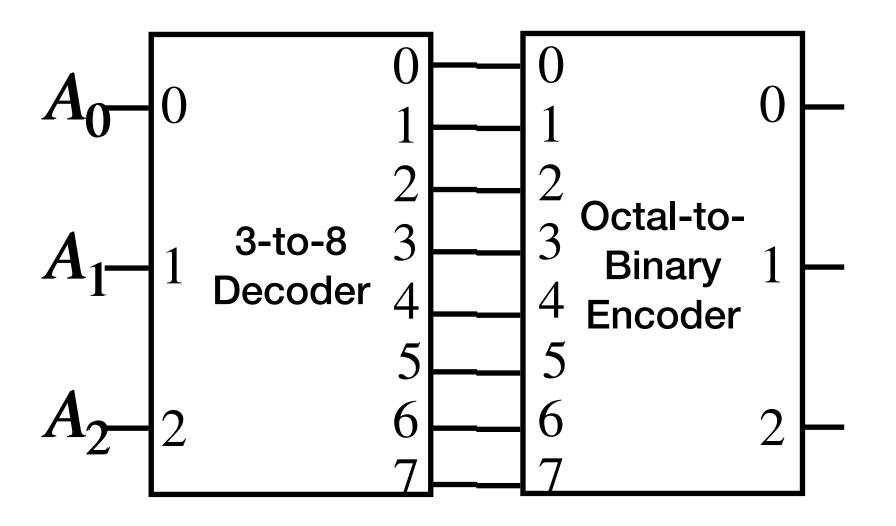

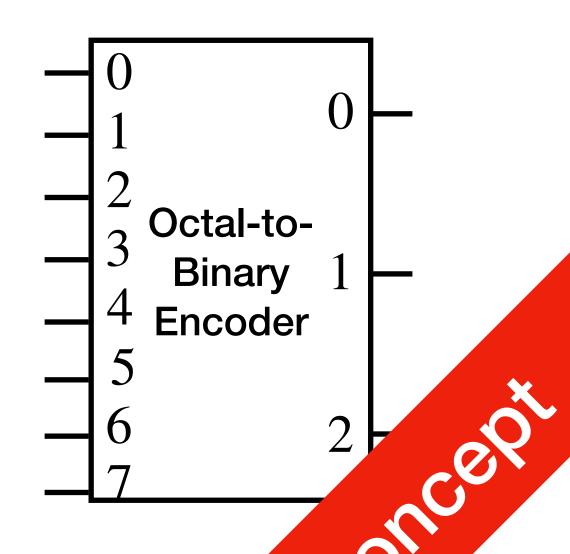

#### Encoder

- Inverse operation of a decoder

- $2^n$  inputs, only one is giving positive input<sup>1</sup>

- *n* outputs

1. In reality, could be less

#### Encoder

| D <sub>7</sub> | D <sub>6</sub> | D <sub>5</sub> | D <sub>4</sub> | D <sub>3</sub> | D <sub>2</sub> | D <sub>1</sub> | D <sub>0</sub> | A <sub>2</sub> | A <sub>1</sub> | A <sub>0</sub> |

|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|

|                |                |                |                |                |                |                | 1              | 0              | 0              | 0              |

|                |                |                |                |                |                | 1              |                | 0              | 0              | 1              |

|                |                |                |                |                | 1              |                |                | 0              | 1              | 0              |

|                |                |                |                | 1              |                |                |                | 0              | 1              | 1              |

|                |                |                | 1              |                |                |                |                | 1              | 0              | 0              |

|                |                | 1              |                |                |                |                |                | 1              | 0              | 1              |

|                | 1              |                |                |                |                |                |                | 1              | 1              | 0              |

| 1              |                |                |                |                |                |                |                | 1              | 1              | 1              |

| $A_0$ | $= D_1 +$ | $D_3 +$ | $D_5 + D$ | 7 |

|-------|-----------|---------|-----------|---|

| $A_1$ | $= D_2 +$ | $D_3 +$ | $D_6 + D$ | 7 |

| $A_2$ | $= D_4 +$ | $D_5 +$ | $D_6 + D$ | 7 |

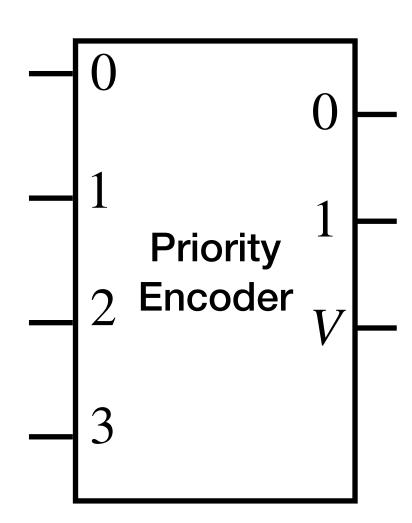

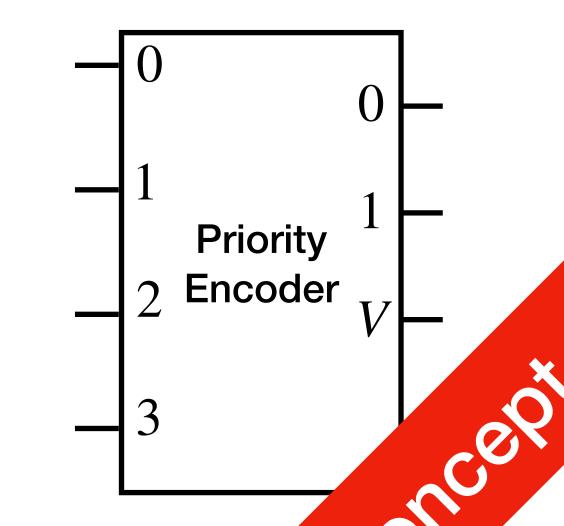

### Priority Encoder

- ullet Additional Validity Output V

- Indicating whether the input is valid (contains 1)

- Priority

- Ignores  $D_{< i}$  if  $D_i = 1$

COUCS!

P3.3 Adv. Func. Blocks

## Priority Encoder

| D <sub>3</sub> | D <sub>2</sub> | D <sub>1</sub> | D <sub>0</sub> | A <sub>1</sub> | A <sub>0</sub> | V |

|----------------|----------------|----------------|----------------|----------------|----------------|---|

| 0              | 0              | 0              | 0              | 0              | 0              | 0 |

| 0              | 0              | 0              | 1              | 0              | 0              | 1 |

| 0              | 0              | 1              | X              | 0              | 1              | 1 |

| 0              | 1              | X              | X              | 1              | 0              | 1 |

| 1              | X              | X              | X              | 1              | 1              | 1 |

$$V = D_3 + D_2 + D_1 + D_0$$

$$A_1 = D_3 + \overline{D_3}D_2 = D_2 + D_3$$

$$A_0 = \overline{D_3}\overline{D_2}D_1 + D_3$$

$$= \overline{D_2}D_1 + D_3$$

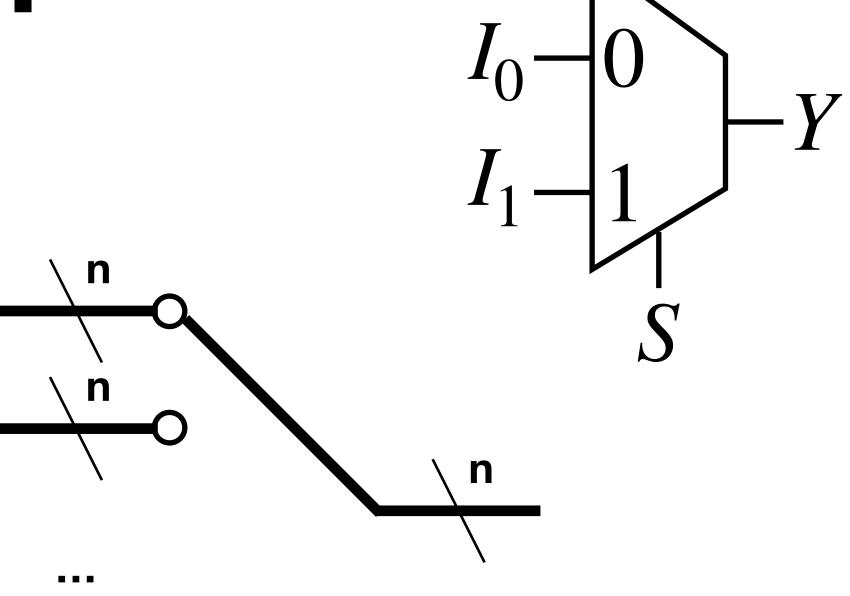

### Multiplexer

- Multiple *n*-variable input vectors

- Single n-variable output vector

- Switches: which input vectors to output

#### Common Techniques

- Implementing Multiplexer using Decoders

- Implementing Multiplexer using smaller Multiplexers

- Implementing Sum-of-Minterm using Decoder (use OR gate)

- Implementing Sum-of-Minterm using Multiplexer (use value fixing)

Cook Cook

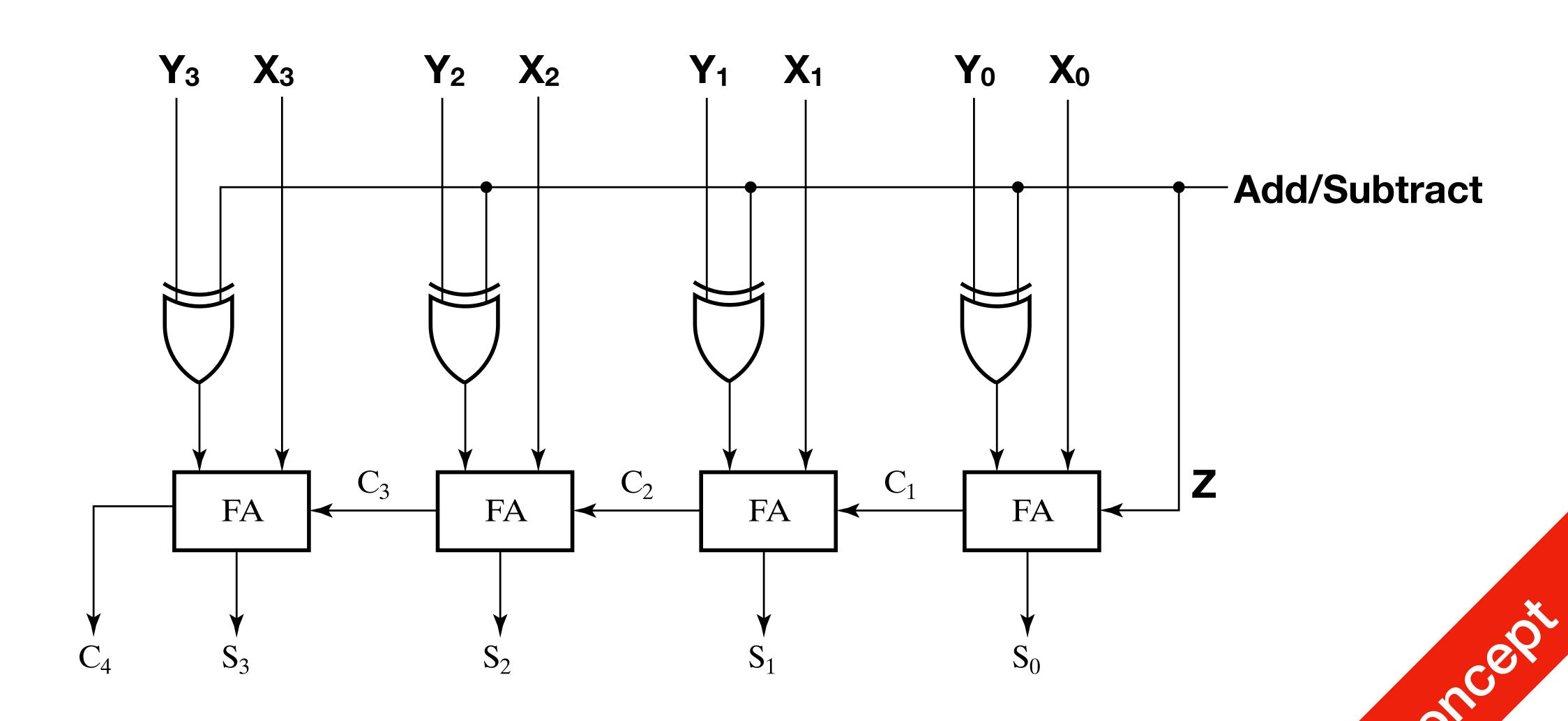

#### Arithmetic Blocks

- 1-bit Half Adder and Full Adder

- n-bit Adder

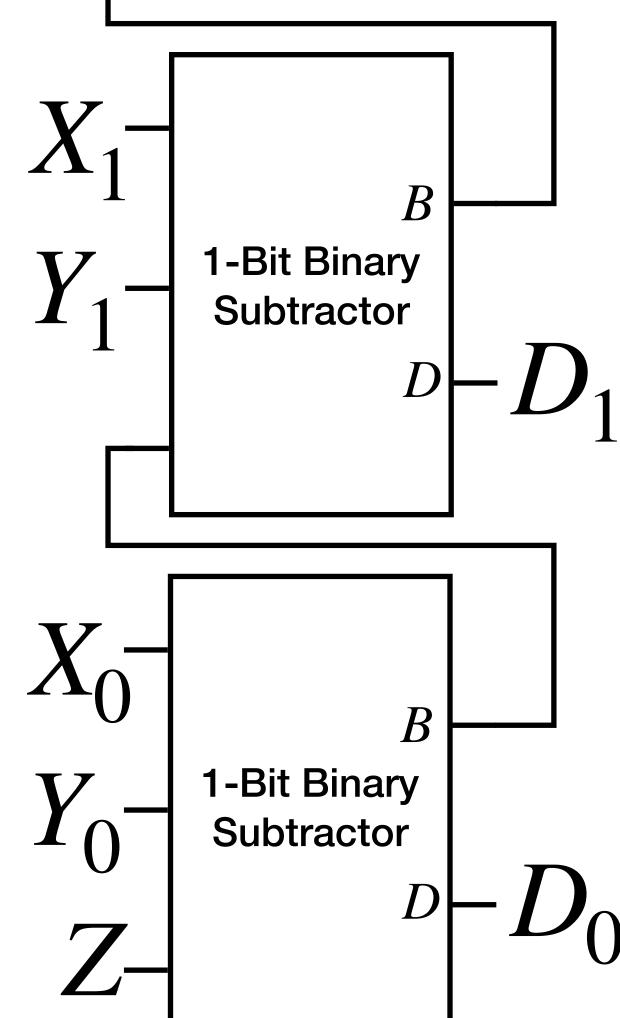

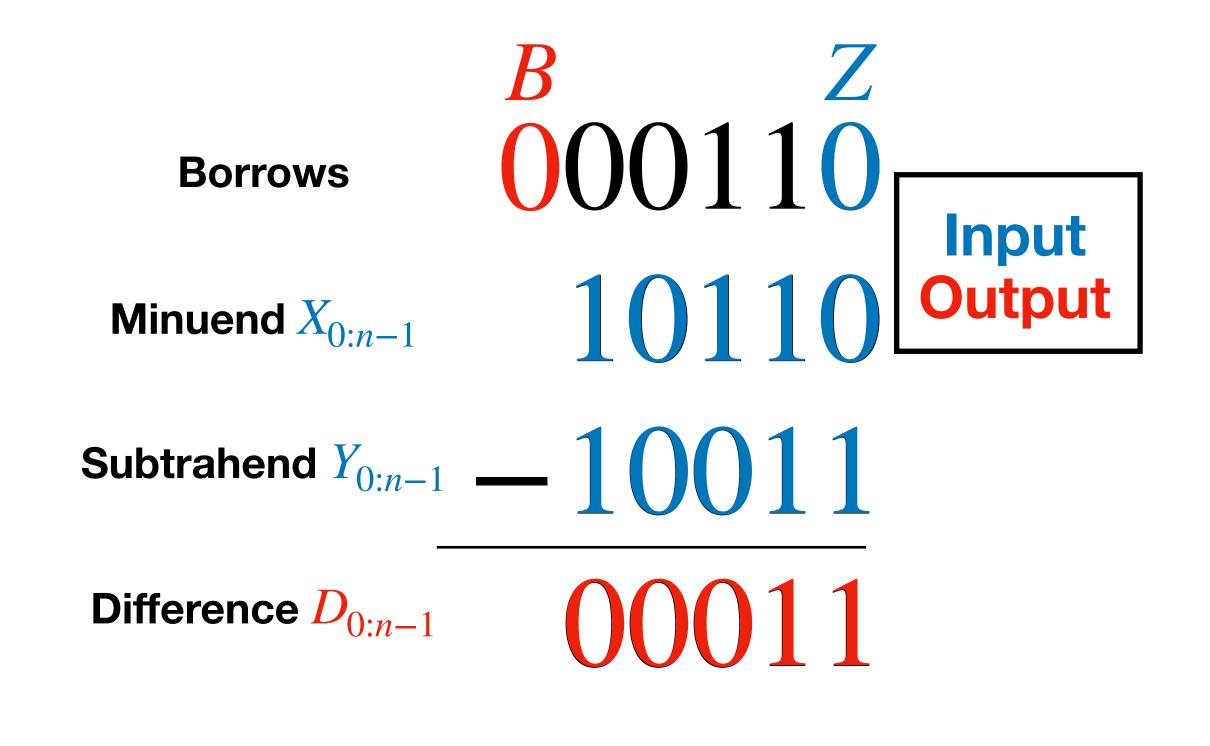

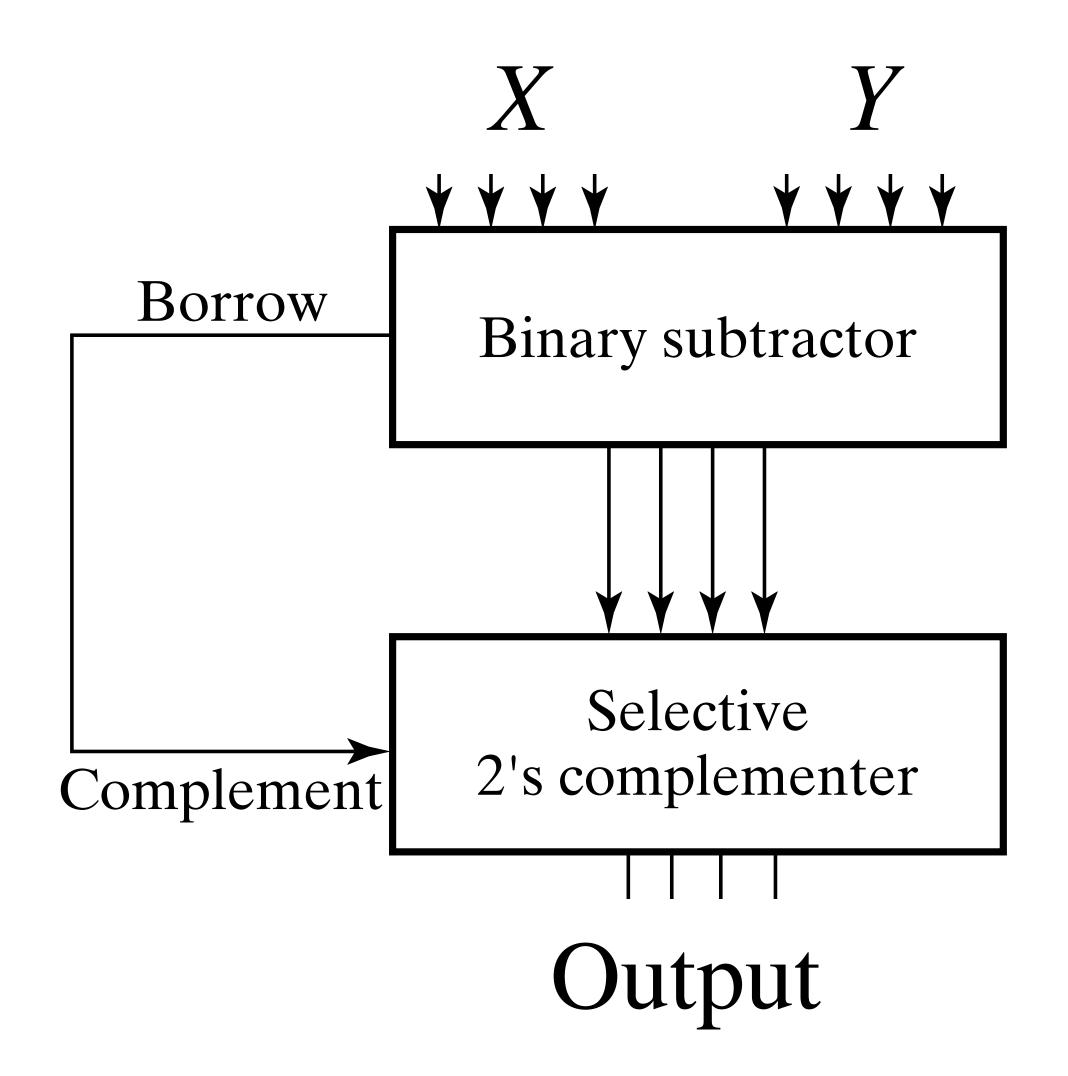

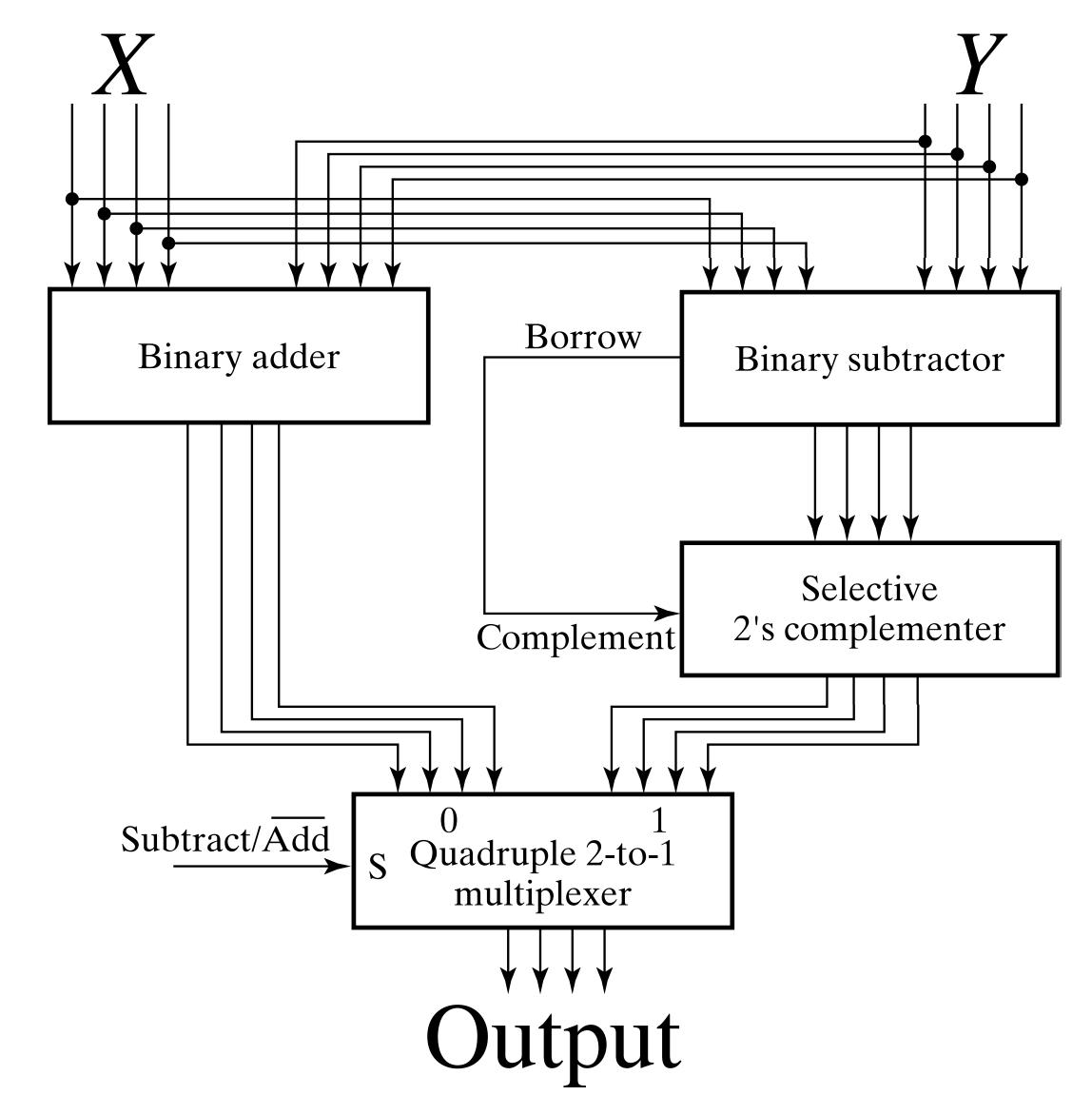

- 1-bit subtractor and n-bit subtractor

- 2s complement and binary addersubtractor

Color

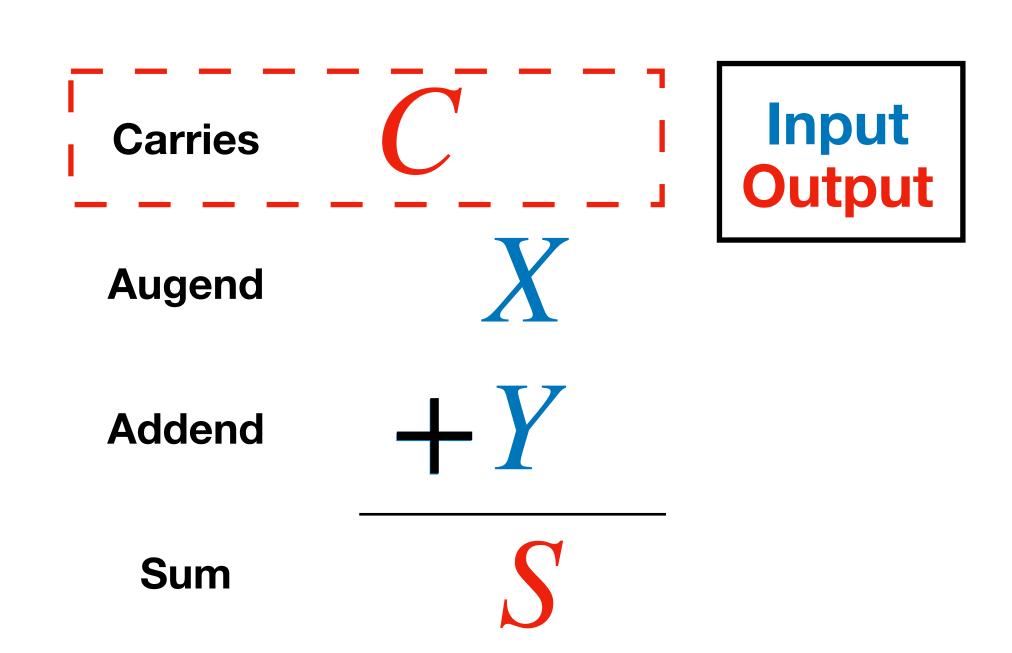

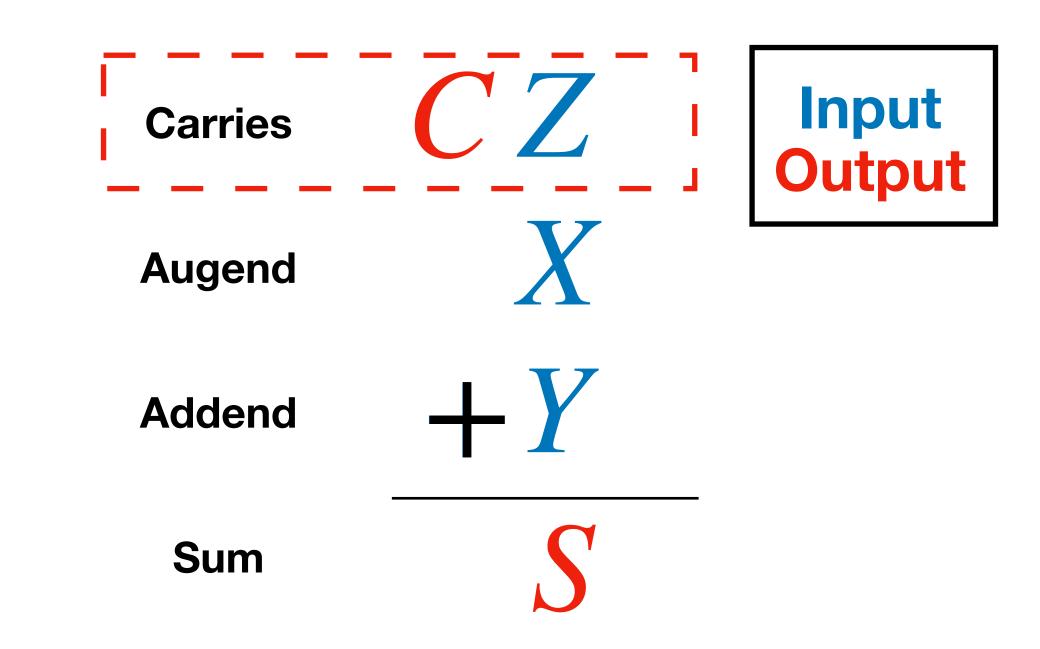

#### 1-bit Adder

• Half adder input X, Y output S, C

• Full adder input X, Y, Z; output S, C

Unsigned Binary

Subtraction

Technology

• 1 bit Unsigned Subtractor

P3.4

**Arithmetic Blocks**

### Arithmetic Blocks Full Unsigned Subtraction

#### Adder Subtractor I

#### Adder-Subtractor II