#### CSCI 150 Introduction to Digital and Computer System Design Lecture 3: Combinational Logic Design VII

Jetic Gū 2020 Fall Semester (S3)

#### Overview

- Focus: Arithmetic Functional Blocks

- Architecture: Combinatory Logical Circuits

- Textbook v4: Ch4 4.3, 4.4, 4.7; v5: Ch2 2.9, Ch3 3.10, 3.11

- Core Ideas:

- 1. Subtraction II

- 2. Subtraction III

- 3. VHDL

P0 Review

# Unsigned Binary Subtraction I

Review

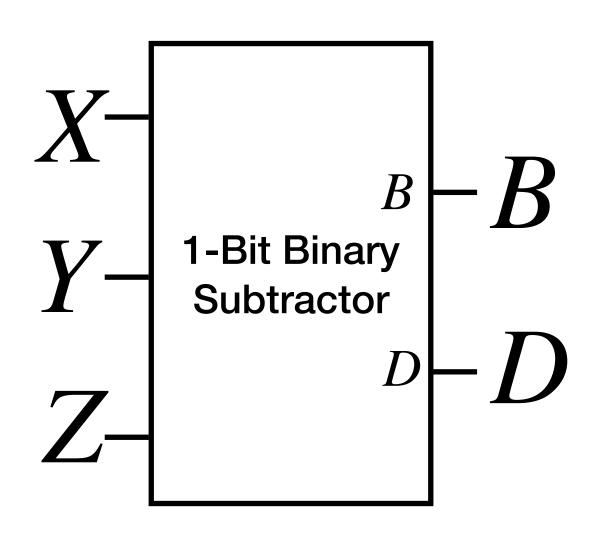

#### **Unsigned 1-bit Binary** Subtraction

- Implementation using 3-to-8 Decoder

- $B = \Sigma m(1,2,3,7)$

- $D = \Sigma m(1,2,4,7)$

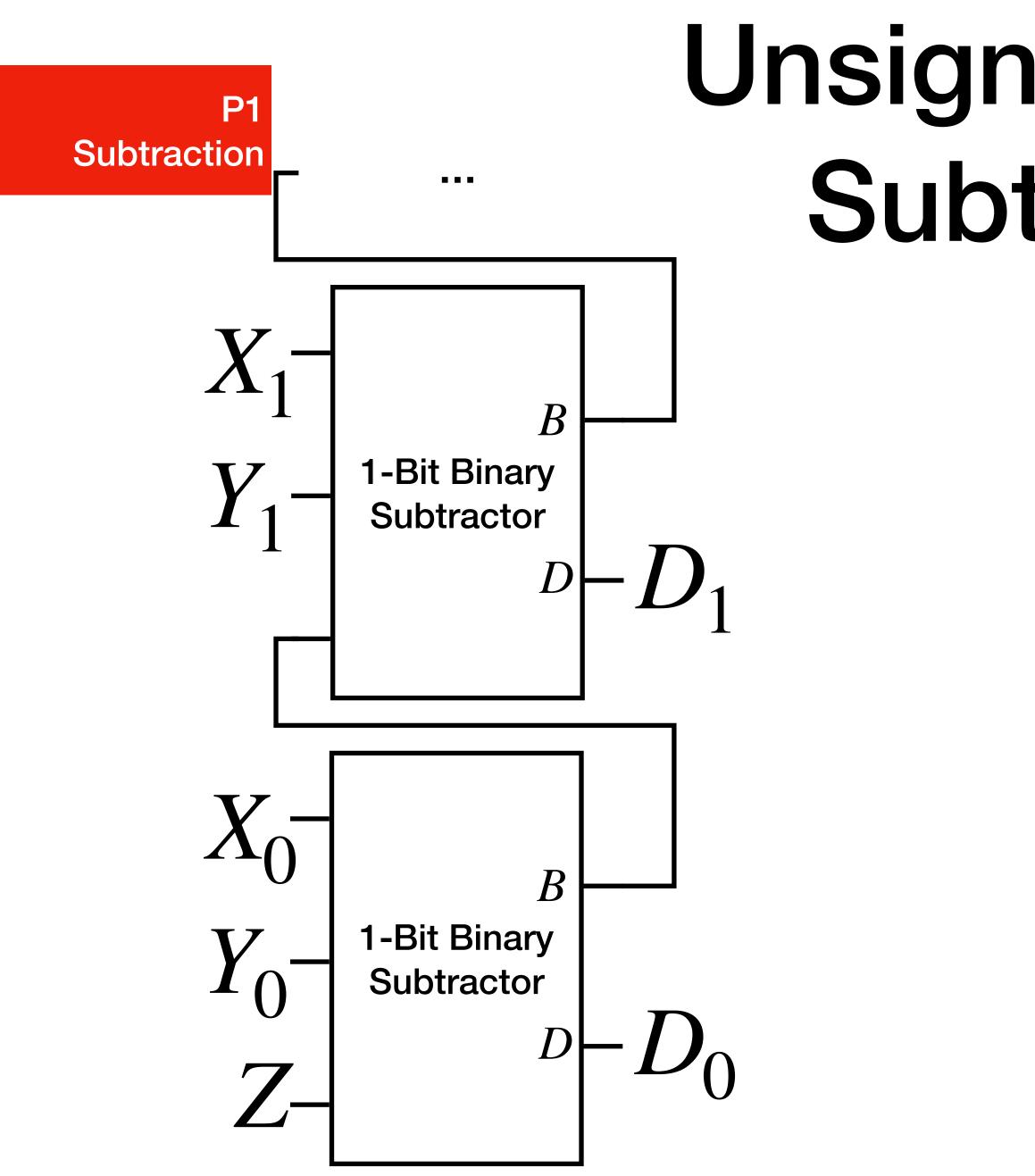

#### Unsigned Binary Subtraction

Technology

• 1 bit Unsigned Subtractor

# $\begin{array}{ccc} B & Z \\ 0000110 \\ Minuend X_{0:n-1} & 10110 \end{array} \quad \begin{array}{c} Input \\ 0utput \end{array}$ Subtrahend $Y_{0:n-1} - 10011 \\ Difference D_{0:n-1} & 00011 \end{array}$

#### Unsigned Binary Subtraction II X - Y when Y > X

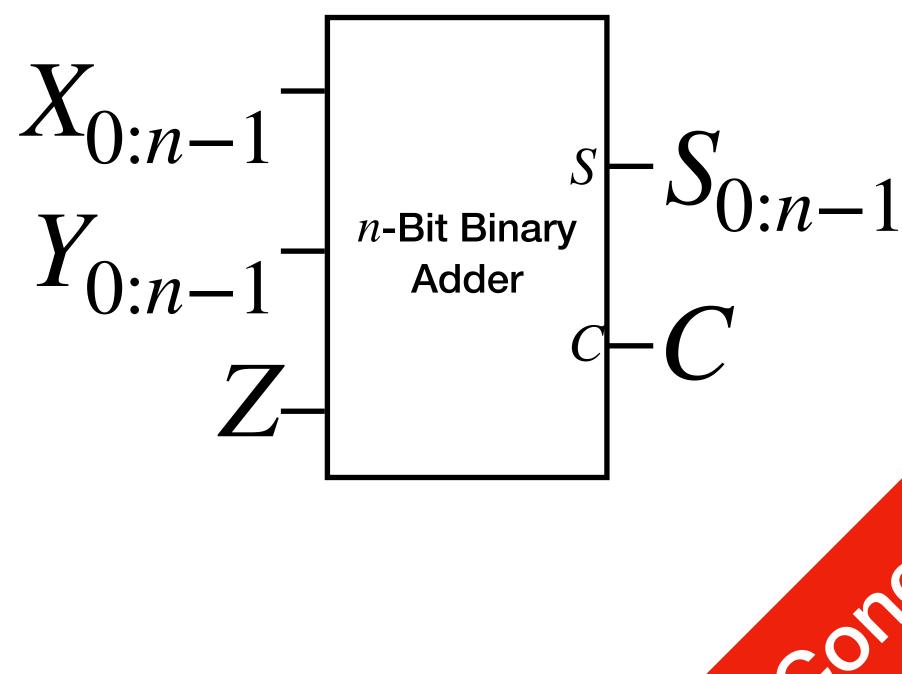

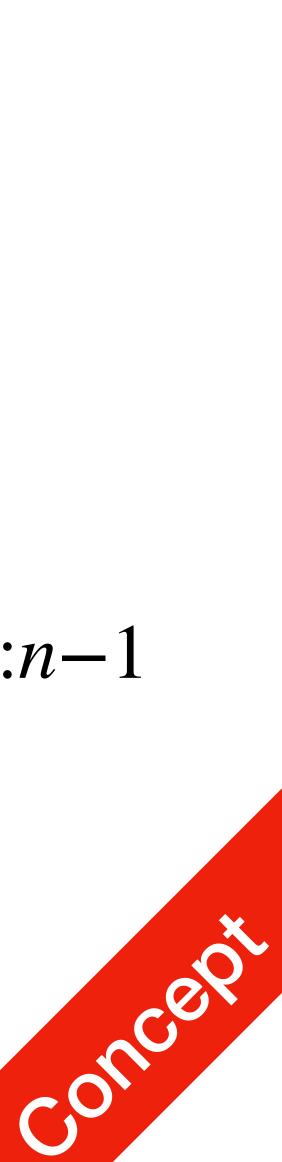

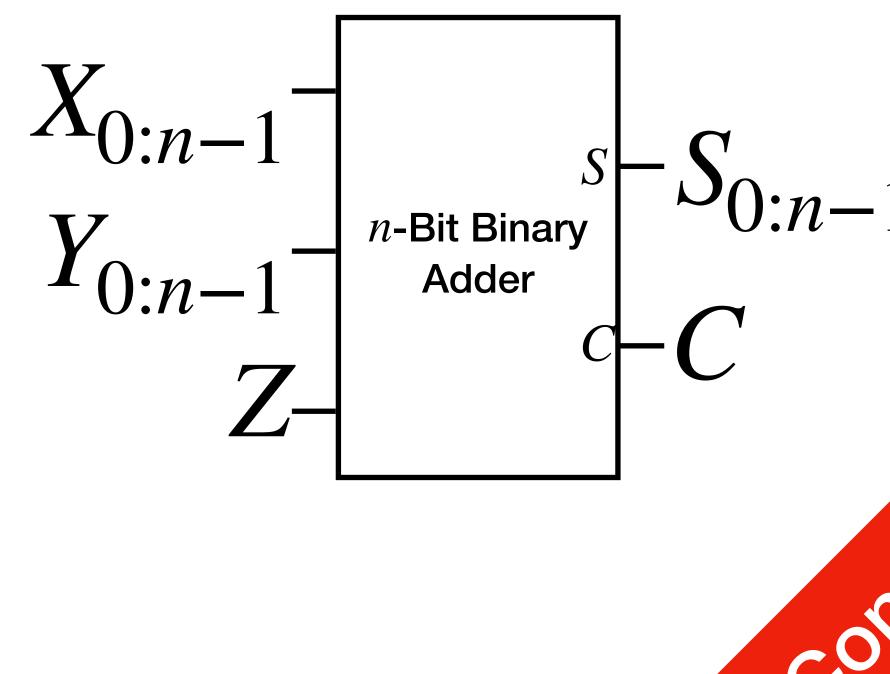

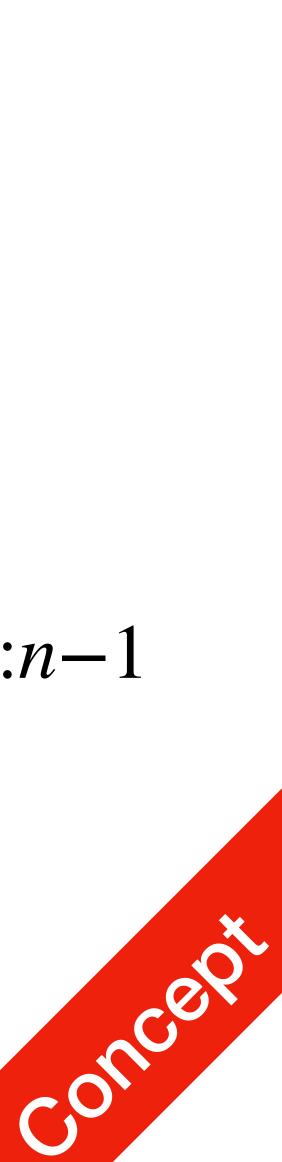

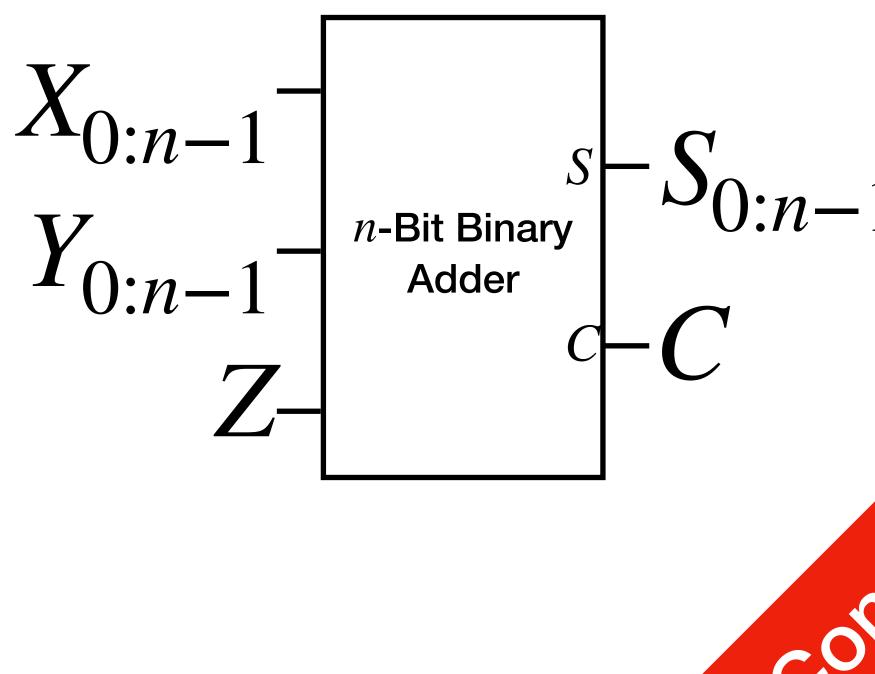

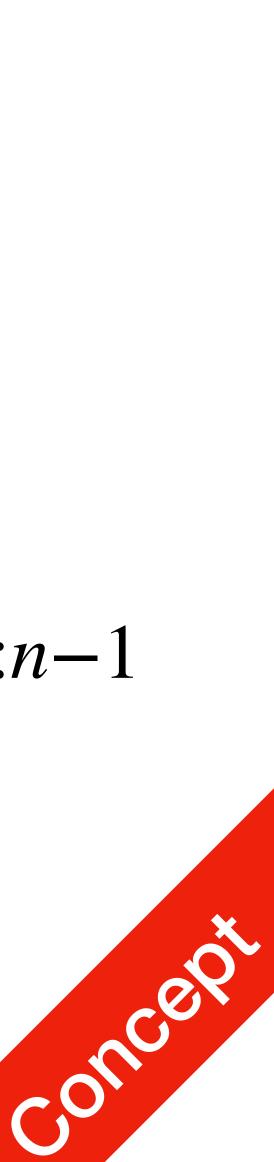

- Binary Adder

- Binary Subtractor  $(X Y, X \ge Y)$

#### What we have so far

- the greater number

- What if it's the opposite? i.e. X < Y, F = X Y?

#### X > Y, F = X - Y

• We learned to perform subtraction, by subtracting the smaller number from

#### **Borrows**

Minuend

Subtrahend

# -0011

Difference

**Borrows**

Minuend

Subtrahend

# -100110

Difference

#### **Borrows**

Minuend

Subtrahend

# -0011

Difference

**Borrows**

Minuend

Subtrahend

# -100110

Difference

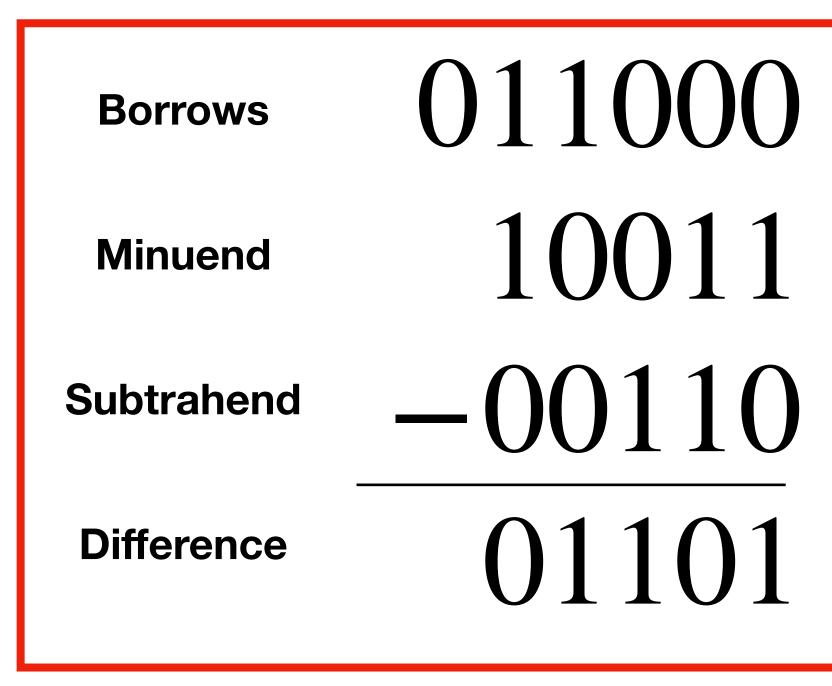

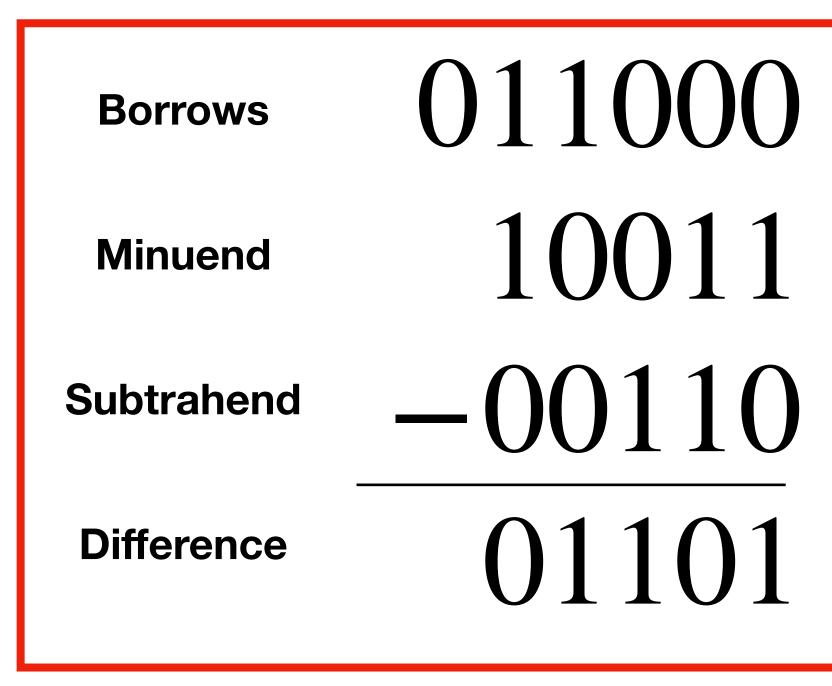

# Borrows011000Minuend10011Subtrahend-00110Difference01101

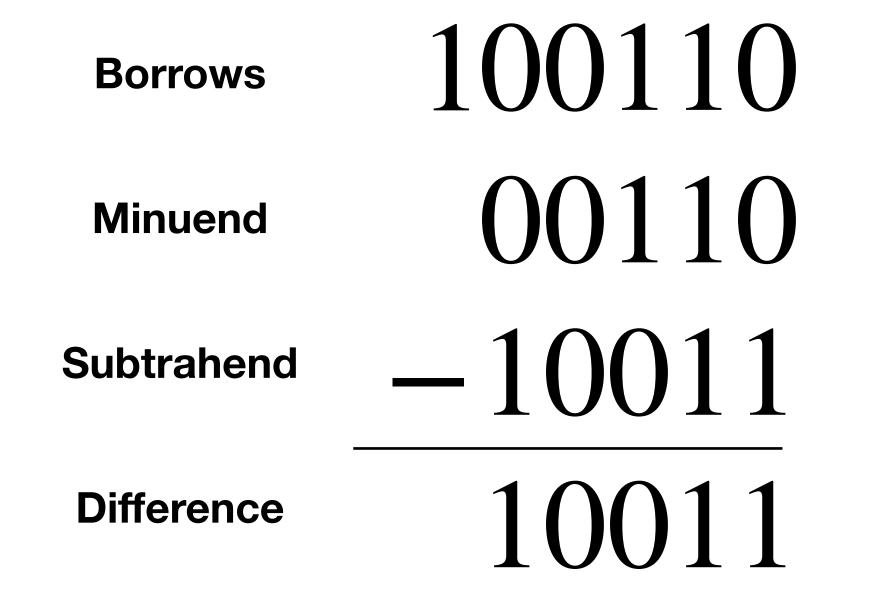

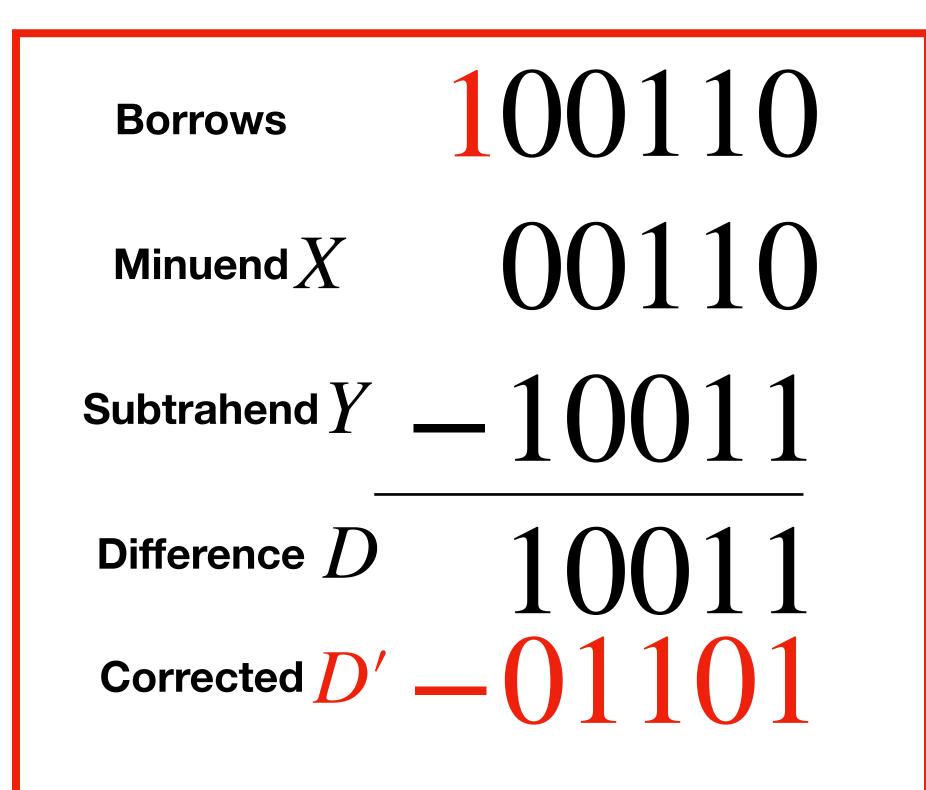

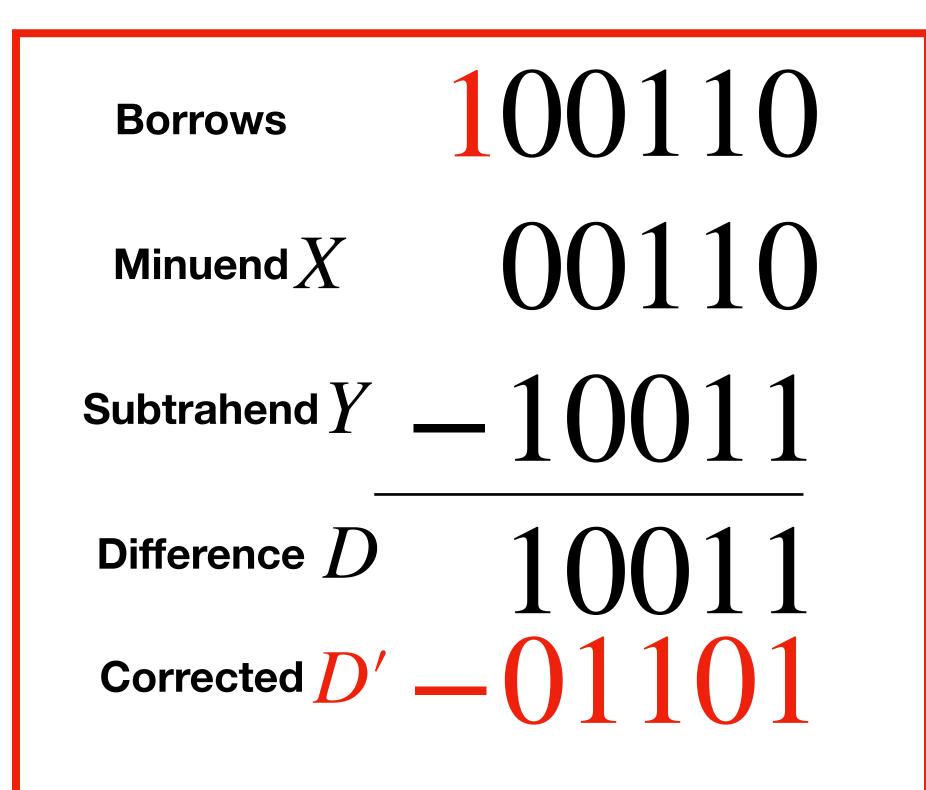

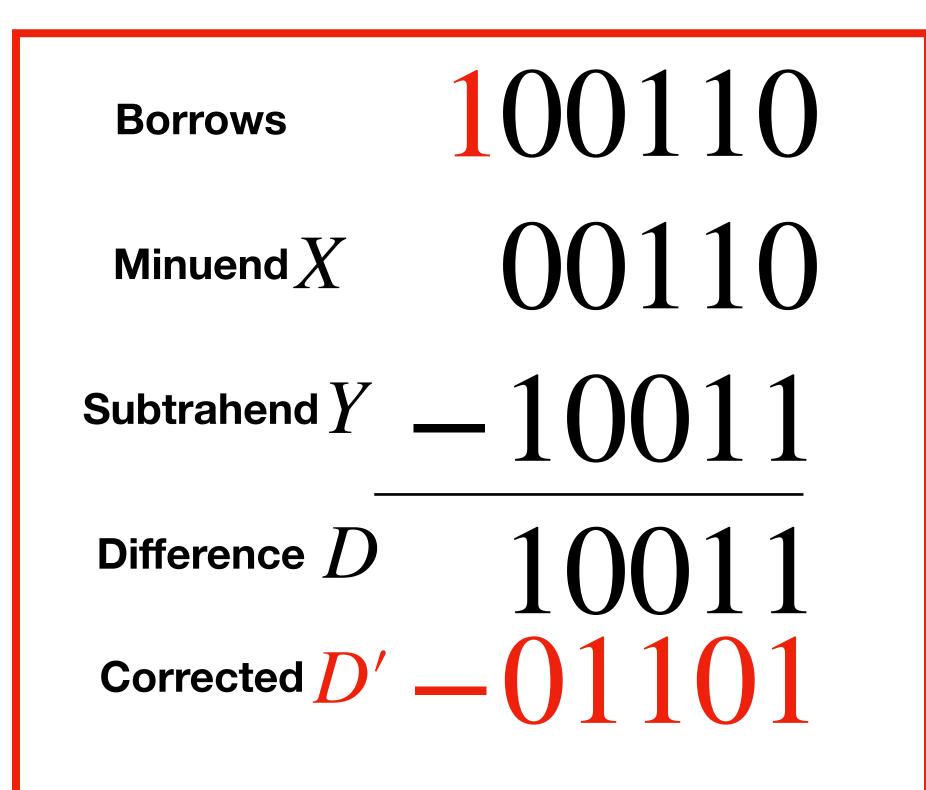

# Borrows100110Minuend00110Subtrahend-10011Difference10011

This is correct

Borrows100110Minuend00110Subtrahend-10011Difference10011

This is correct

This is incorrect

Standard subtraction module works if the Minuend is bigger than the Subtrahend

| 011000 |

|--------|

| 10011  |

| -00110 |

| 01101  |

|        |

This is correct

| Borrows    | 100110 |

|------------|--------|

| Minuend    | 00110  |

| Subtrahend | -10011 |

| Difference | 10011  |

|            |        |

This is incorrect

Standard subtraction module works if the Minuend is bigger than the Subtrahend

(2's compliment)

- Standard subtraction module works if the Minuend is bigger than the Subtrahend

- Incorrect output D  $= 2^{n} + X - Y$

#### (2's compliment)

- Standard subtraction module works if the Minuend is bigger than the Subtrahend

- Incorrect output D  $= 2^{n} + X - Y$

Correct output D' = -(Y - X) $= -(2^{n} - D)$  $= -(\overline{D} + 1)$  (2's compliment)

## 2s compliment

- Given binary unsigned integer of n bits D, its 2s compliment  $2^n - D = \overline{D} + 1$

- Proof

- Biggest number represented in *n* bit:  $(11...1)_2 = 2^n 1$

- $2^n D = [(11...1)_2 + 1] D = (11...1)_2 D + 1 = \overline{D} + 1$

- Implementation

- Inversion and plus 1, easily doable as complementer

#### Subtraction

#### 1. Compute 20-15=5 using 6-bit binary

#### 1. Compute 20-15=5 using 6-bit binary

•  $20 = (010100)_2$ ,  $15 = (001111)_2$

#### 1. Compute 20-15=5 using 6-bit binary

•  $20 = (010100)_2$ ,  $15 = (001111)_2$

0011110Borrows 010100-001111000101

- 1. Compute 20-15=5 using 6-bit binary

- $20 = (010100)_2$ ,  $15 = (001111)_2$

- 2. Compute 15-20=-5 using 6-bit binary and 2s complement

Borrows 0011110 )<sub>2</sub> 010100 hary and 2s complement 0001111 000101

- 1. Compute 20-15=5 using 6-bit binary

- $20 = (010100)_2$ ,  $15 = (001111)_2$

- 2. Compute 15-20=-5 using 6-bit binary and 2s complement

Borrows 0011110 )<sub>2</sub> 010100 hary and 2s complement 0001111 000101

- 1. Compute 20-15=5 using 6-bit binary

- $20 = (010100)_2$ ,  $15 = (001111)_2$

- 2. Compute 15-20=-5 using 6-bit binary and 2s complement

- Correction:  $(111011)_2$  2s complement:  $(000101)_2$

110000Borrows 001111-010100111011

- 1. Compute 20-15=5 using 6-bit binary

- $20 = (010100)_2$ ,  $15 = (001111)_2$

- 2. Compute 15-20=-5 using 6-bit binary and 2s complement

Borrows 1 100000 )2 hary and 2s complement -010100 111011

#### 1. Compute 7-15=-8 using 6-bit binary and 2s complement

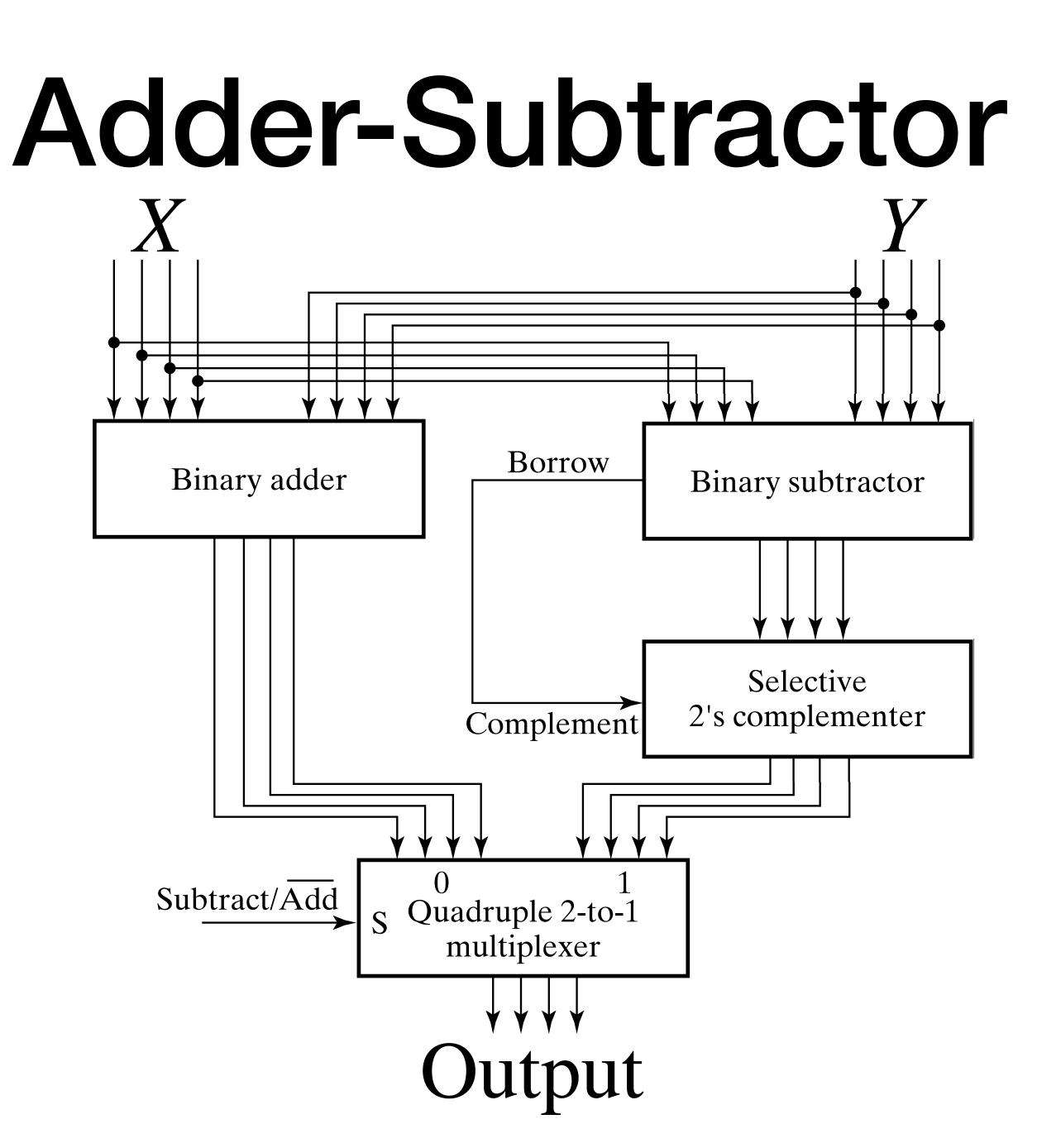

### Subtraction Full Unsigned Subtraction

- Solution 1

- Compare the Minuend and Subtra greater, then add negative sign

- Solution 2

- Use 2s compliment

• Compare the Minuend and Subtrahend, switch places if the Subtrahend is

#### Subtraction Full Unsigned Subtraction

Selective 2's complementer

# Output

#### Subtraction Full Unsigned Subtraction

$\begin{array}{cccc} X & Y \\ & & & & & & & \\ & & & & & & & \\ & & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & &$

Selective 2's complementer

# Unsigned Binary Subtraction III

What do you mean we can do subtraction using an adder?

### 2s compliment

#### $2^n - D = \overline{D} + 1$

#### Subtraction using 2s Complement

- Input: X and Y

- *Y*: 2s complement  $Y' = \overline{Y} + 1$  ( $\overline{Y}$

- $X Y = X + (2^n Y) 2^n = X$

- Since  $2^n = (10...0)_2$ , and we only output *n*-bits, it can be discarded

$$+1 = 2^n - Y$$

)

$$X + Y' - 2^n$$

#### Subtraction using 2s Complement

• 84 - 67 (10bit)

#### Subtraction using 2s Complement

• 84 - 67 (10bit)

#### X = 0001010100

#### Subtraction using 2s Complement

• 84 - 67 (10bit)

X = 0001010100Y = 0001000011

#### Subtraction using 2s Complement

• 84 - 67 (10bit)

**2s complement**

X = 0001010100Y = 0001000011Y' = 111011101

#### Subtraction using 2s Complement

• 84 - 67 (10bit)

**2s complement**

X = 0001010100Y = 0001000011Y' = 1110111101X + Y' = 10000010001

#### Subtraction using 2s Complement

• 84 - 67 (10bit)

**2s complement**

X = 0001010100Y = 0001000011Y' = 1110111101X + Y' = 10000010001discard carry  $X + Y' - 2^{10} = 0000010001$

#### Subtraction using 2s Complement

• 84 - 67 (10bit)

**2s complement**

discard carry  $X + Y' - 2^{10} = 0000010001$

- X = 0001010100

- Y = 0001000011

- Y' = 1110111101

- X + Y' = 10000010001

- verify  $(84 67)_{10} = 17_{10} = 10001 = 0000010001$

#### Subtraction using 2s Complement

• 84 - 67 (10bit)

**2s complement**

discard carry  $X + Y' - 2^{10} = 0000010001$

- X = 0001010100

- Y = 0001000011

- Y' = 1110111101

- X + Y' = 10000010001

correct!

verify  $(84 - 67)_{10} = 17_{10} = 10001 = 0000010001$

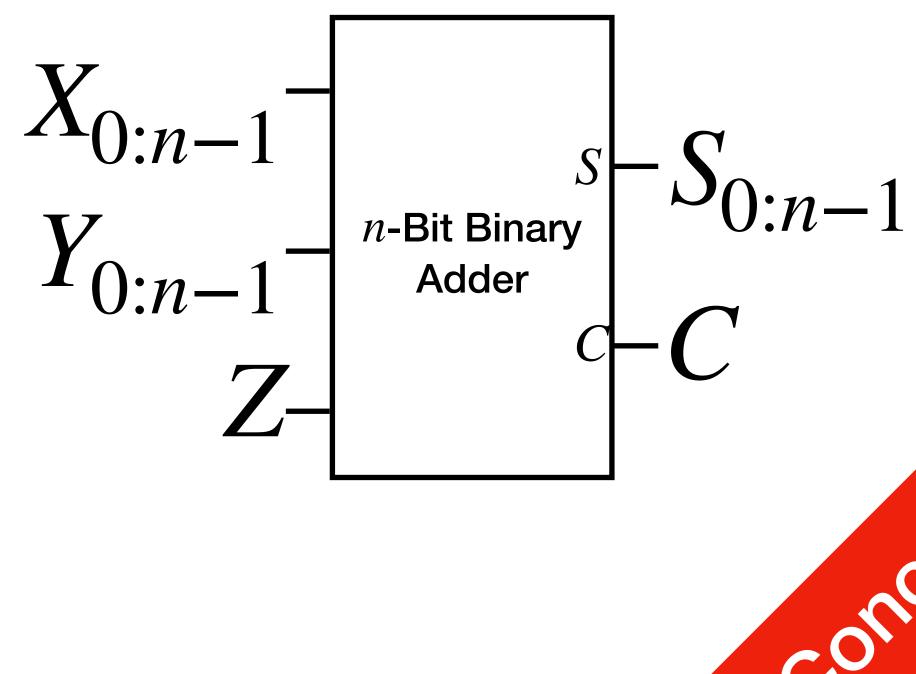

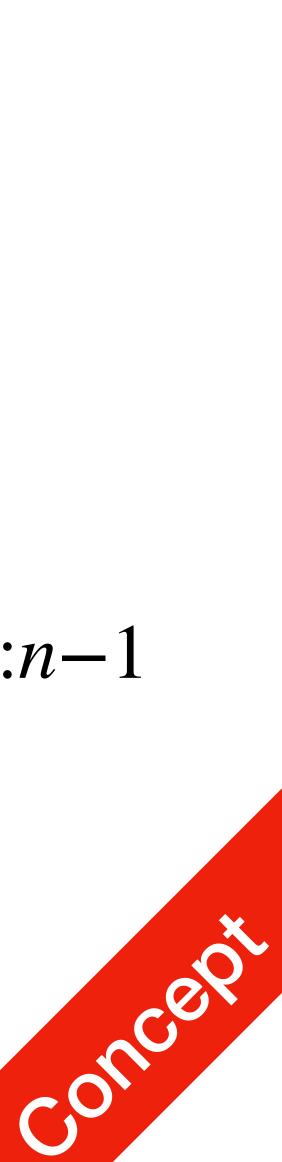

1. Adder

- 1. Adder

- 2. Complementer (Inverting and add 1)

- 1. Adder

- 2. Complementer (Inverting and add 1)

- Or just inverting, and then plus one

- 1. Adder

- 2. Complementer (Inverting and add 1)

- Or just inverting, and then plus one

- Addition: X + Y

- 1. Adder

- 2. Complementer (Inverting and add 1)

- Or just inverting, and then plus one

- Addition: X + Y

- Subtraction:  $X Y = X + \overline{Y} + 1 2^n$

- 1. Adder

- 2. Complementer (Inverting and add 1)

- Or just inverting, and then plus one

- Addition: X + Y

- Subtraction:  $X Y = X + \overline{Y} + 1 2^n$

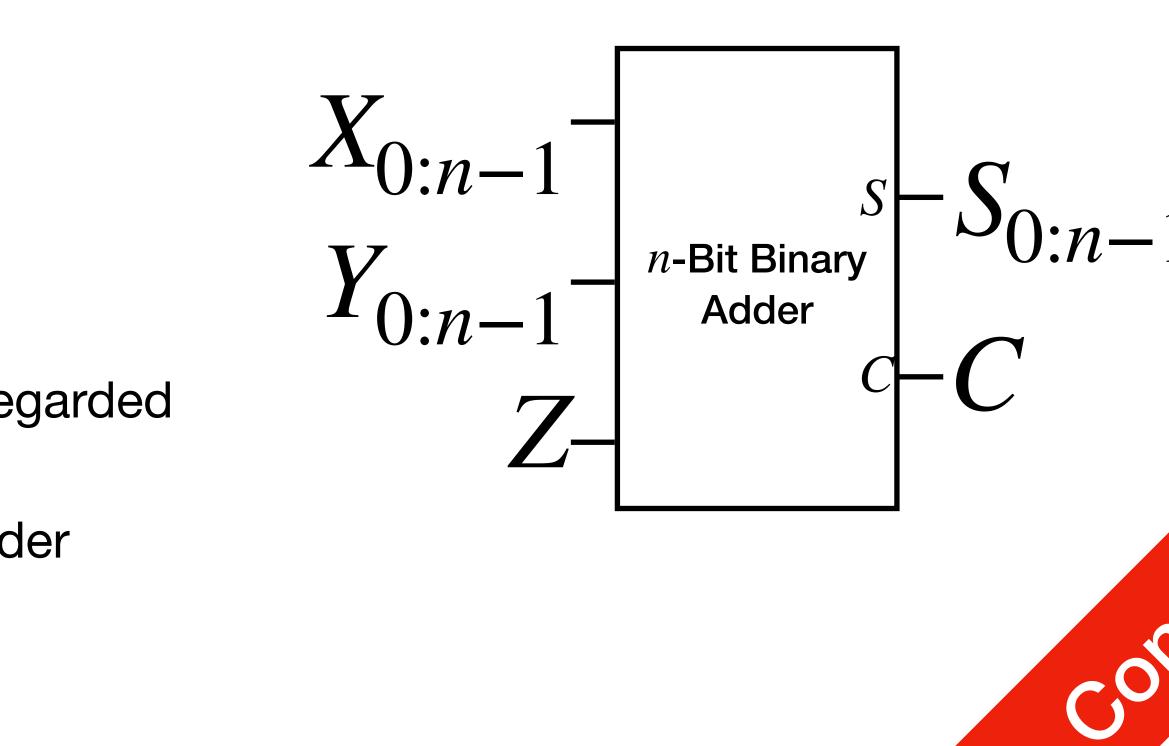

- We are using *n*-bit adder,  $2^n$  can be disregarded

- 1. Adder

- 2. Complementer (Inverting and add 1)

- Or just inverting, and then plus one

- Addition: X + Y

- Subtraction:  $X Y = X + \overline{Y} + 1 2^n$

- We are using *n*-bit adder,  $2^n$  can be disregarded

- The plus 1 here can be Z input to the adder

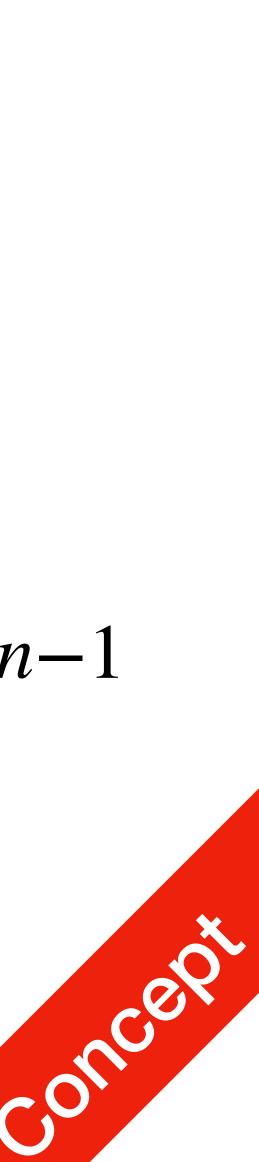

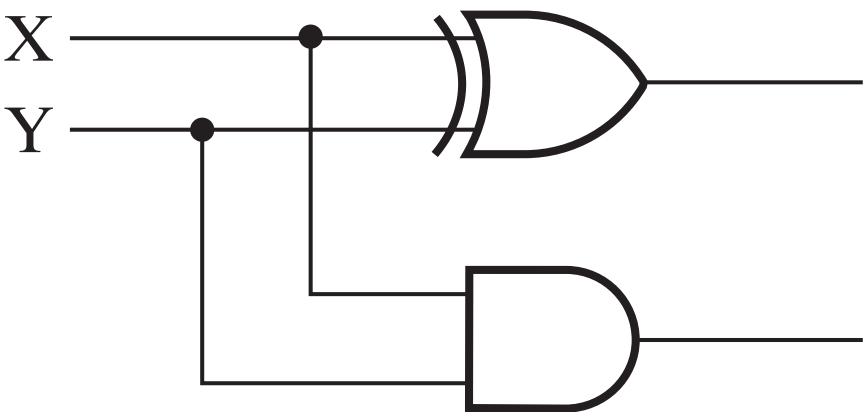

### Adder Subtractor Units (Unsigned)

P0-2 Adder-Subtractor

- Binary Adder

- Binary Subtractor

- Binary Adder-Subtractor Unit, using Adder, Subtractor, Complementer and Multiplexer

- Binary Adder-Subtractor Unit using Adder and XOR

**P3** Exercises

#### Excercises 2s Complement Subtraction using 2s Complement

### Subtraction

• Compute 10-7 using 4-bit binary using Adder and 2s complement

### Subtraction

• Compute 24-17 using 8-bit binary using Adder and 2s complement

# Hardware Description Language

VHDL (VHSIC-HDL): Very High Speed Integrated Circuit Hardware Description Language

## PARTICIPATION PARTICIPATICA PA

- Create a new component in VHDL called HalfAdder1

- Input: X, Y

- Output: S, C

- **Don't use** AFTER

### PARTICIPATION PARTICIPATICA PA

#### architecture arch1 of HalfAdder is

#### begin

$S \ll X X OR Y;$

$C \ll X AND Y;$

end arch1;

P4 VHDL

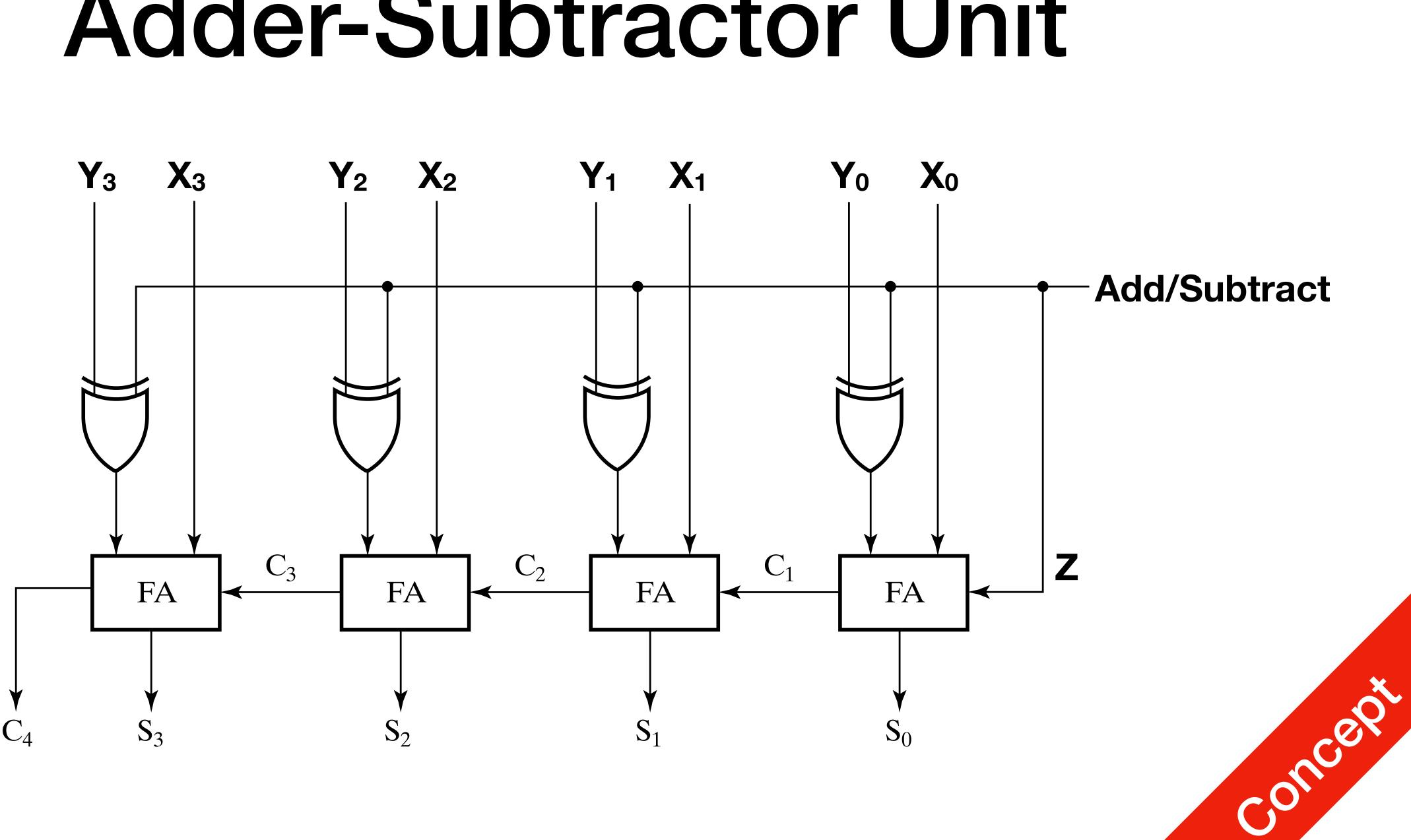

• 1-bit Half Adder

- 1-bit Half Adder

- 1-bit Full Adder using Schema Diagram (Logic Circuit Diagram)

- 1-bit Half Adder

- 1-bit Full Adder using Schema Diagram (Logic Circuit Diagram)

- 4-bit Full Adder using Schema Diagram (Logic Circuit Diagram)

**P4**

VHDL

# Today's Tasks

- 1-bit Half Adder

- 1-bit Full Adder using Schema Diagram (Logic Circuit Diagram)

- 4-bit Full Adder using Schema Diagram (Logic Circuit Diagram)

- 4-bit Adder-Subtractor using Schema Diagram (Logic Circuit Diagram)