# CSCI 150 Introduction to Digital and Computer System Design Lecture 3: Combinational Logic Design IV

Jetic Gū 2020 Fall Semester (S3)

#### Overview

- Focus: Logic Functions

- Architecture: Combinatory Logical Circuits

- Textbook v4: Ch3 3.6, 3.7; v5: Ch3 3.6, 3.7

- Core Ideas:

- 1. Encoder

- 2. Multiplexer

#### Systematic Design Procedures

- **Specification**: Write a specification for the circuit

- 2. **Formulation**: Derive relationship between inputs and outputs of the system e.g. using truth table or Boolean expressions

- 3. **Optimisation**: Apply optimisation, minimise the number of logic gates and literals required

- 4. **Technology Mapping**: Transform design to new diagram using available implementation technology

- 5. **Verification**: Verify the correctness of the final design in meeting the specifications

# Functional Components

- Value-Fixing, Transferring, Inverting, Enabler

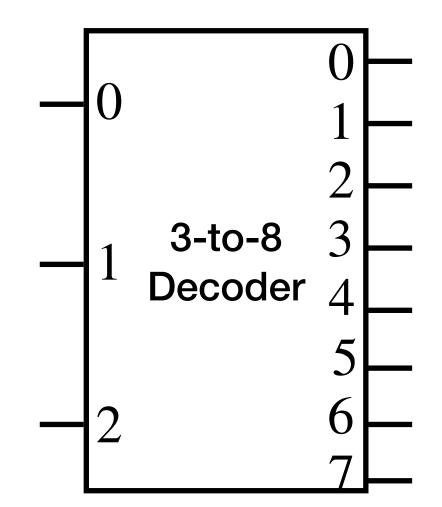

- Decoder

- Input:  $A_0 A_1 ... A_{n-1}$

- Output:  $D_0D_1 ... D_{2^n-1}$ ,  $D_i = m_i$

Wait, didn't we just covered this? Oh, that's decoder

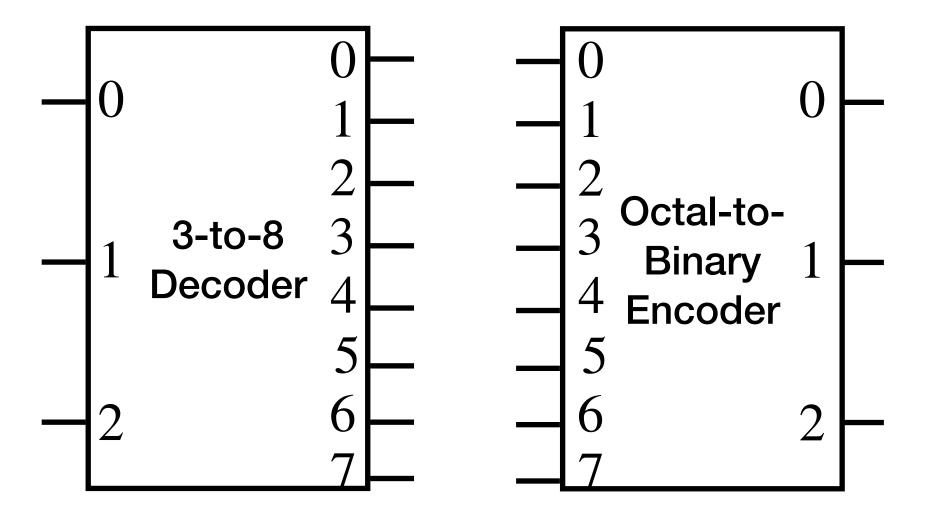

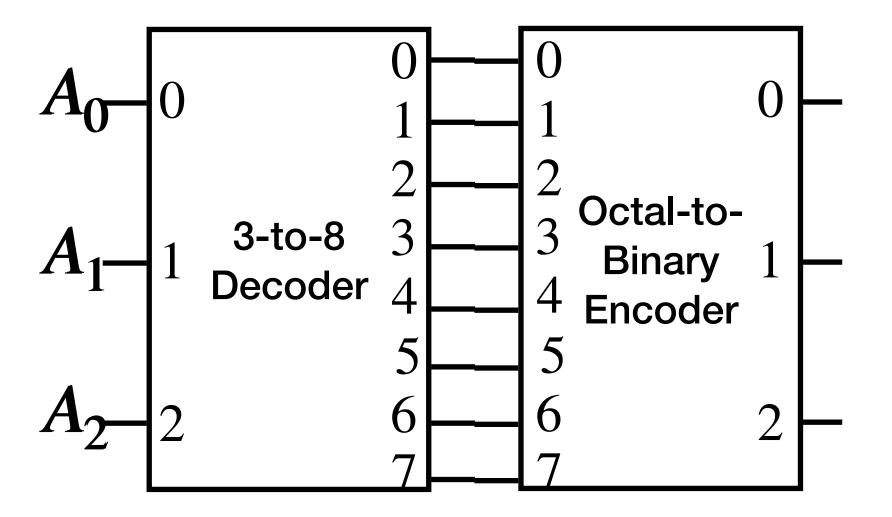

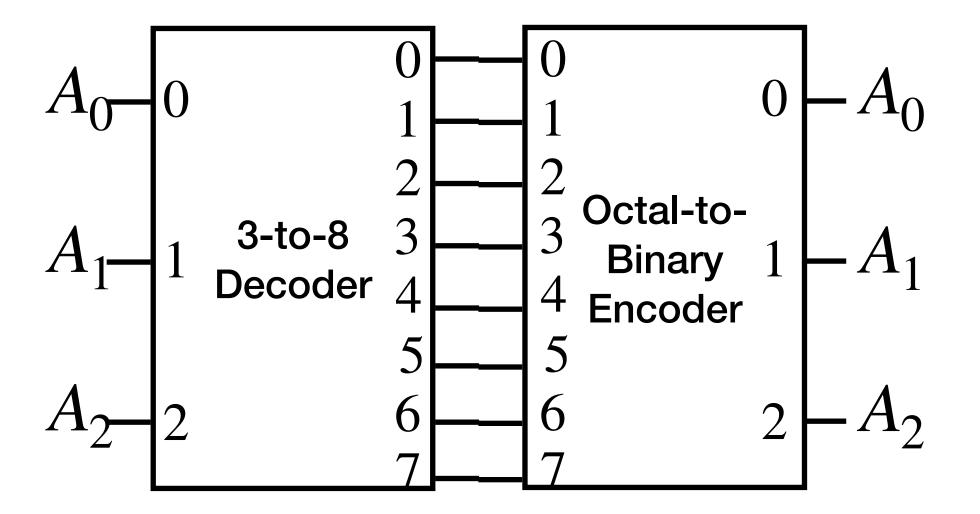

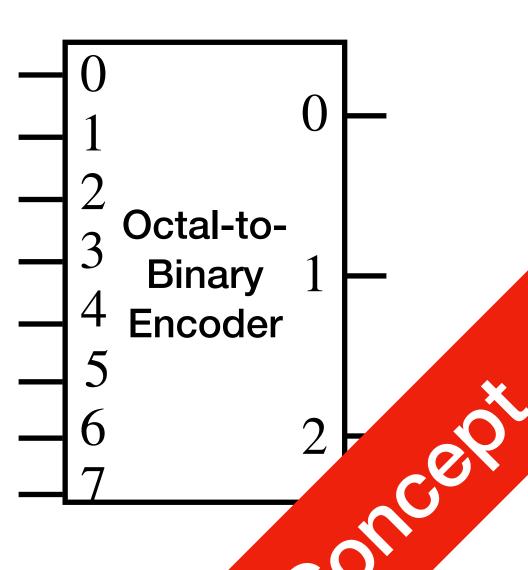

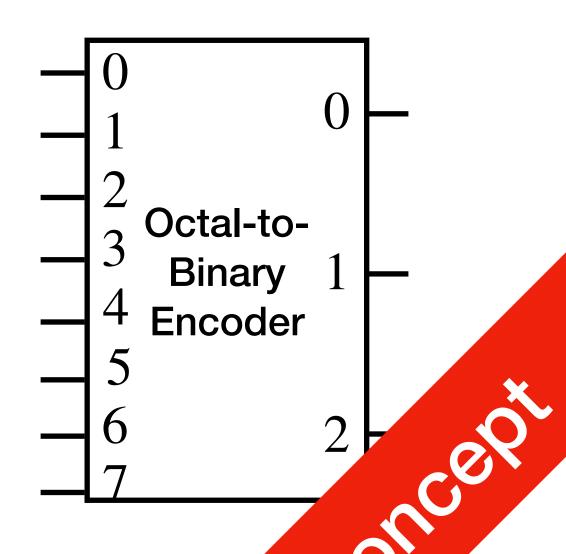

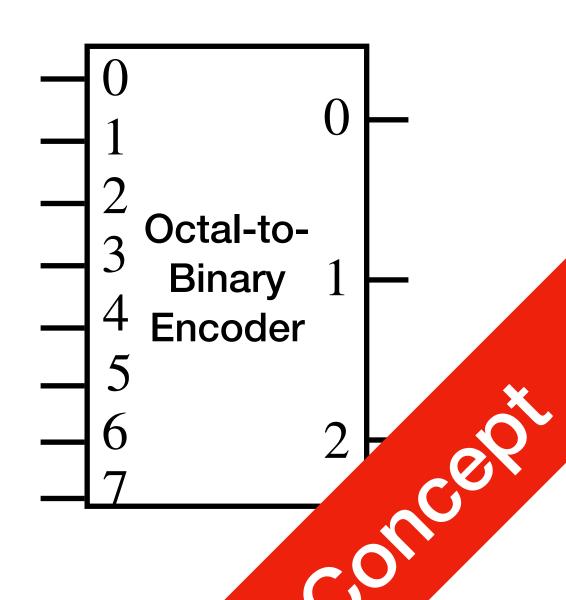

- Inverse operation of a decoder

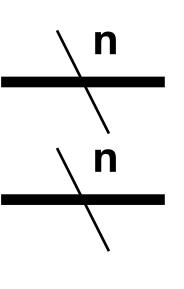

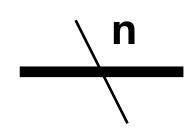

- $2^n$  inputs, only one is giving positive input<sup>1</sup>

- *n* outputs

- Inverse operation of a decoder

- $2^n$  inputs, only one is giving positive input<sup>1</sup>

- *n* outputs

- Inverse operation of a decoder

- $2^n$  inputs, only one is giving positive input<sup>1</sup>

- *n* outputs

| D <sub>7</sub> | D <sub>6</sub> | D <sub>5</sub> | D <sub>4</sub> | D <sub>3</sub> | D <sub>2</sub> | D <sub>1</sub> | D <sub>0</sub> | A <sub>2</sub> | A <sub>1</sub> | A <sub>0</sub> |

|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|

|                |                |                |                |                |                |                | 1              |                |                |                |

|                |                |                |                |                |                | 1              |                | 0              | 0              | 1              |

|                |                |                |                |                | 1              |                |                | 0              | 1              | 0              |

|                |                |                |                | 1              |                |                |                | 0              | 1              | 1              |

|                |                |                | 1              |                |                |                |                | 1              | 0              | 0              |

|                |                | 1              |                |                |                |                |                | 1              | 0              | 1              |

|                | 1              |                |                |                |                |                |                | 1              | 1              | 0              |

| 1              |                |                |                |                |                |                |                | 1              | 1              | 1              |

| D <sub>7</sub> | D <sub>6</sub> | D <sub>5</sub> | D <sub>4</sub> | D <sub>3</sub> | D <sub>2</sub> | D <sub>1</sub> | D <sub>0</sub> | A <sub>2</sub> | A <sub>1</sub> | A <sub>0</sub> |

|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|

|                |                |                |                |                |                |                | 1              | 0              | 0              | 0              |

|                |                |                |                |                |                | 1              |                | 0              | 0              | 1              |

|                |                |                |                |                | 1              |                |                | 0              | 1              | 0              |

|                |                |                |                | 1              |                |                |                | 0              | 1              | 1              |

|                |                |                | 1              |                |                |                |                | 1              | 0              | 0              |

|                |                | 1              |                |                |                |                |                | 1              | 0              | 1              |

|                | 1              |                |                |                |                |                |                | 1              | 1              | 0              |

| 1              |                |                |                |                |                |                |                | 1              | 1              | 1              |

| $A_0 = D_1 + D_3 + D_5 + D_7$ |

|-------------------------------|

| $A_1 = D_2 + D_3 + D_6 + D_7$ |

| $A_2 = D_4 + D_5 + D_6 + D_7$ |

- What happens if the inputs are all 0s?

- What happens if the inputs include multiple 1s?

$$A_0 = D_1 + D_3 + D_5 + D_7$$

$$A_1 = D_2 + D_3 + D_6 + D_7$$

$$A_2 = D_4 + D_5 + D_6 + D_7$$

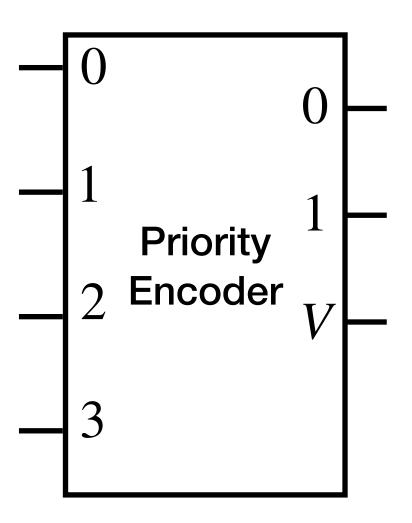

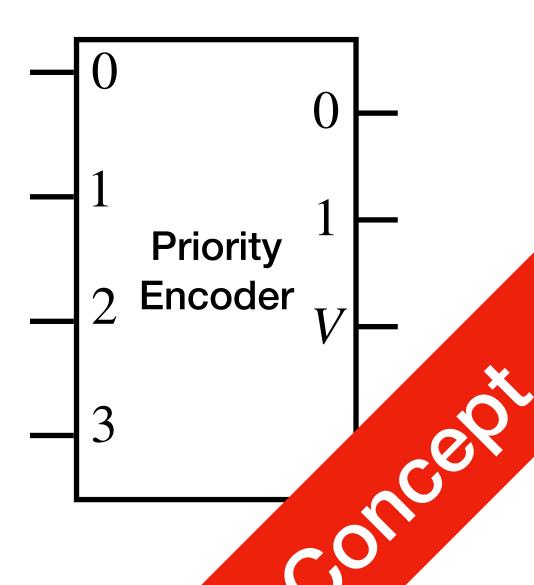

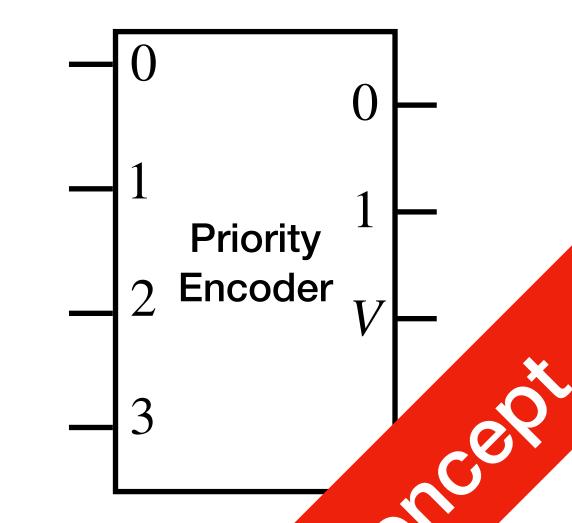

# Priority Encoder

- ullet Additional Validity Output V

- Indicating whether the input is valid (contains 1)

- Priority

- Ignores  $D_{< i}$  if  $D_i = 1$

Coucer

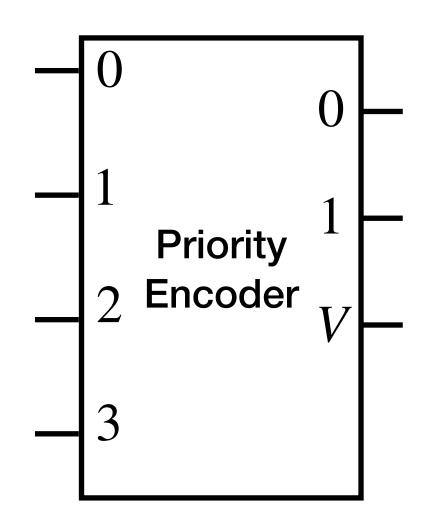

# Priority Encoder

| D <sub>3</sub> | D <sub>2</sub> | D <sub>1</sub> | D <sub>0</sub> | A <sub>1</sub> | A <sub>0</sub> | V |

|----------------|----------------|----------------|----------------|----------------|----------------|---|

| 0              | 0              | 0              | 0              | X              | X              | 0 |

| 0              | 0              | 0              | 1              | 0              | 0              | 1 |

| 0              | 0              | 1              | X              | 0              | 1              | 1 |

| 0              | 1              | X              | X              | 1              | 0              | 1 |

| 1              | X              | X              | X              | 1              | 1              | 1 |

# Priority Encoder

| D <sub>3</sub> | D <sub>2</sub> | D <sub>1</sub> | D <sub>0</sub> | A <sub>1</sub> | A <sub>0</sub> | V |

|----------------|----------------|----------------|----------------|----------------|----------------|---|

| 0              | 0              | 0              | 0              | X              | X              | 0 |

| 0              | 0              | 0              | 1              | 0              | 0              | 1 |

| 0              | 0              | 1              | X              | 0              | 1              | 1 |

| 0              | 1              | X              | X              | 1              | 0              | 1 |

| 1              | X              | X              | X              | 1              | 1              | 1 |

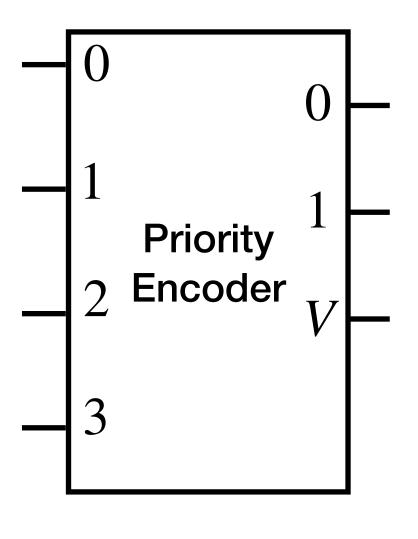

# Priority Encoder

| D <sub>3</sub> | D <sub>2</sub> | D <sub>1</sub> | D <sub>0</sub> | A <sub>1</sub> | Ao | V |

|----------------|----------------|----------------|----------------|----------------|----|---|

| 0              | 0              | 0              | 0              | X              | X  | 0 |

| 0              | 0              | 0              | 1              | 0              | 0  | 1 |

| 0              | 0              | 1              | X              | 0              | 1  | 1 |

| 0              | 1              |                | X              | 1              | 0  | 1 |

| 1              | X              | X              | X              | 1              | 1  | 1 |

COUCEL

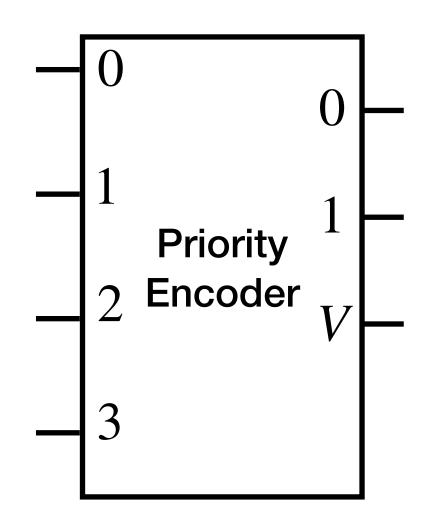

# Priority Encoder

| D <sub>3</sub> | D <sub>2</sub> | D <sub>1</sub> | D <sub>0</sub> | A <sub>1</sub> | A <sub>0</sub> | V |

|----------------|----------------|----------------|----------------|----------------|----------------|---|

| 0              | 0              | 0              | 0              | 0              | 0              | 0 |

| 0              | 0              | 0              | 1              | 0              | 0              | 1 |

| 0              | 0              | 1              | X              | 0              | 1              | 1 |

| 0              | 1              | X              | X              | 1              | 0              | 1 |

| 1              | X              | X              | X              | 1              | 1              | 1 |

# Priority Encoder

| D <sub>3</sub> | D <sub>2</sub> | D <sub>1</sub> | D <sub>0</sub> | A <sub>1</sub> | A <sub>0</sub> | V |

|----------------|----------------|----------------|----------------|----------------|----------------|---|

| 0              | 0              | 0              | 0              | 0              | 0              | 0 |

| 0              | 0              | 0              | 1              | 0              | 0              | 1 |

| 0              | 0              | 1              | X              | 0              | 1              | 1 |

| 0              | 1              | X              | X              | 1              | 0              | 1 |

| 1              | X              | X              | X              | 1              | 1              | 1 |

$$V = D_3 + D_2 + D_1 + D_0$$

$$A_1 = D_3 + \overline{D_3}D_2 = D_2 + D_3$$

$$A_0 = \overline{D_3}\overline{D_2}D_1 + D_3$$

$$= \overline{D_2}D_1 + D_3$$

Switch Modes

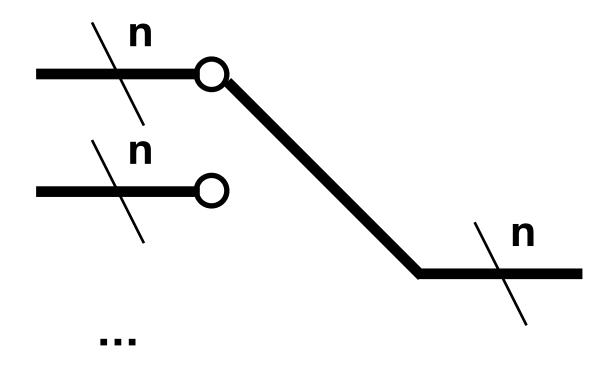

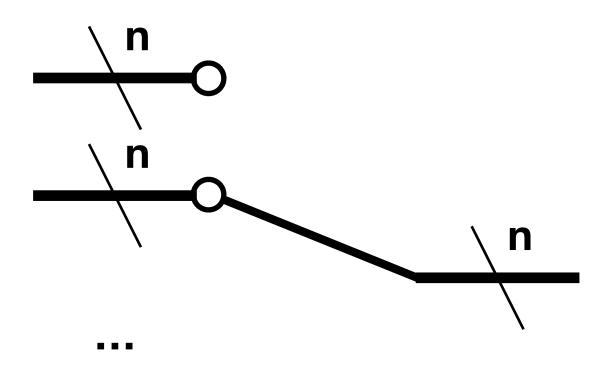

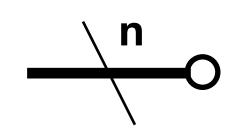

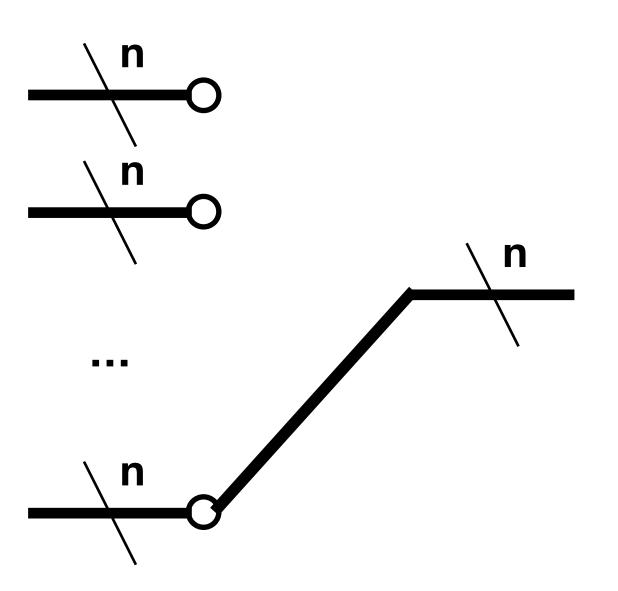

- Multiple *n*-variable input vectors

- Single *n*-variable output vector

- Switches: which input vectors to output

- Multiple *n*-variable input vectors

- Single n-variable output vector

- Switches: which input vectors to output

---

- Multiple *n*-variable input vectors

- Single n-variable output vector

- Switches: which input vectors to output

- Multiple *n*-variable input vectors

- Single n-variable output vector

- Switches: which input vectors to output

$$\frac{n}{}$$

- Multiple *n*-variable input vectors

- Single *n*-variable output vector

- Switches: which input vectors to output

- Multiple *n*-variable input vectors

- Single *n*-variable output vector

- Switches: which input vectors to output

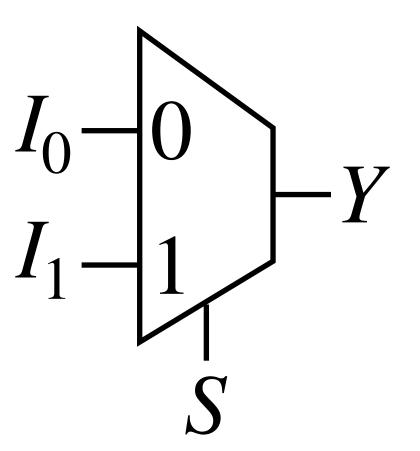

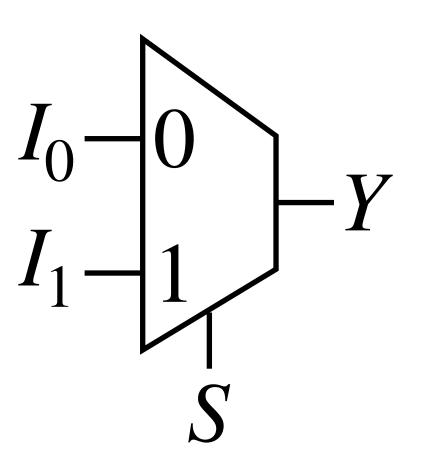

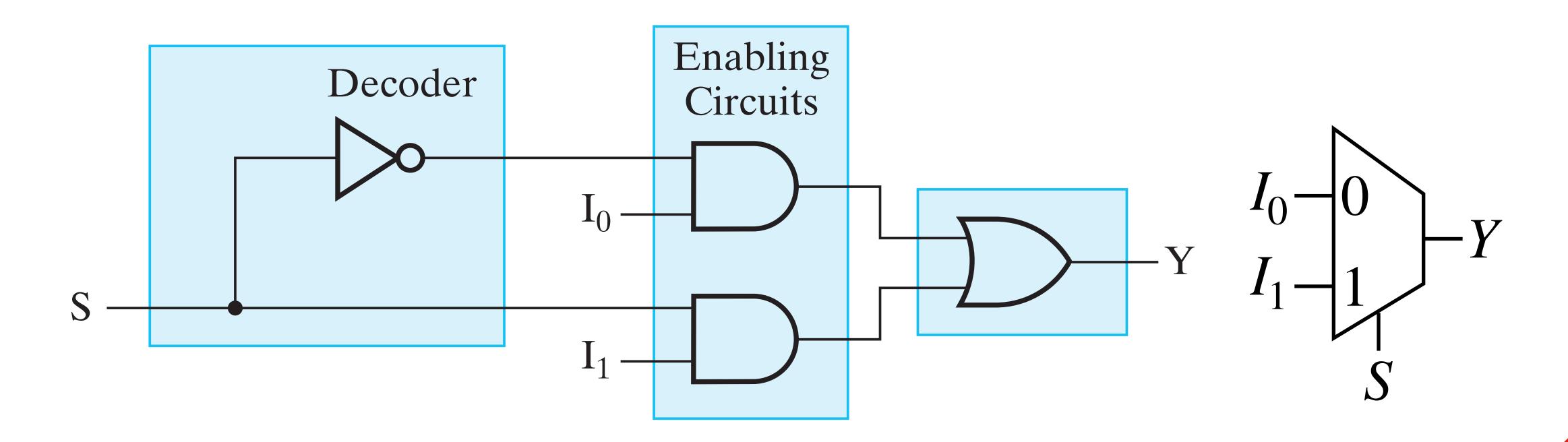

# Single-Bit 2-to-1 Multiplexer

- 2 single-bit inputs

- 1 single-bit output

- 1-bit switch

# Single-Bit 2-to-1 Multiplexer

| S | lo | I <sub>1</sub> | Y |

|---|----|----------------|---|

|   | 0  | X              | 0 |

| 0 | 1  | X              | 1 |

| 1 | X  | 0              | 0 |

| 1 | X  | 1              | 1 |

# Single-Bit 2-to-1 Multiplexer

Technology

- 1 x 1-to-2 Decoder

- 2 x 1-bit Enabler

- 1 x 2-input OR Gate

Cocc

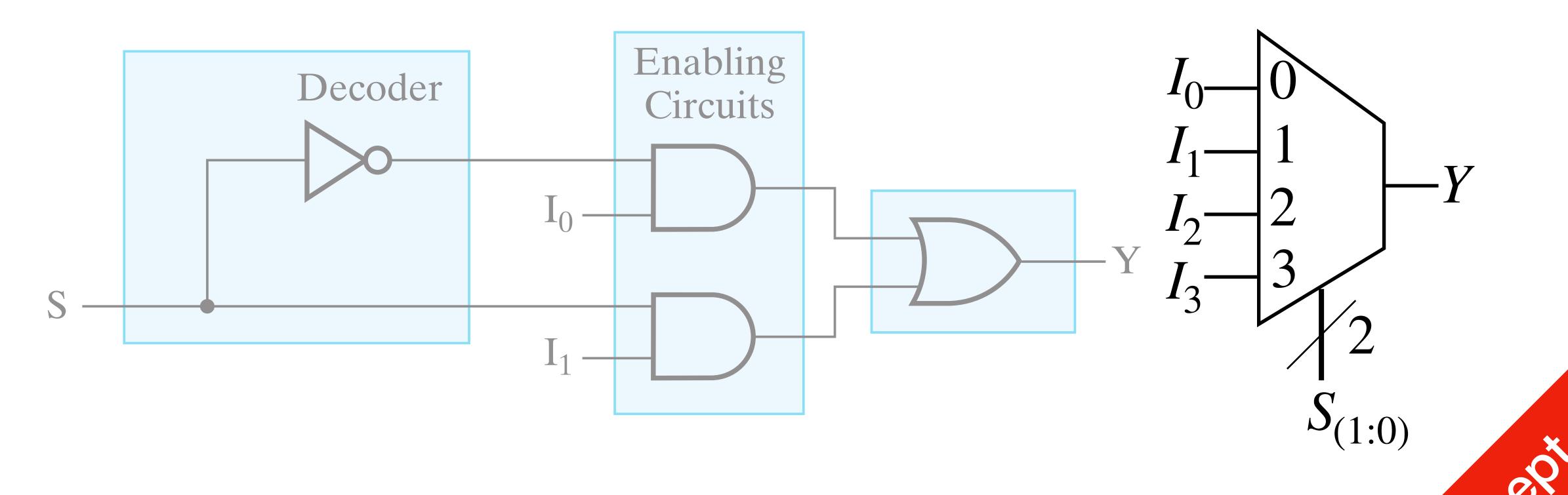

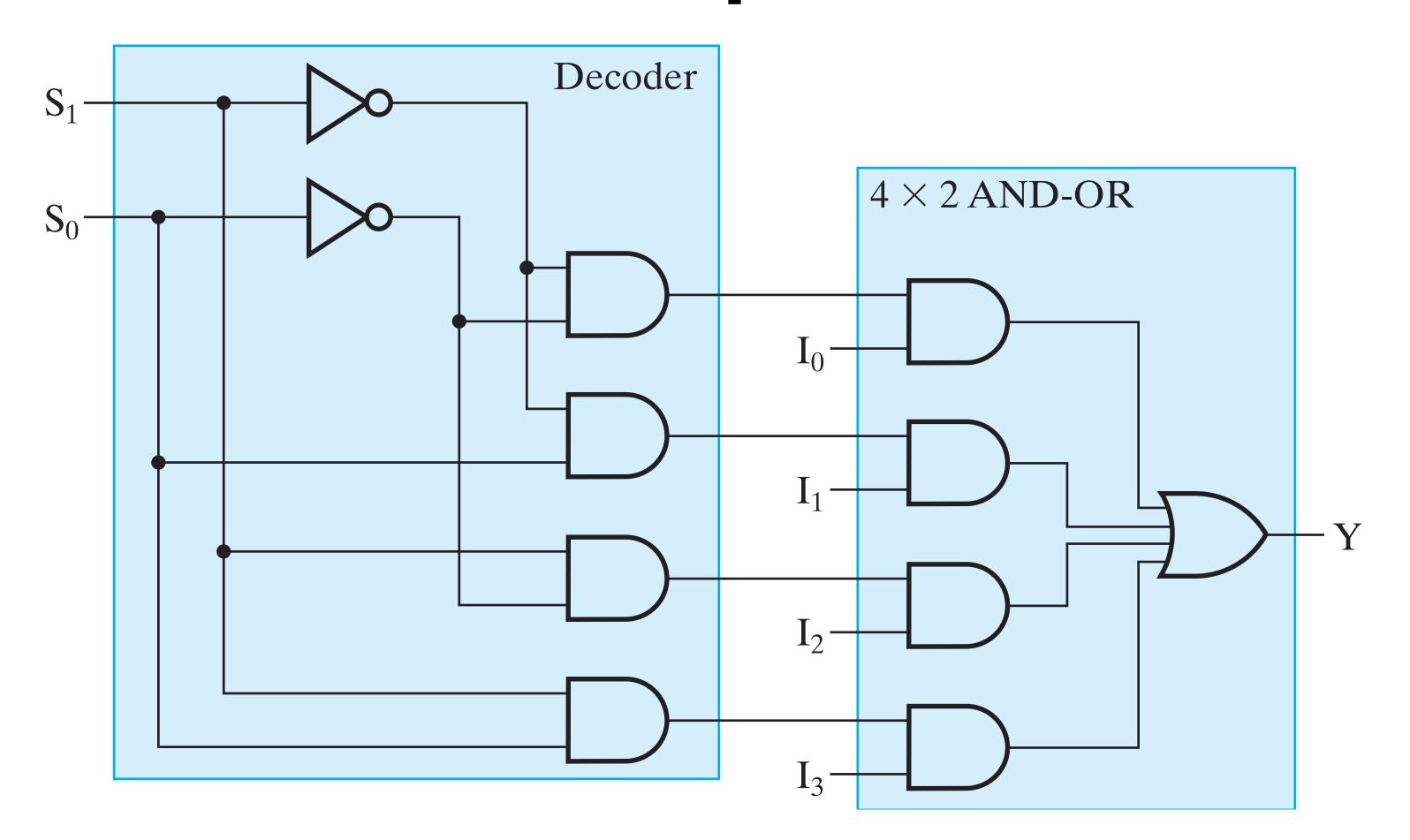

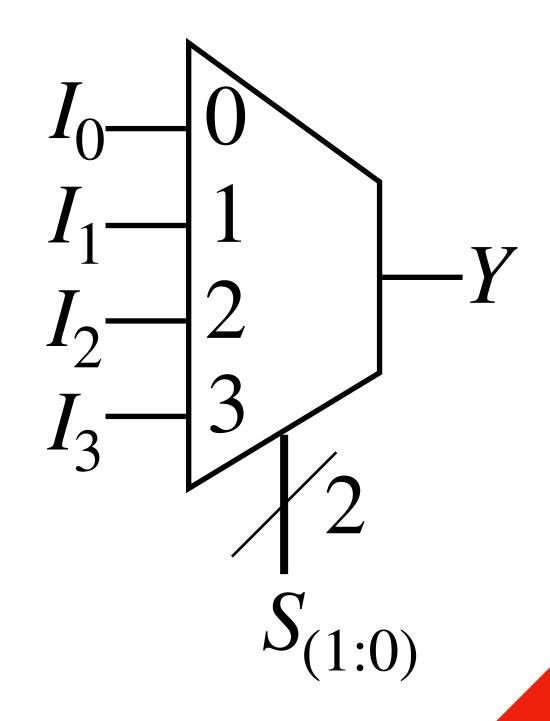

# Single-Bit 4-to-1 Multiplexer

Technology

- 1 x 2-to-4 Decoder

- 4 x 1-bit Enabler

- 1 x 4-input OR Gate

CORC

# Single-Bit 4-to-1 Multiplexer

#### Technology

- 1 x 2-to-4 Decoder

- 4 x 1-bit Enabler

- 1 x 4-input OR Gate

Course

# Circuit Drawing Time!

It's OK, this is the last time...

Sorta...

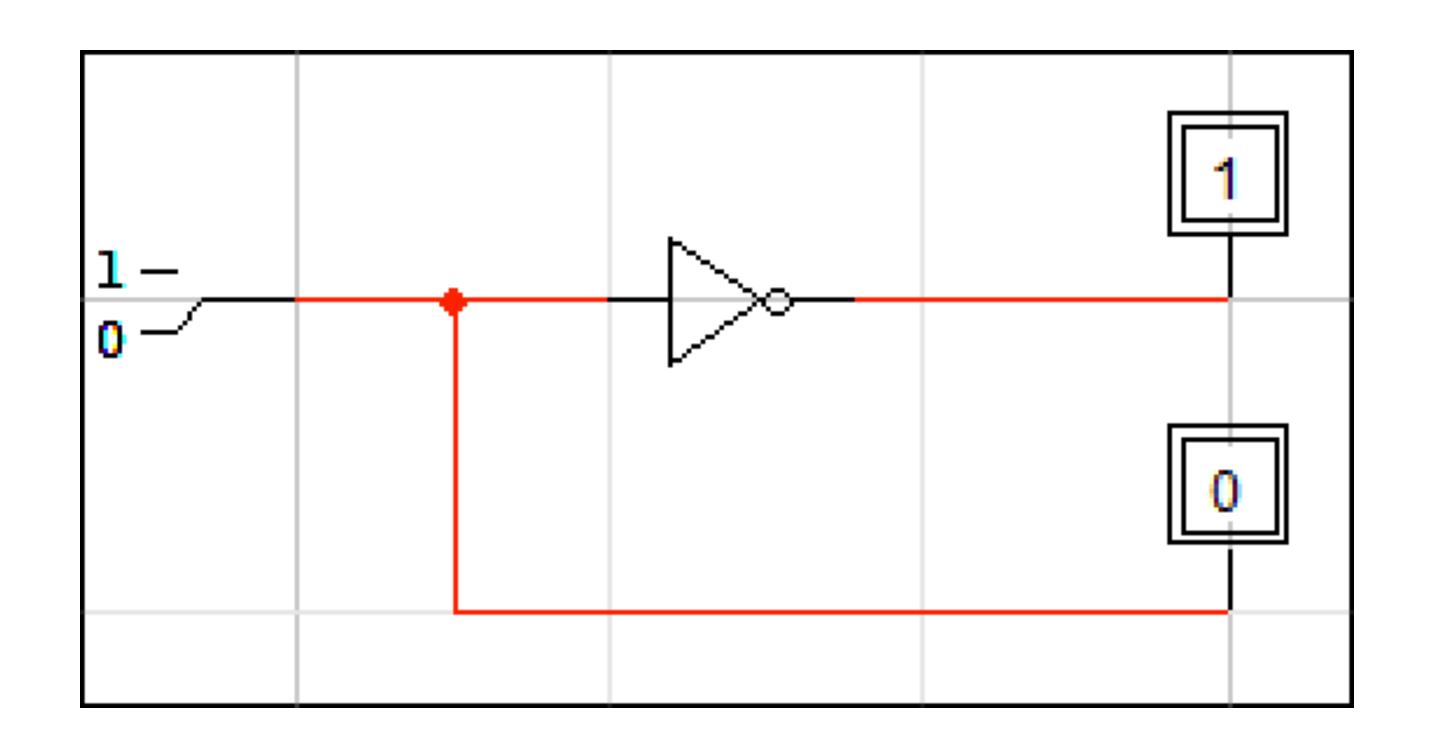

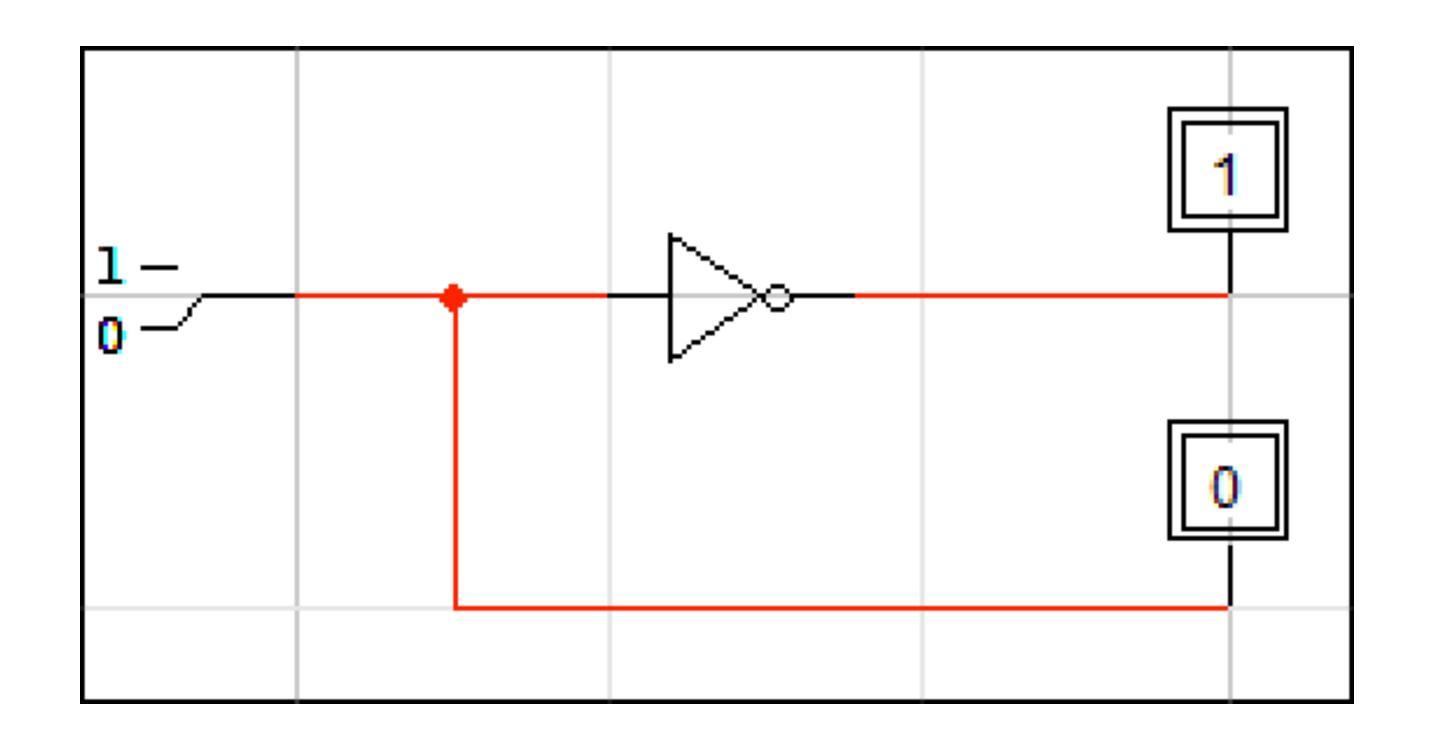

### Last Circuit Drawing Practice

- 1. Sub-circuit

- 2. Implementing 2-to-4 Decoder using drawing tools

- 3. Implementing 3-to-8 Decoder using 2-to-4 Decoders

- 4. Implementing Octal-to-Binary Priority Encoder using drawing tools<sup>1</sup>

- 5. Implementing Multiplexer using drawing tools<sup>1</sup>

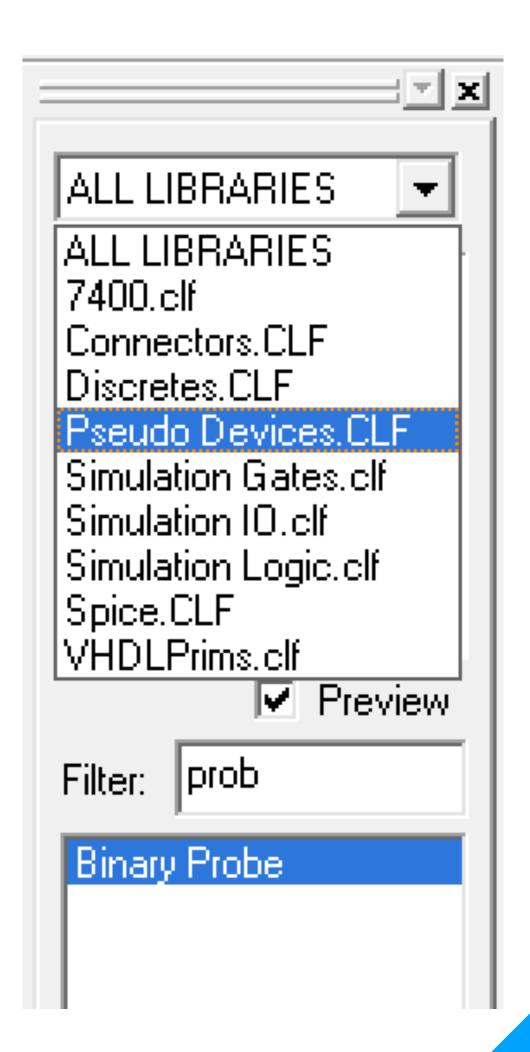

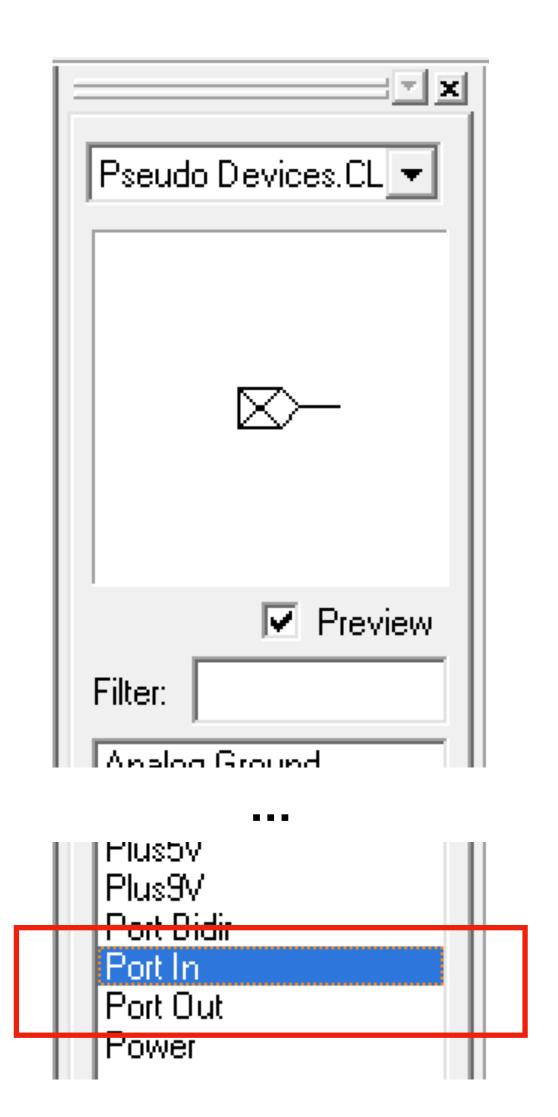

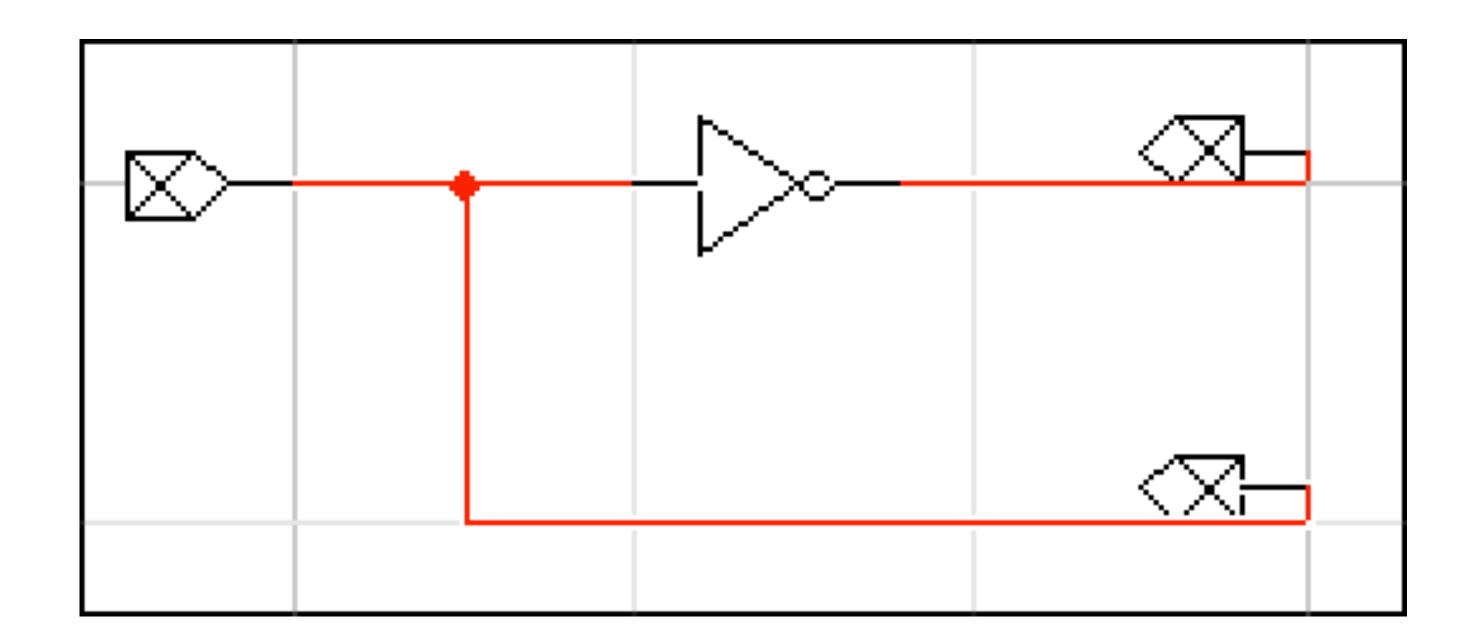

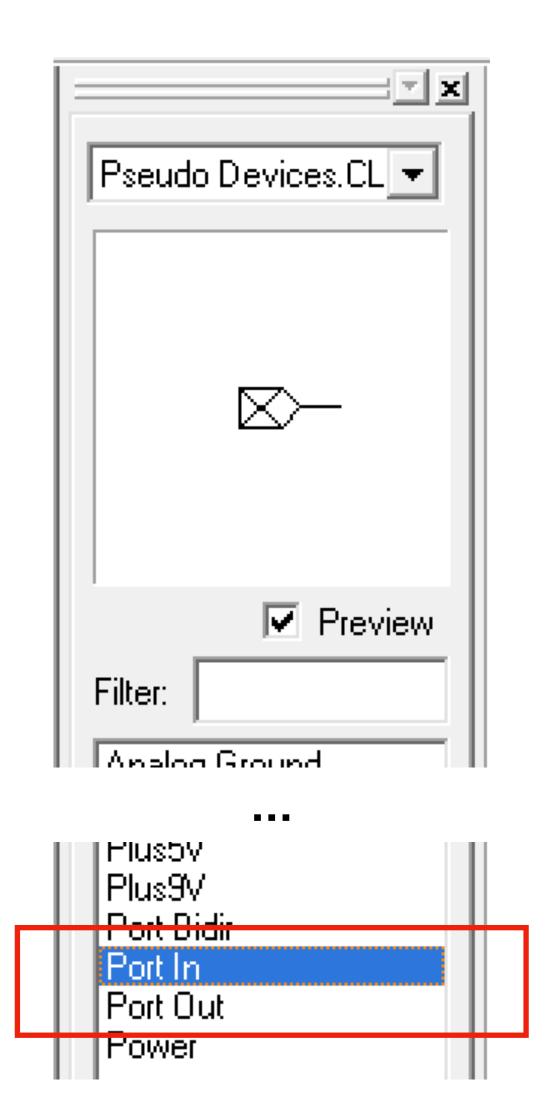

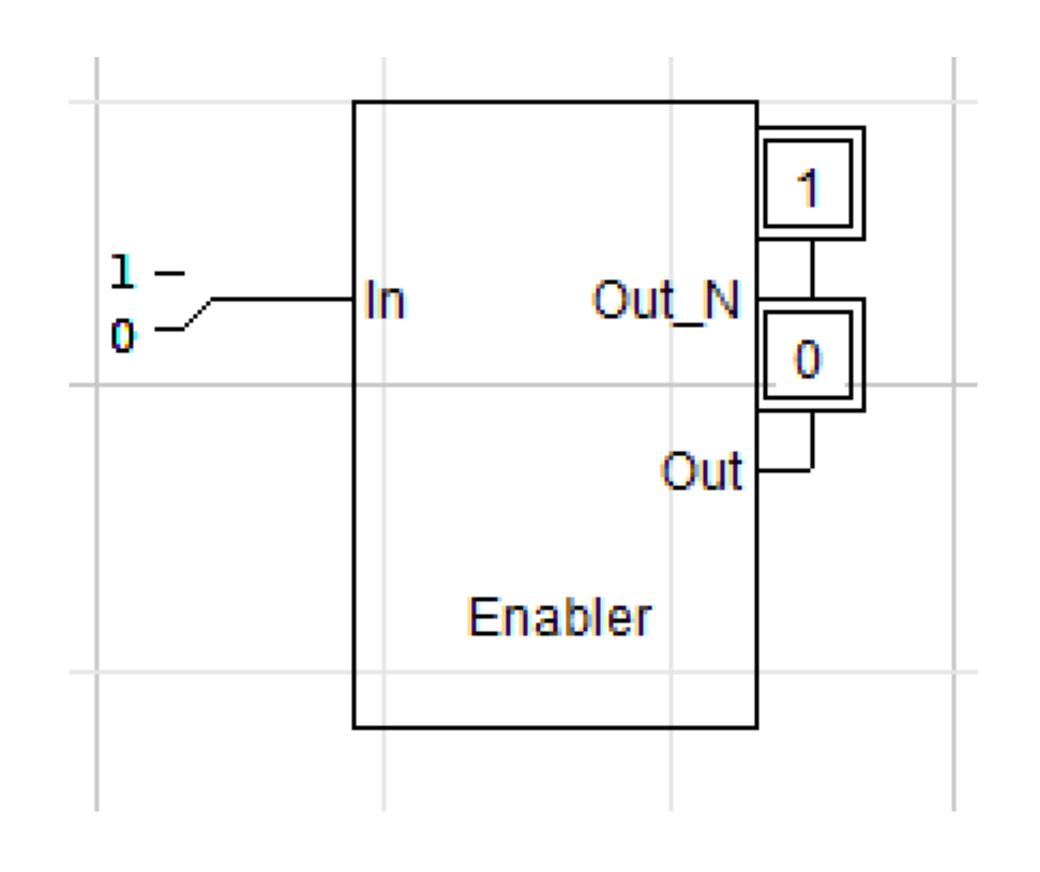

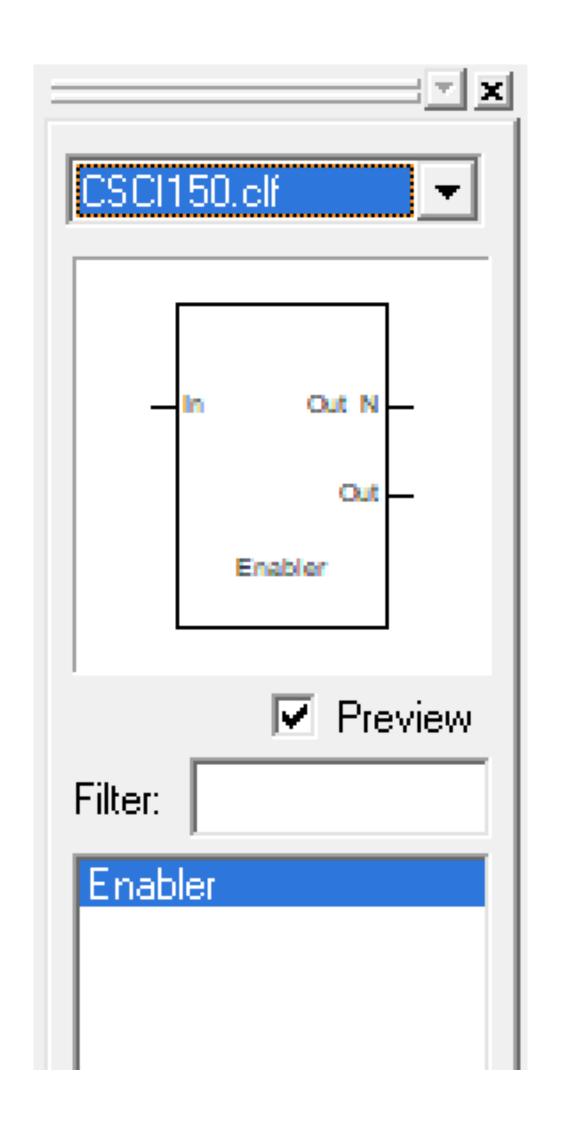

1. Implement an enabler, then select the Pseudo Devices library

Y 6 C

CCI

Chilico

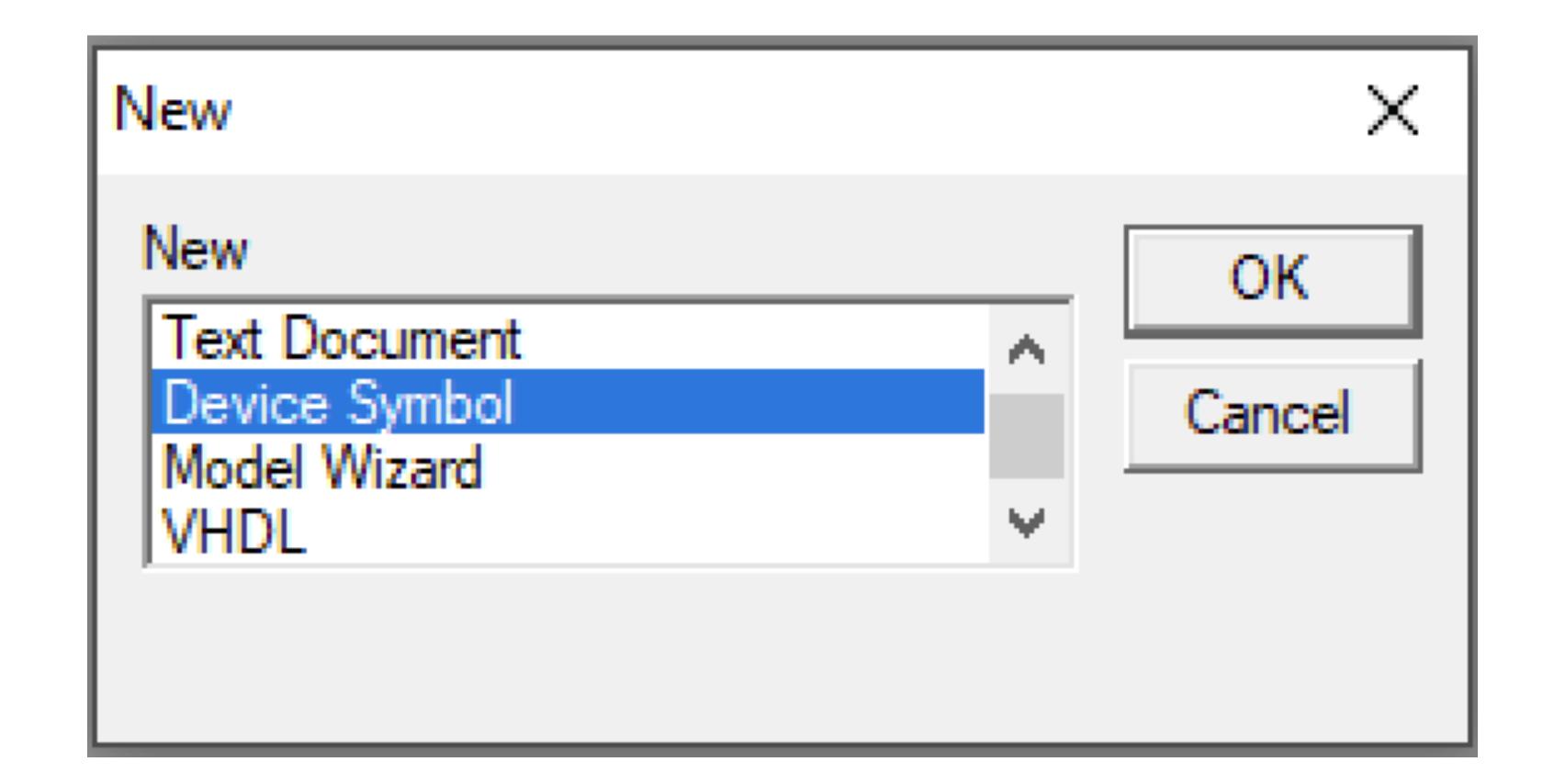

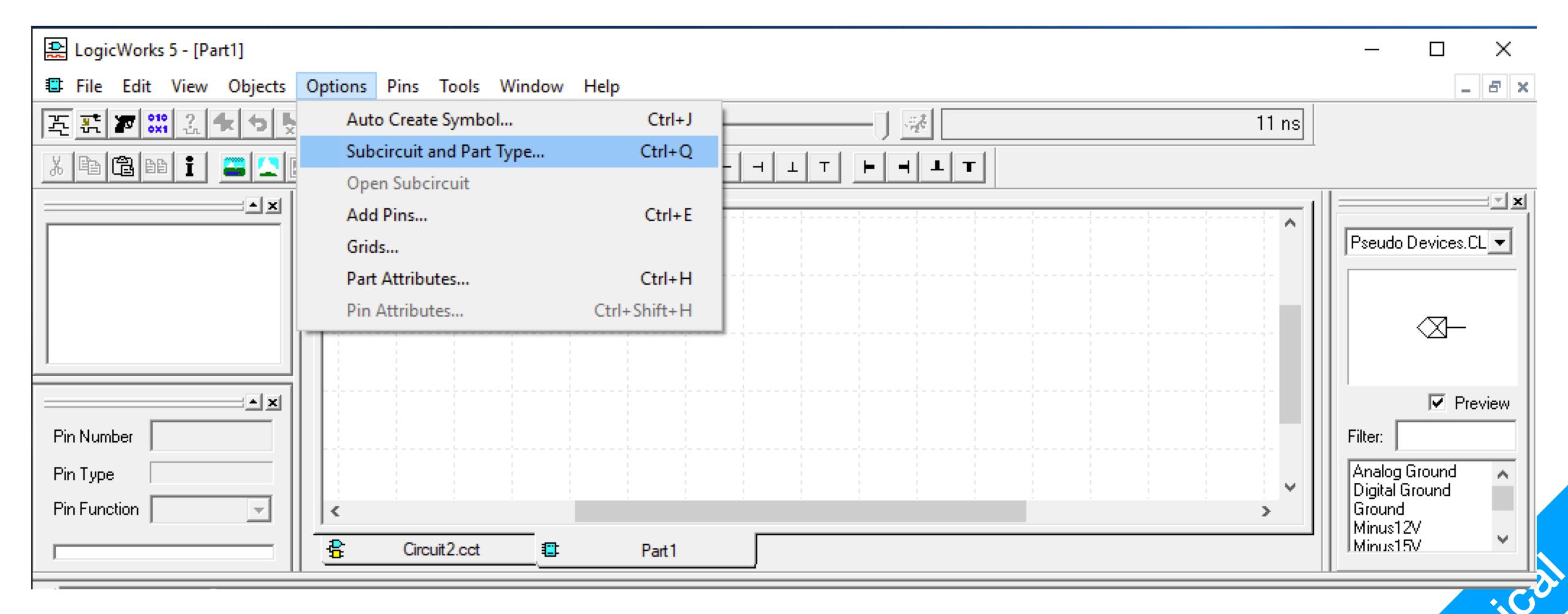

4. With the Circuit.cct open and Part1 open, go to Options - Subcircuit and Part Type

| Part Type                                                                                                                                                  | X |

|------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

| Primitive Type  Create a subcircuit symbol, but don't store a circuit with it yet.  Create a subcircuit symbol and select an open circuit to attach to it. |   |

| C Imp Select Internal Circuit X  Set Circuit2.cct  Ot                                                                                                      |   |

| Subcircu  Del  Loc  OK  Cancel                                                                                                                             |   |

| Messages Done Cancel                                                                                                                                       |   |

5. Select Create a subcircuit symbol and select an open circuit to attach to it

| Part Type                                                                                                                                                      | × |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

| Primitive Type  C Create a subcircuit symbol, but don't store a circuit with it yet.  C Create a subcircuit symbol and select an open circuit to attach to it. |   |

| C Imp Select Internal Circuit X  C Set Circuit2.cct                                                                                                            |   |

| Subcircu  Del  OK Cancel  Brow                                                                                                                                 |   |

| Messages Done  Cancel                                                                                                                                          |   |

Yeculi Co.

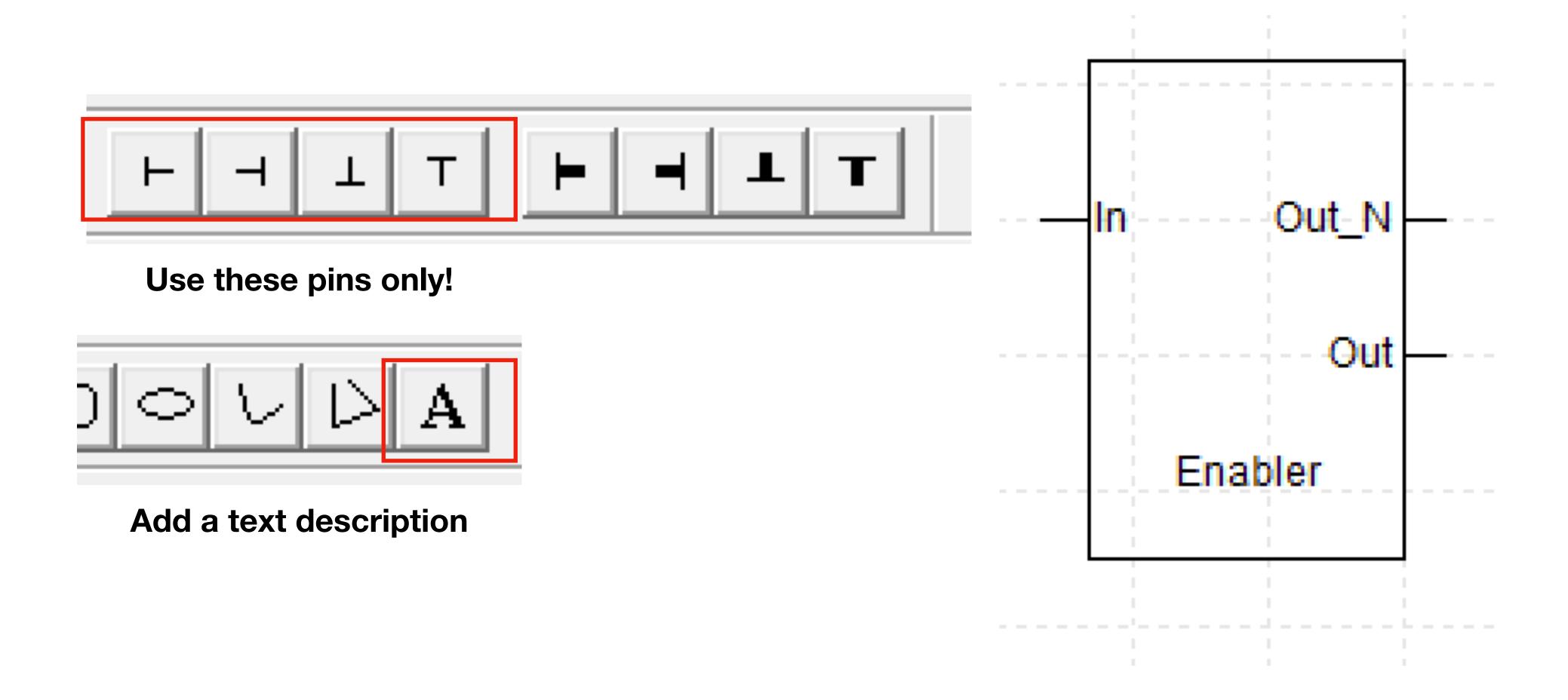

7. Draw a rectangle and add the THIN pins

Chilico

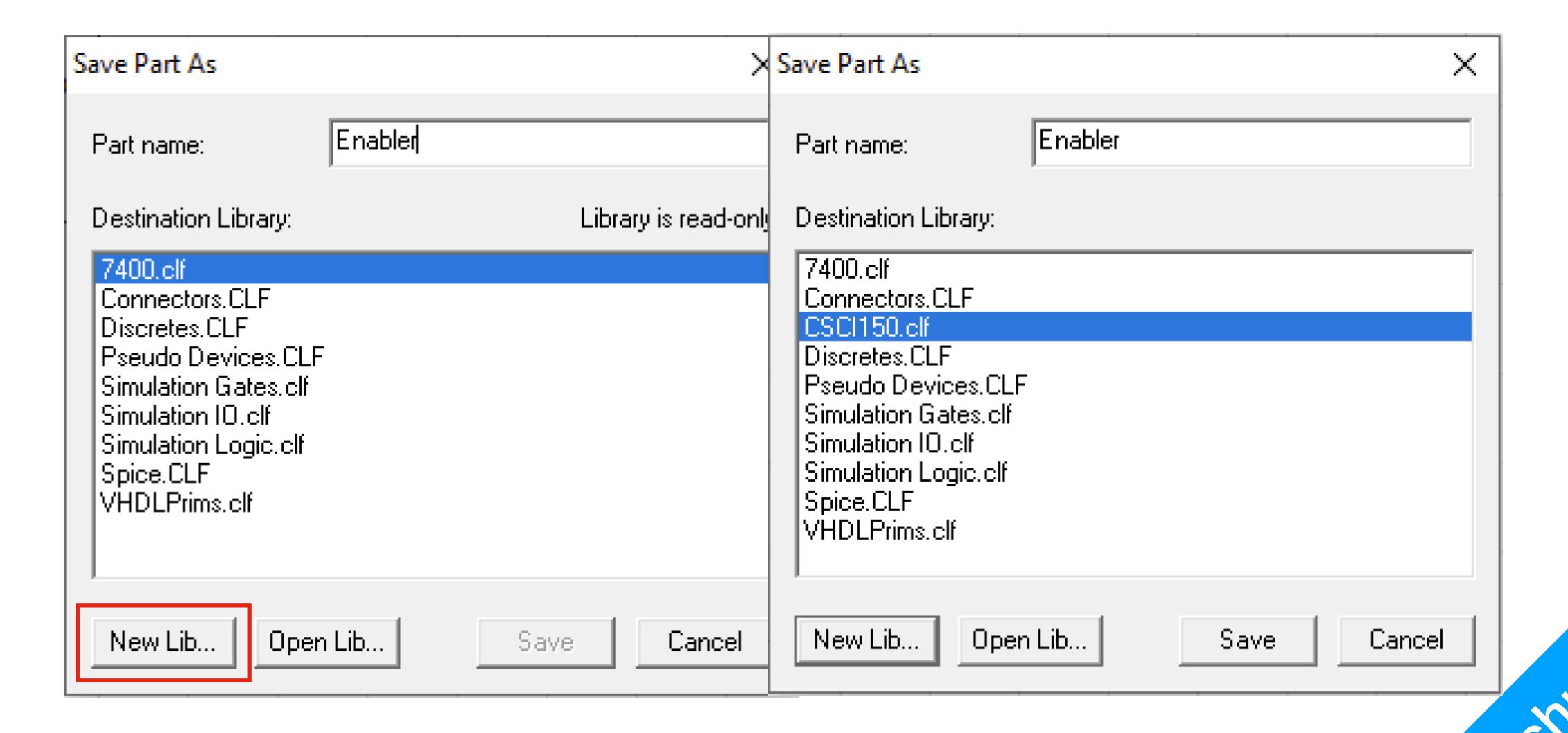

8. Save the part in a new library, e.g. CSCI150

Signature of the second second

## Last Circuit Drawing Practice

- 1. Sub-circuit

- 2. Implementing 2-to-4 Decoder using drawing tools

- 3. Implementing 3-to-8 Decoder using 2-to-4 Decoders

- 4. Implementing Octal-to-Binary Priority Encoder using drawing tools<sup>1</sup>

- 5. Implementing Multiplexer using drawing tools<sup>1</sup>