## CSCI 150 Introduction to Digital and Computer System Design Lecture 4: Sequential Circuit V

Jetic Gū 2020 Summer Semester (S2)

## Overview

- Focus: Basic Information Retaining Blocks

- Architecture: Sequential Circuit

- Textbook v4: Ch5 5.5, 5.6; v5: Ch4 4.5

- Core Ideas:

- 1. Sequential Circuit Design Procedures

- 2. Other Flip-Flop Types

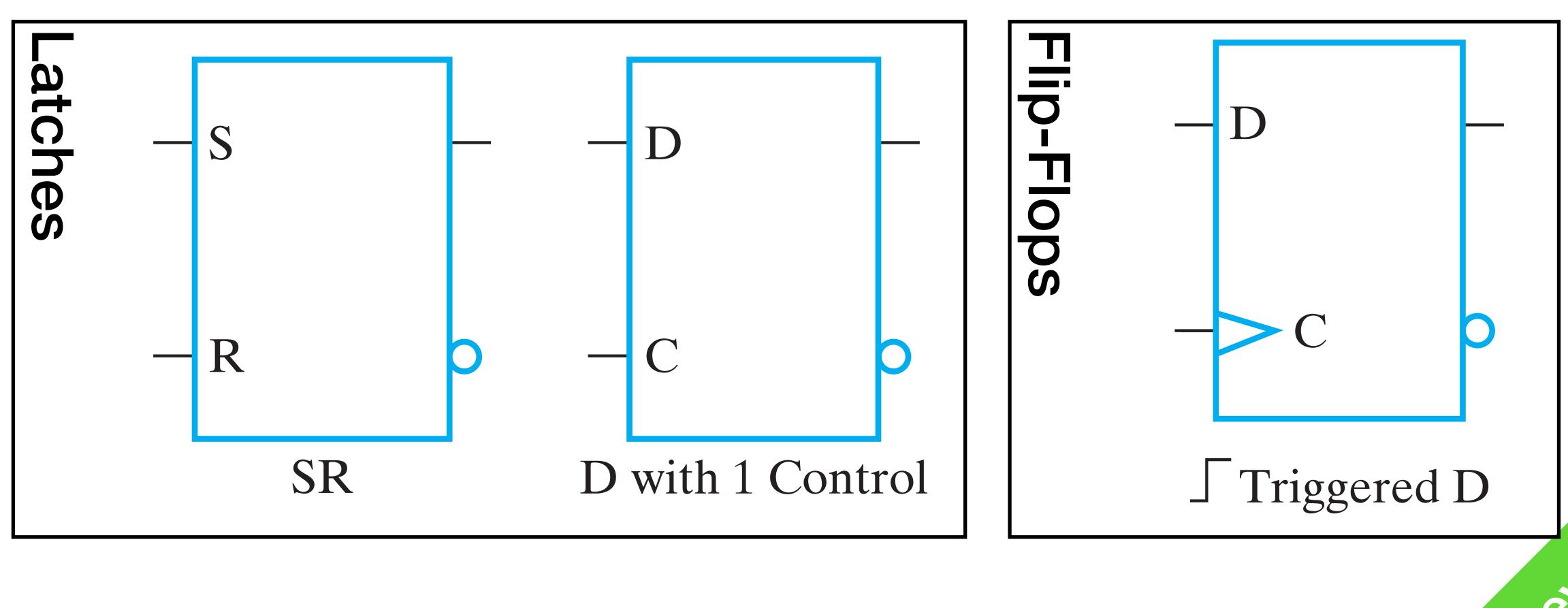

# Latches and Flip-Flops

### Systematic Design Procedures **P**0 Review Sequential Circuits

- **Specification**

- 2. Formulation e.g. using state table or state diagram

- 3. State Assignment: assign binary codes to states

- entries

- **Output Equation Determination:** Derive output equations from the output entries 5.

- **Optimisation** 6.

- 7. Technology Mapping

- 8. Verification

4. Flip-Flop Input Equation Determination: Select flip-flop types, derive input equations from next-state

# Sequential Circuit Design II

State Assignment; Input Equation Determination; Output Equation Determination

### Systematic Design Procedures **P1** Design Sequential Circuits

- **Specification**

- 2. Formulation e.g. using state table or state diagram

- 3. State Assignment: assign binary codes to states

- entries

- **Output Equation Determination:** Derive output equations from the output entries 5.

- **Optimisation** 6.

- 7. Technology Mapping

- 8. Verification

4. Flip-Flop Input Equation Determination: Select flip-flop types, derive input equations from next-state

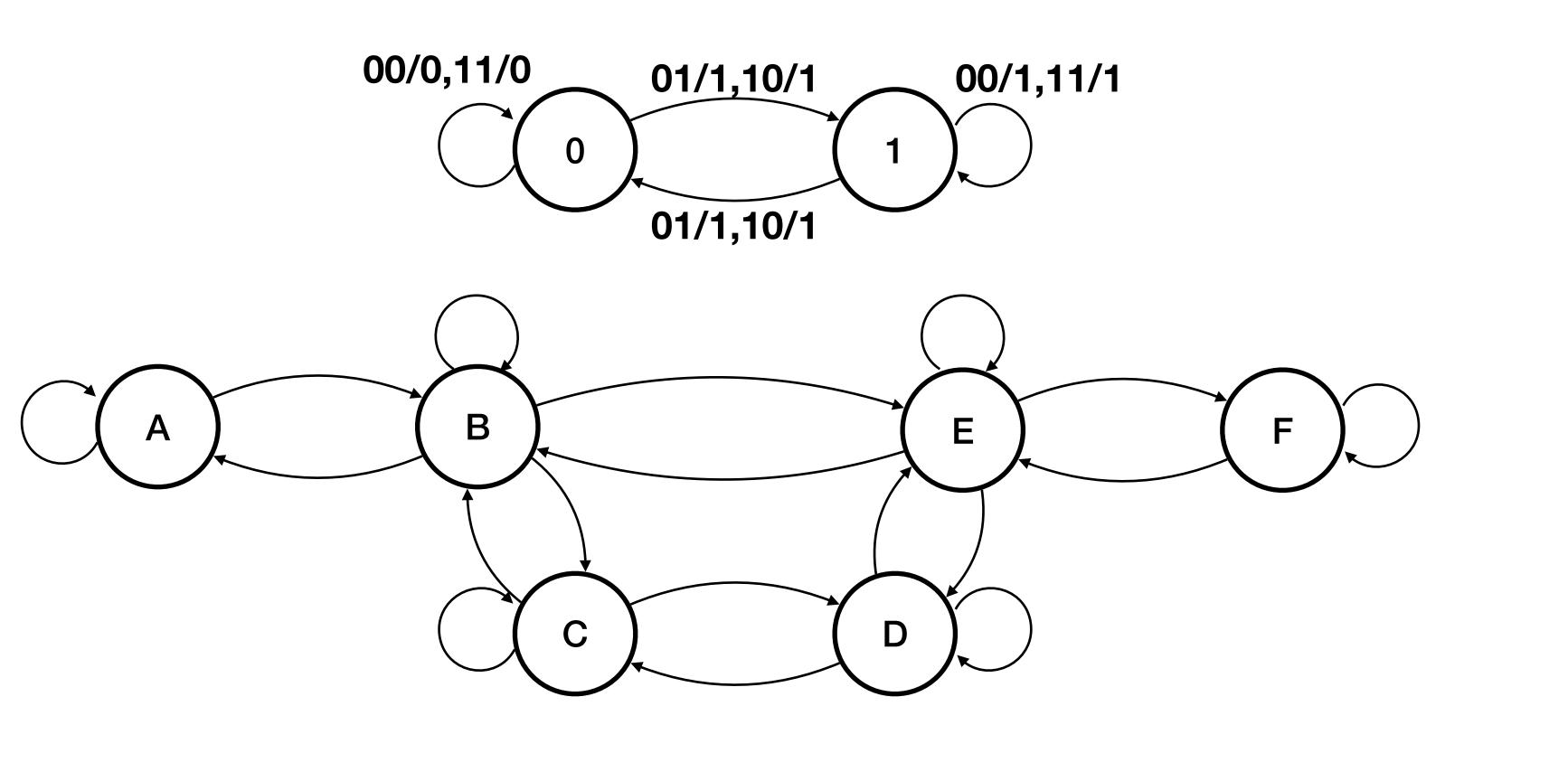

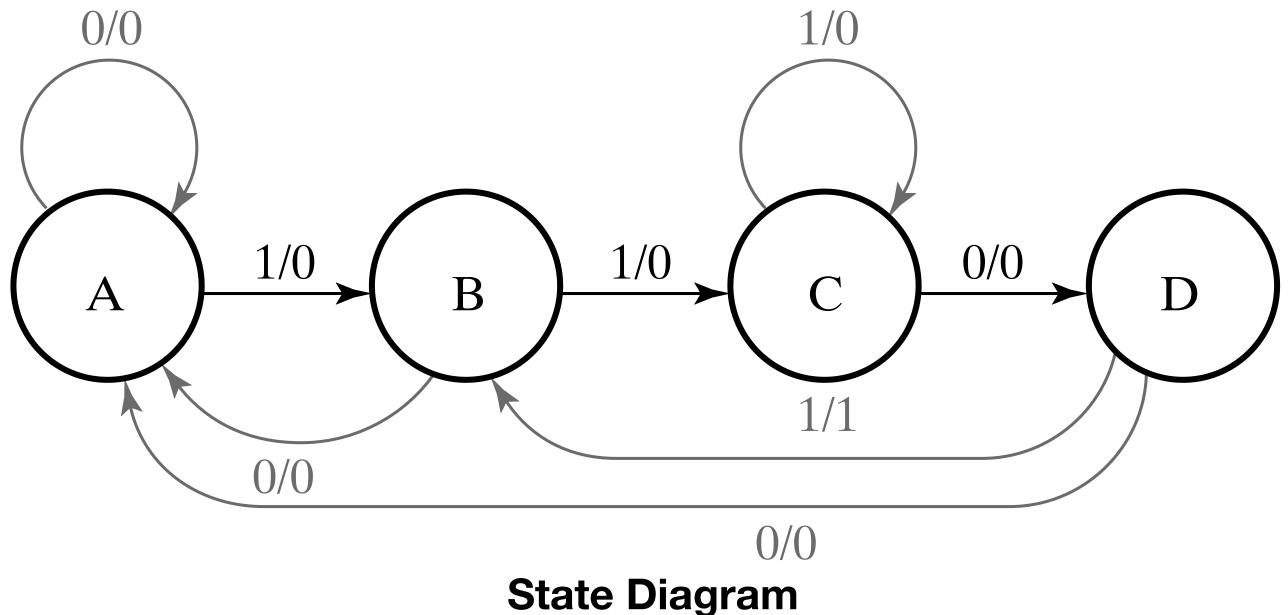

# 2. Formulation

Sometimes it is more intuitive to describe state transitions then defining the states

# 2. Formulation

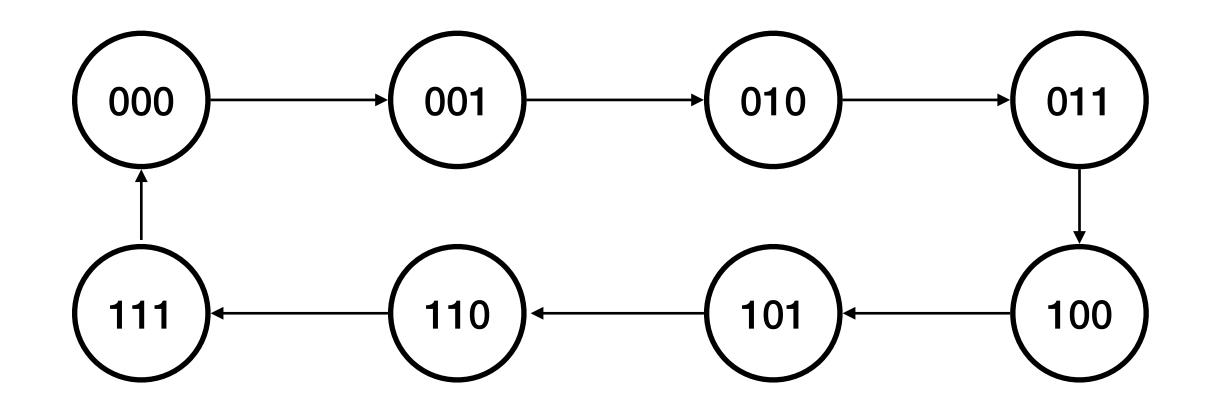

• Incrementer: perform +1 operation every CLK on 3-bit

- Used when states are quite complicated and expressed using variables during Formulation

- Define the **binary values** for each state  $\bullet$

- Used when states are quite complicated and expressed using variables during Formulation

- Define the **binary values** for each state

| Present<br>State | Next State          |           | Output Z            |              |

|------------------|---------------------|-----------|---------------------|--------------|

|                  | <b>X</b> = <b>0</b> | X = 1     | <b>X</b> = <b>0</b> | <b>X</b> = 1 |

| A                | A                   | B         | 0                   | 0            |

| B                | A                   | C         | 0                   | 0            |

| С                | D                   | C         | 0                   | 0            |

| D                | A                   | B         | 0                   | 1            |

|                  | Sta                 | ite Table |                     | I            |

• Method 1: sequential assignment  $A = 0, B = 1, C = 2, D = 3, \dots$

**P1**

Design

| Droopt           | Next                | State | Output Z            |       |

|------------------|---------------------|-------|---------------------|-------|

| Present<br>State | <b>X</b> = <b>0</b> | X = 1 | <b>X</b> = <b>0</b> | X = 1 |

| A <b>00</b>      | <b>00</b> A         | B 01  | 0                   | 0     |

| B <b>01</b>      | <b>00</b> A         | C 10  | 0                   | 0     |

| C 10             | <b>11</b> D         | C 10  | 0                   | 0     |

| D 11             | <b>00</b> A         | B 01  | 0                   | 1     |

|                  |                     |       |                     |       |

**State Table**

### • Method 2: one hot $A = (0001)_2, B = (0010)_2, C = (0100)_2, D = (1000)_2$

|                  | Next State          |        | Output Z            |       |

|------------------|---------------------|--------|---------------------|-------|

| Present<br>State | <b>X</b> = <b>0</b> | X = 1  | <b>X</b> = <b>0</b> | X = 1 |

| A 0001           | <b>0001</b> A       | B 0010 | 0                   | 0     |

| B 0010           | <b>0001</b> A       | C 0100 | 0                   | 0     |

| C 0100           | <b>1000</b> D       | C 0100 | 0                   | 0     |

| D <b>1000</b>    | <b>0001</b> A       | B 0010 | 0                   | 1     |

|                  |                     |        |                     |       |

**State Table**

- Are these the only methods?

- No, there's tons

- Are these methods equivalent?

- For this course, we don't require you to come up with the best state assignment solution

No, they each lead to completely different solutions, with different costs

- Are we using all of the combinations?

- No. Some states are not designed to be reachable

- Could also be used in the future for extensions

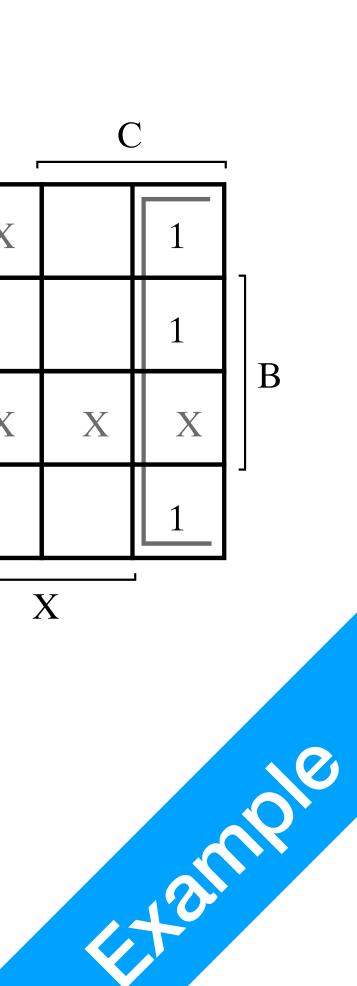

## 4. Flip-Flop Input Expressions **P1** 5. Output Expressions Design

- Express all Flip-Flops using input variables

- Express all outputs using variables and Flip-Flop outputs

| $D_1 D_0$ for next state |      |

|--------------------------|------|

| $S_1 S_0$ for present    | Pres |

|                          |      |

sent State  $S_1S_0$

- A **00**

- B **01**

- C 10

- D 11

| Next                | State $D_1 D_0$ | Outp                | Output Z |  |  |

|---------------------|-----------------|---------------------|----------|--|--|

| <b>X</b> = <b>0</b> | X = 1           | <b>X</b> = <b>0</b> | X = 1    |  |  |

| <b>00</b> A         | B 01            | 0                   | 0        |  |  |

| <b>00</b> A         | C 10            | 0                   | 0        |  |  |

| <b>11</b> D         | C 10            | 0                   | 0        |  |  |

| <b>00</b> A         | B 01            | 0                   | 1        |  |  |

|                     |                 |                     |          |  |  |

## 4. Flip-Flop Input Expressions **P1** 5. Output Expressions Design

- Express all Flip-Flops using input variables

- Express all outputs using variables and Flip-Flop outputs

$D_1 D_0$  for next state  $S_1S_0$  for present

$D_1 = F_1(X, S_1, S_0) = \Sigma m(2, 5, 6)$  $D_0 = F_0(X, S_1, S_0) = \Sigma m(2, 4, 7)$

$Z = m_{7}$

| X | $S_1 S_0$ | $D_1 D_0$ | Ζ |

|---|-----------|-----------|---|

| 0 | 00        | 00        | 0 |

| 0 | 01        | 00        | 0 |

| 0 | 10        | 11        | 0 |

| 0 | 11        | 00        | 0 |

| 1 | 00        | 01        | 0 |

| 1 | 01        | 10        | 0 |

| 1 | 10        | 10        | 0 |

| 1 | 11        | 01        | 1 |

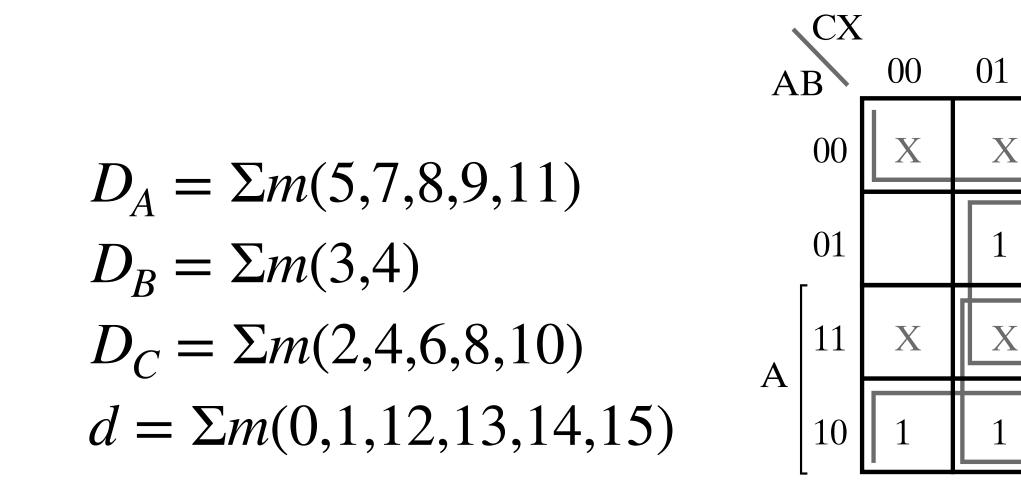

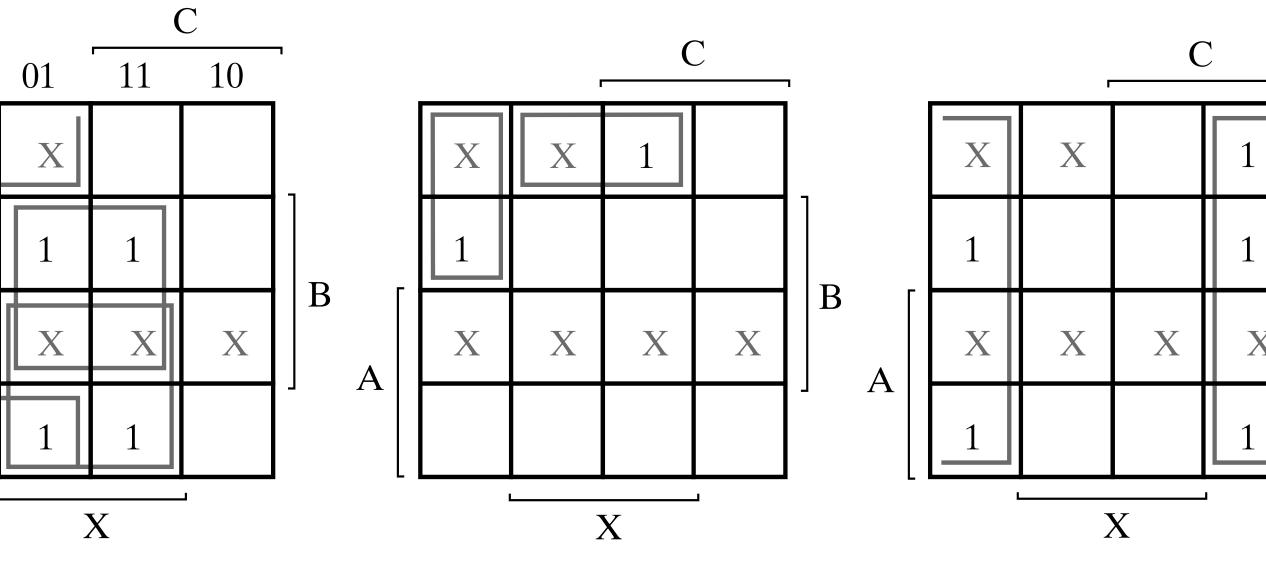

## 6. Optimisation with Unused States

• Unused states can be implemented as don't care conditions

**P1**

Design

• In this example  $m_0, m_1, m_{12}, m_{13}, m_{14}, m_{15}$ are unused, and can all be don't care conditions

$$D_A = \Sigma m(5,7,8,9,11)$$

$$D_B = \Sigma m(3,4)$$

$$D_C = \Sigma m(2,4,6,8,10)$$

$$d = \Sigma m(0,1,12,13,14,15)$$

| Pre | sent S | State | Input | Nex | xt Sta | ate |

|-----|--------|-------|-------|-----|--------|-----|

| Α   | В      | С     | X     | Α   | В      | С   |

| 0   | 0      | 1     | 0     | 0   | 0      | 1   |

| 0   | 0      | 1     | 1     | 0   | 1      | 0   |

| 0   | 1      | 0     | 0     | 0   | 1      | 1   |

| 0   | 1      | 0     | 1     | 1   | 0      | 0   |

| 0   | 1      | 1     | 0     | 0   | 0      | 1   |

| 0   | 1      | 1     | 1     | 1   | 0      | 0   |

| 1   | 0      | 0     | 0     | 1   | 0      | 1   |

| 1   | 0      | 0     | 1     | 1   | 0      | 0   |

| 1   | 0      | 1     | 0     | 0   | 0      | 1   |

| 1   | 0      | 1     | 1     | 1   | 0      | 0   |

## 6. Optimisation with Unused States

**P1**

Design

### Systematic Design Procedures **P1** Design Sequential Circuits

- **Specification**

- 2. Formulation e.g. using state table or state diagram

- 3. State Assignment: assign binary codes to states

- entries

- **Output Equation Determination:** Derive output equations from the output entries 5.

- **Optimisation** 6.

- 7. Technology Mapping

- 8. Verification

4. Flip-Flop Input Equation Determination: Select flip-flop types, derive input equations from next-state

# Summary

- 3. State Assignment: assign binary codes to states

- 4. Flip-Flop Input Equation Determination: Select flip-flop types, derive input equations from next-state entries

- 5. Output Equation Determination: Derive output equations from the output entries

- **Optimisation with unused states** 6.

P2 Other Flip-Flop

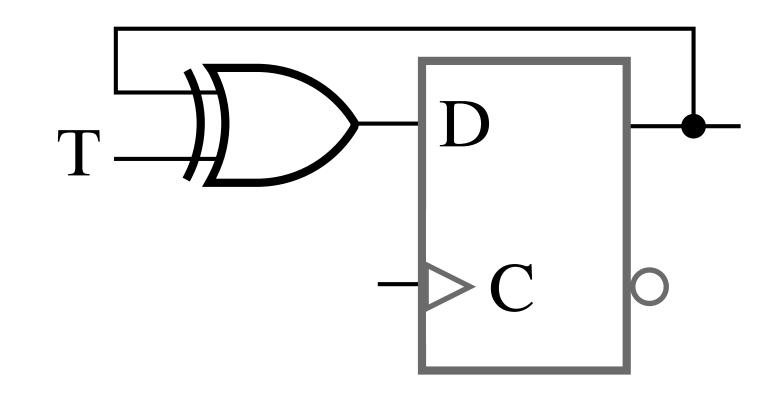

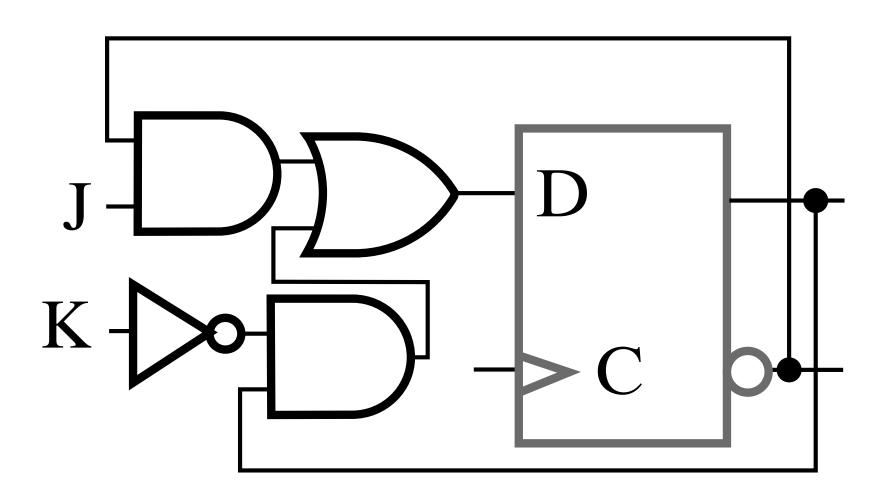

## Some Other Flip-Flop Types JK Flip-Flop; T Flip-Flop

Conditional Inverter

| T | Q(t + 1)          | Operation  |

|---|-------------------|------------|

| 0 | Q(t)              | No change  |

| 1 | $\overline{Q}(t)$ | Complement |

- Follow 8 step design principles

- Write down the boolean expression

- Draw the circuit diagram

| ] | Γ | Q(t + 1)          | Operation  |

|---|---|-------------------|------------|

| ( | ) | Q(t)              | No change  |

| ] |   | $\overline{Q}(t)$ | Complement |

- 3. State Assignment

- 4. Flip-Flop Input Equation

- 5. Output Equation Determination

- 6. Optimisation

- 7. Technology Mapping

| T | Q(t + 1)          | Operation  |

|---|-------------------|------------|

| 0 | Q(t)              | No change  |

| 1 | $\overline{Q}(t)$ | Complement |

- 3. State Assignment

- 4. Flip-Flop Input Equation  $Q(t+1) = Q \oplus T$

- 5. Output Equation Determination

- Optimisation 6.

- Technology Mapping 7.

| T | Q(t + 1)          | Operation  |

|---|-------------------|------------|

| 0 | Q(t)              | No change  |

| 1 | $\overline{Q}(t)$ | Complement |

- 3. State Assignment

- 4. Flip-Flop Input Equation  $Q(t+1) = Q \oplus T$

- 5. Output Equation Determination

- Optimisation 6.

- Technology Mapping 7.

| T | Q(t + 1)          | Operation  |

|---|-------------------|------------|

| 0 | Q(t)              | No change  |

| 1 | $\overline{Q}(t)$ | Complement |

• Similar to *SR* Master-Slave Flip-Flop with 11 input inverting internal value

Operation J Q(t+1)K 0 Q(t)No change 0 0 0 Reset 1 1 0 Set  $\overline{Q}(t)$ 1 Complement 1

- Follow 8 step design principles

- Write down the boolean expression

- Draw the circuit diagram

| J | K | Q(t + 1)          | Operation  |

|---|---|-------------------|------------|

| 0 | 0 | Q(t)              | No change  |

| 0 | 1 | 0                 | Reset      |

| 1 | 0 | 1                 | Set        |

| 1 | 1 | $\overline{Q}(t)$ | Complement |

- 3. State Assignment

- 4. Flip-Flop Input Equation

- 5. Output Equation Determination

- 6. Optimisation

- 7. Technology Mapping

| J | K | Q(t + 1)          | Operation  |

|---|---|-------------------|------------|

| 0 | 0 | Q(t)              | No change  |

| 0 | 1 | 0                 | Reset      |

| 1 | 0 | 1                 | Set        |

| 1 | 1 | $\overline{Q}(t)$ | Complement |

- 3. State Assignment

- 4. Flip-Flop Input Equation  $Q(t+1) = J \cdot \overline{Q} + \overline{K} \cdot Q$

- 5. Output Equation Determination

- 6. Optimisation

- 7. Technology Mapping

| J | K | Q(t + 1)          | Operation  |

|---|---|-------------------|------------|

| 0 | 0 | Q(t)              | No change  |

| 0 | 1 | 0                 | Reset      |

| 1 | 0 | 1                 | Set        |

| 1 | 1 | $\overline{Q}(t)$ | Complement |

- 3. State Assignment

- 4. Flip-Flop Input Equation  $Q(t+1) = J \cdot \overline{Q} + \overline{K} \cdot Q$

- 5. Output Equation Determination

- 6. Optimisation

- 7. Technology Mapping

| J | K | <b>Q(t + 1)</b>   | Operation  |

|---|---|-------------------|------------|

| 0 | 0 | Q(t)              | No change  |

| 0 | 1 | 0                 | Reset      |

| 1 | 0 | 1                 | Set        |

| 1 | 1 | $\overline{Q}(t)$ | Complement |

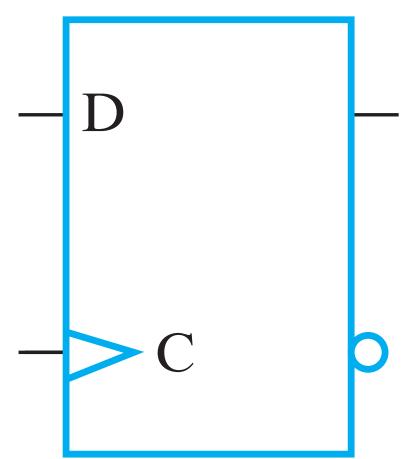

# LogicWorks Exercise

P2 Other Flip-Flop

- Implement *D* flip flop using *D* latch and *SR* latch Save it as a component in your library

- Implement circuit  $D_S = X \oplus Y \oplus S$ , where  $D_S$  is a D flip flop

- Implement  $D_A = \overline{X}A + XY$ ,  $D_B = \overline{X}B + XA$ , Z = XB

- Draw the state table and diagram, and verify your table with LogicWorks

# Implementation

- Implement *JK* Flip-Flop

- Implement *T* Flip-Flop

• Is there any other way to implement? What if you cannot use D Flip-Flop?