# CSCI 150 Introduction to Digital and Computer System Design Lecture 4: Sequential Circuit II

Jetic Gū 2020 Summer Semester (S2)

#### Announcements

- Assignment 1-3 and Lab 1-2 marks are out

- If you get a zero due to formatting issues, you can send me an email ASAP with the correct version and I'll regrade them for you. Don't worry.

- Quiz 2-3 marks will be released today.

- Late submissions will not be graded. 20mins of extra time was given for uploads, if you missed it, it's your own fault

- Midterm is tomorrow, submission before 15:10

- Be prepared, submit ON TIME. Late submissions will NOT be graded.

#### Overview

- Focus: Basic Information Retaining Blocks

- Architecture: Sequential Circuit

- Textbook v4: Ch5 5.2, 5.3; v5: Ch4 4.2, 5.3

- Core Ideas:

- 1. Flip-Flops

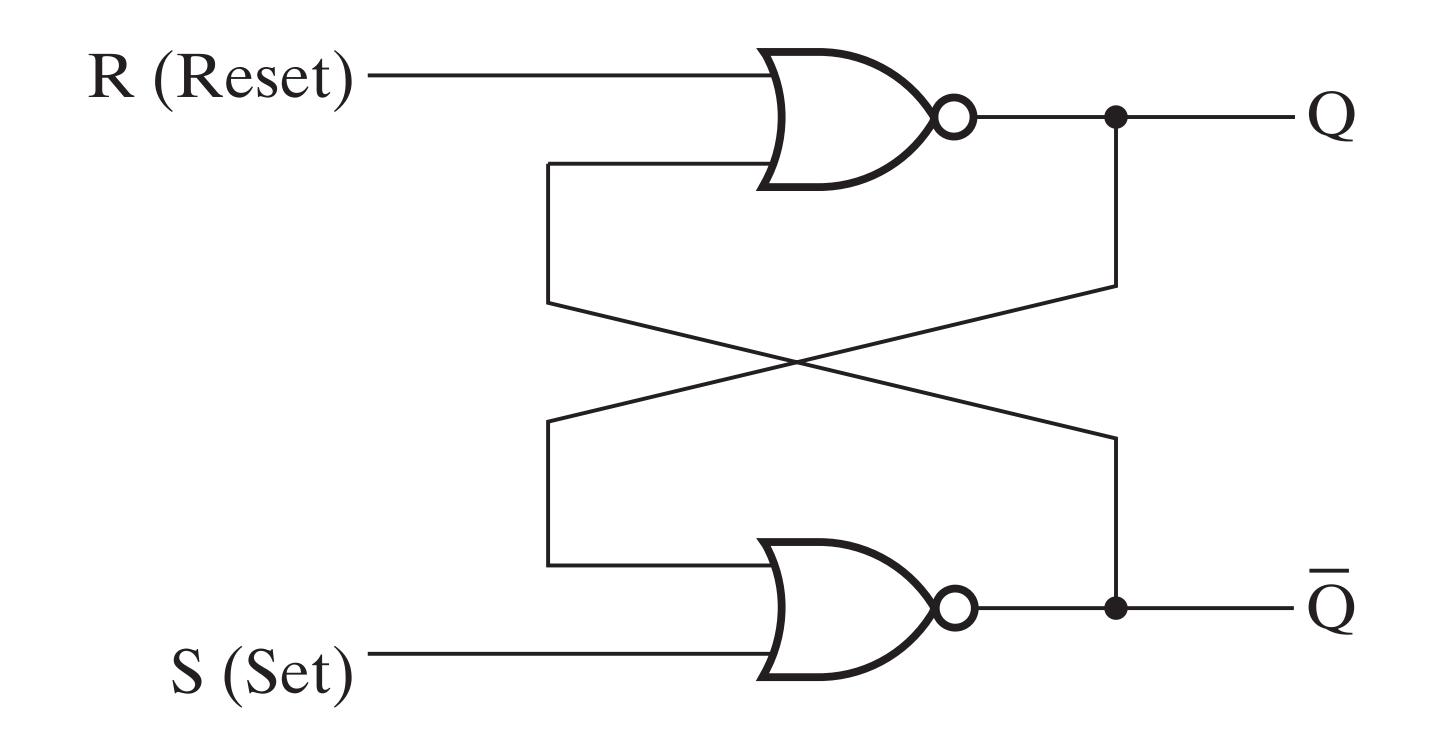

#### SR Latch

P0 Review

### SR Latch

| $\overline{S}$ $\overline{R}$               | $Q \overline{Q}$ |             |

|---------------------------------------------|------------------|-------------|

| <ul><li>0</li><li>1</li><li>1</li></ul>     | 1 0<br>1 0       | Set state   |

| <ol> <li>1</li> <li>1</li> <li>1</li> </ol> | 0 1<br>0 1       | Reset state |

| 0 0                                         | 1 1              | Undefined   |

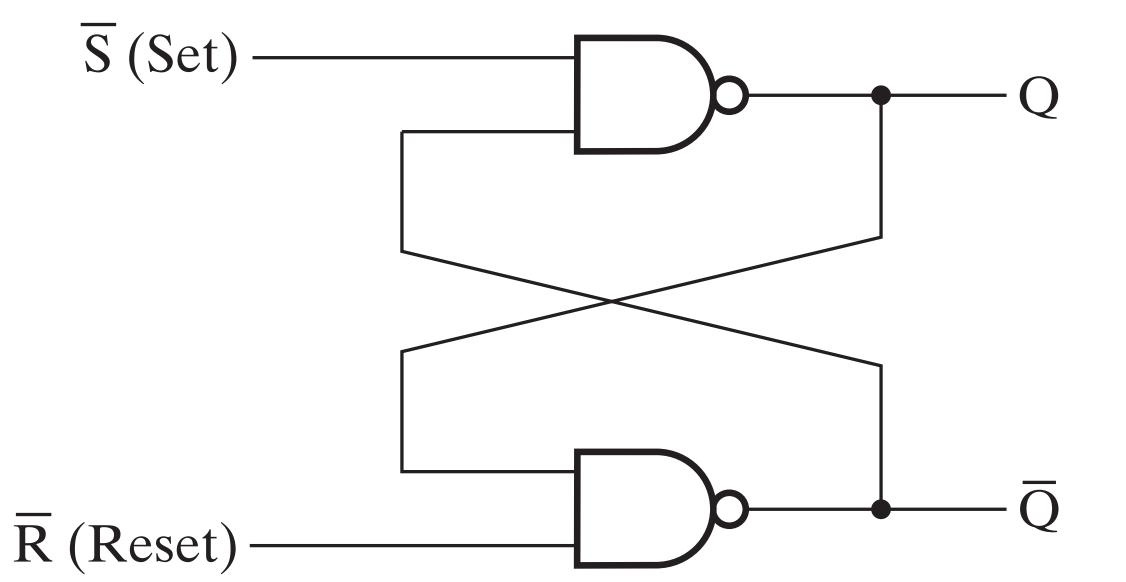

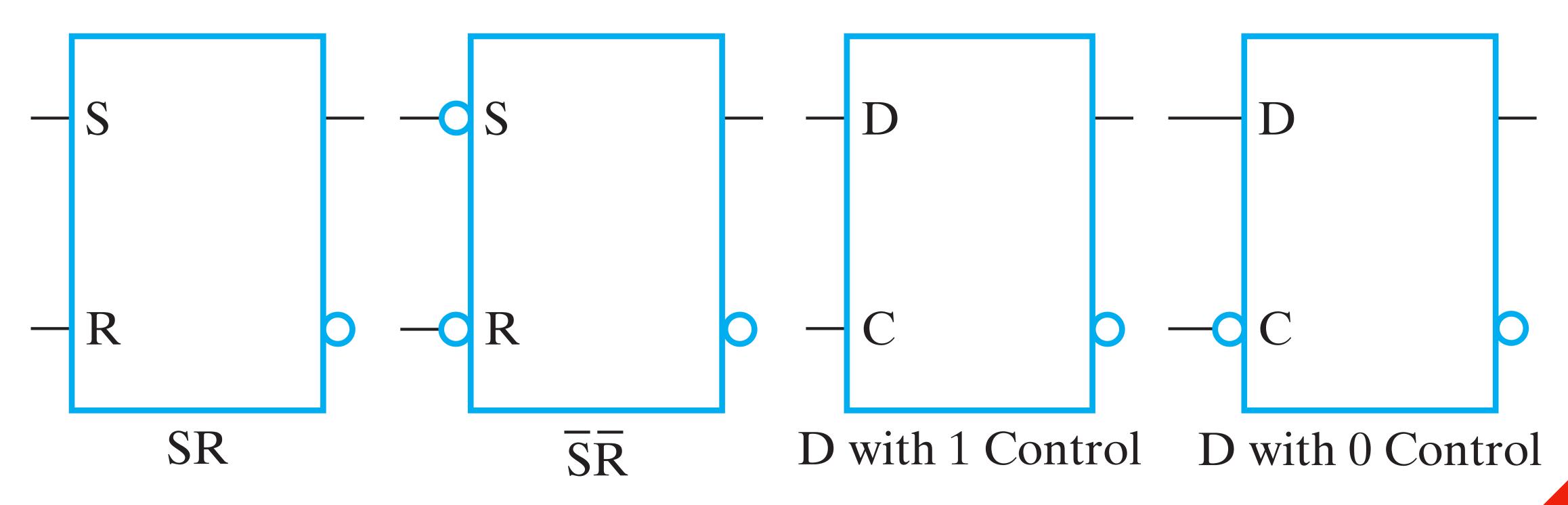

• Design similar to SR latches, but with NANDS

• Functions equivalent to  $S\!\!\!\!R^R\!\!\!$  atches with S and R inverted

P0 Review

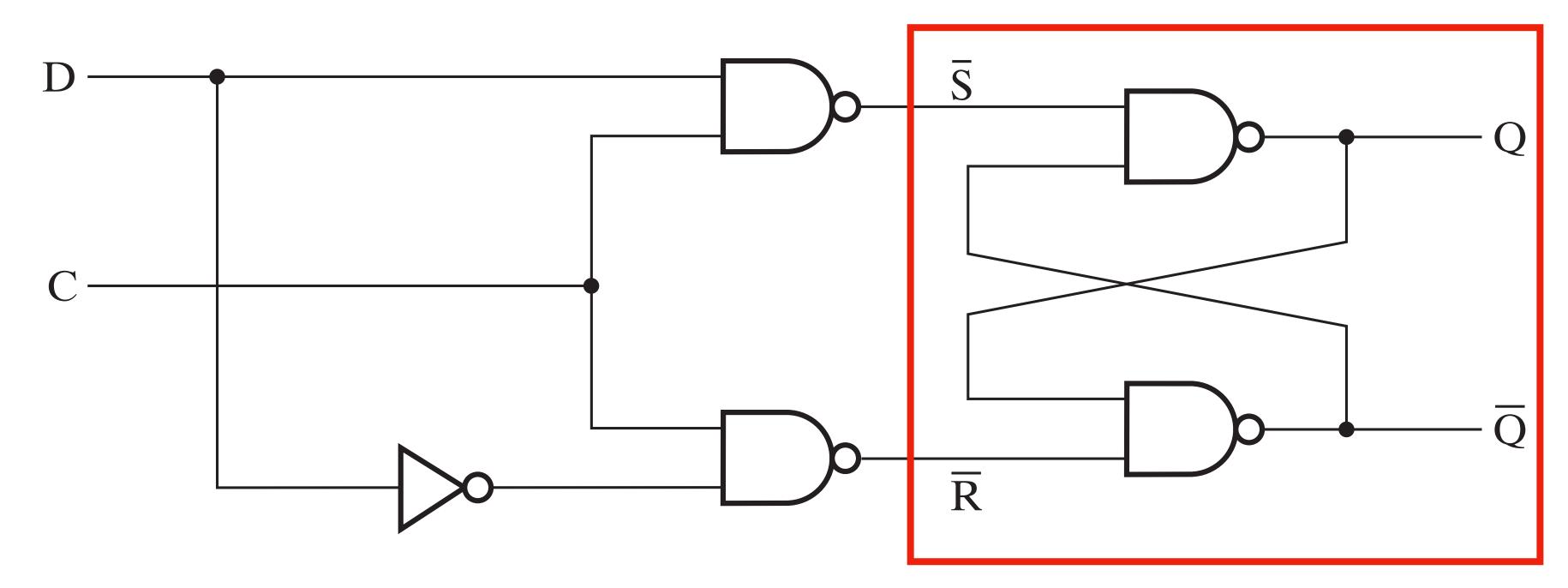

#### D Latch

| C D               | Next state of Q                                   |

|-------------------|---------------------------------------------------|

| 0 X<br>1 0<br>1 1 | No change $Q = 0; Reset state$ $Q = 1; Set state$ |

- Implemented using  $\overline{SR}$  latches

- C: Signals changes to the stored states; D the value to change to  $S\overline{R}$

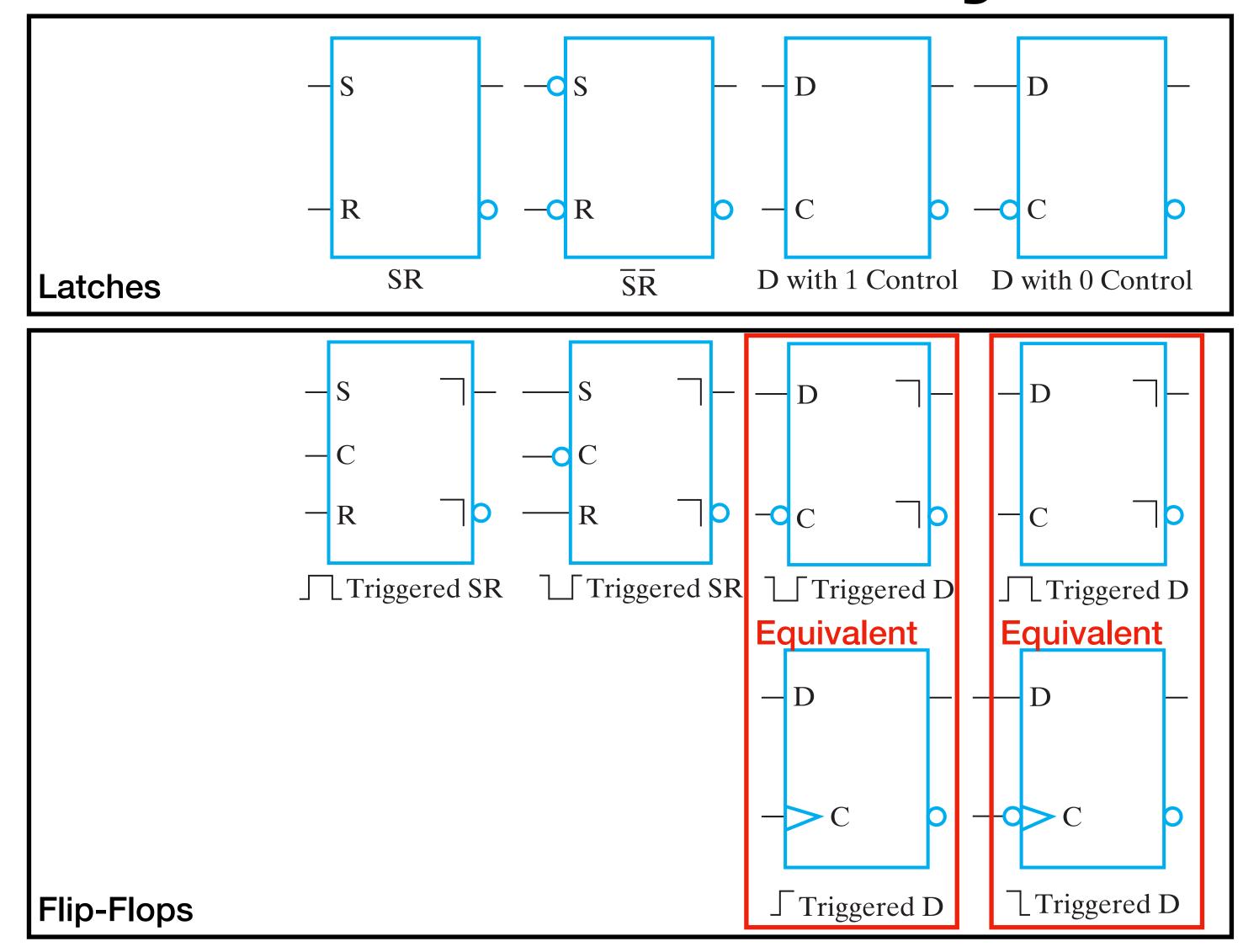

#### Latches

COUCEX

#### Flip-Flops

No, flip-flops are not proper shoes, nor shoes

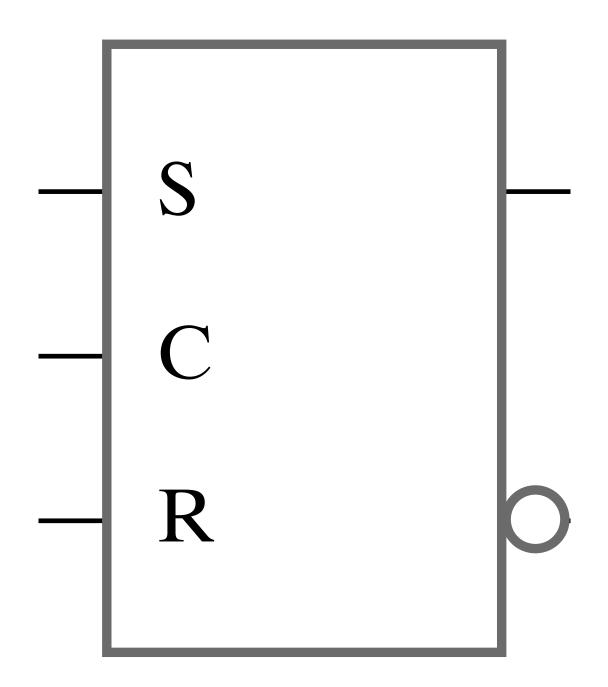

#### SR Latch with Control Input

| C S R        | Next state of Q    |

|--------------|--------------------|

| 0 <b>X X</b> | No change          |

| 1 0 0        | No change          |

| 1 0 1        | Q = 0; Reset state |

| 1 1 0        | Q = 1; Set state   |

| 1 1 1        | Undefined          |

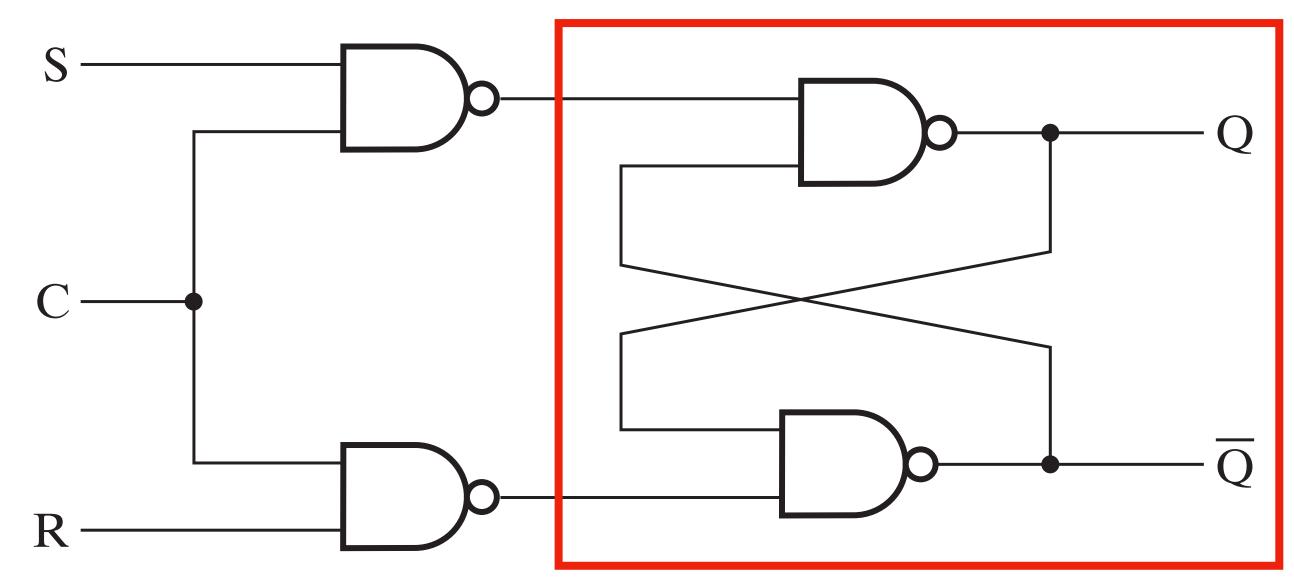

- Implemented using  $\overline{SR}$  latches

- C acts as an enabler; otherwise the entire circuit functions as an SR latch

#### SR Latch with Control Input

| C S R        | Next state of Q    |

|--------------|--------------------|

| 0 <b>X X</b> | No change          |

| 1 0 0        | No change          |

| 1 0 1        | Q = 0; Reset state |

| 1 1 0        | Q = 1; Set state   |

| 1 1 1        | Undefined          |

|              |                    |

- Implemented using  $\overline{SR}$  latches

- C acts as an enabler; otherwise the entire circuit functions as an SR latch

#### Latches

- What happens if the control pulse remains active?

- any changes in the data input will change the state of the latch immediately!

- latches are transparent

input can be seen from outputs while control pulse is 1

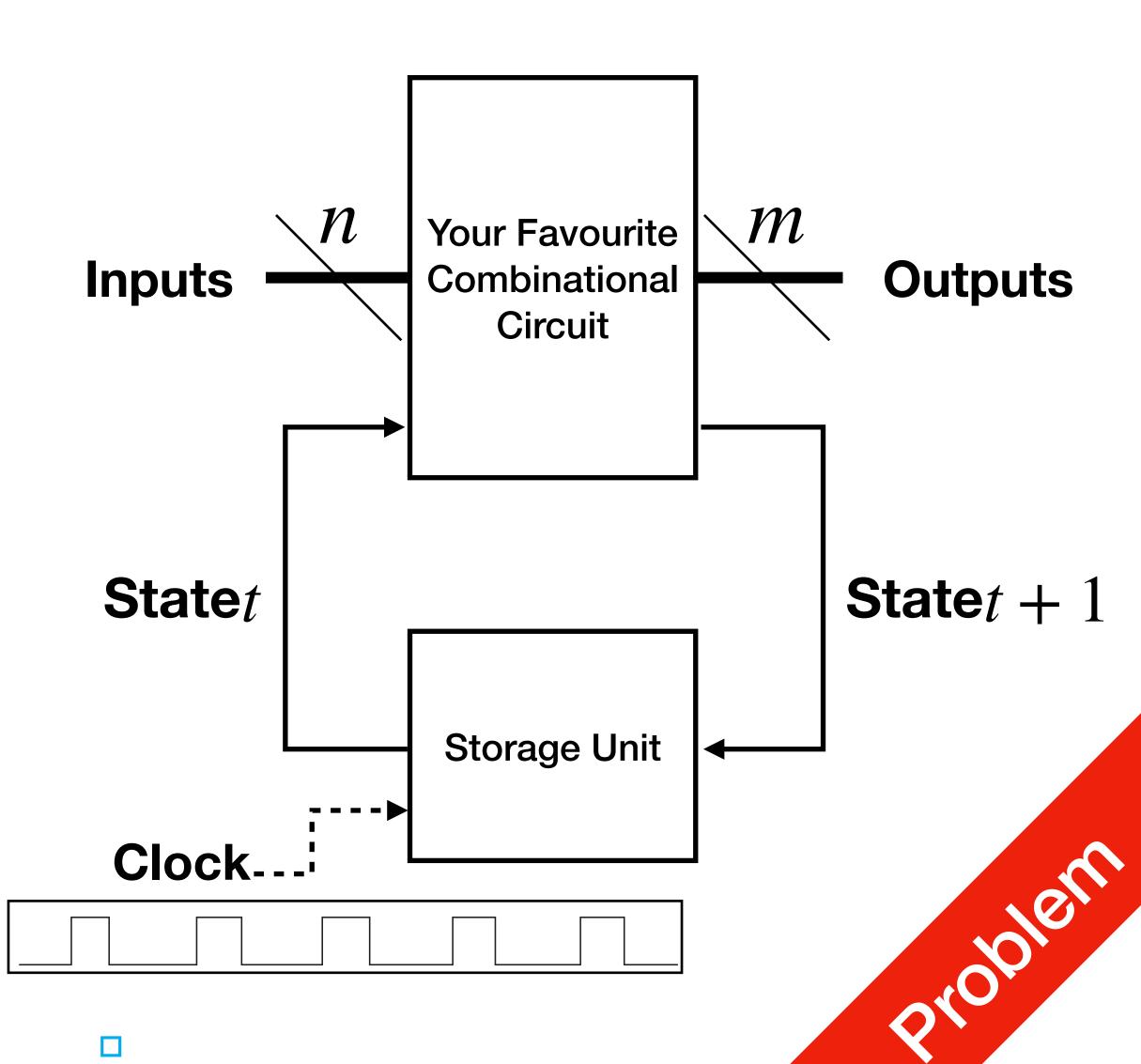

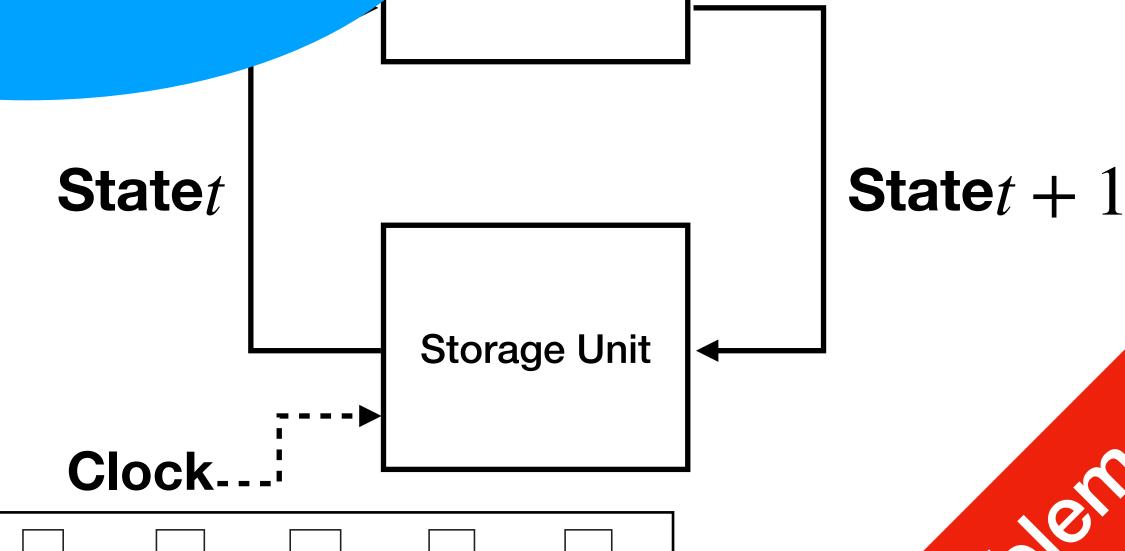

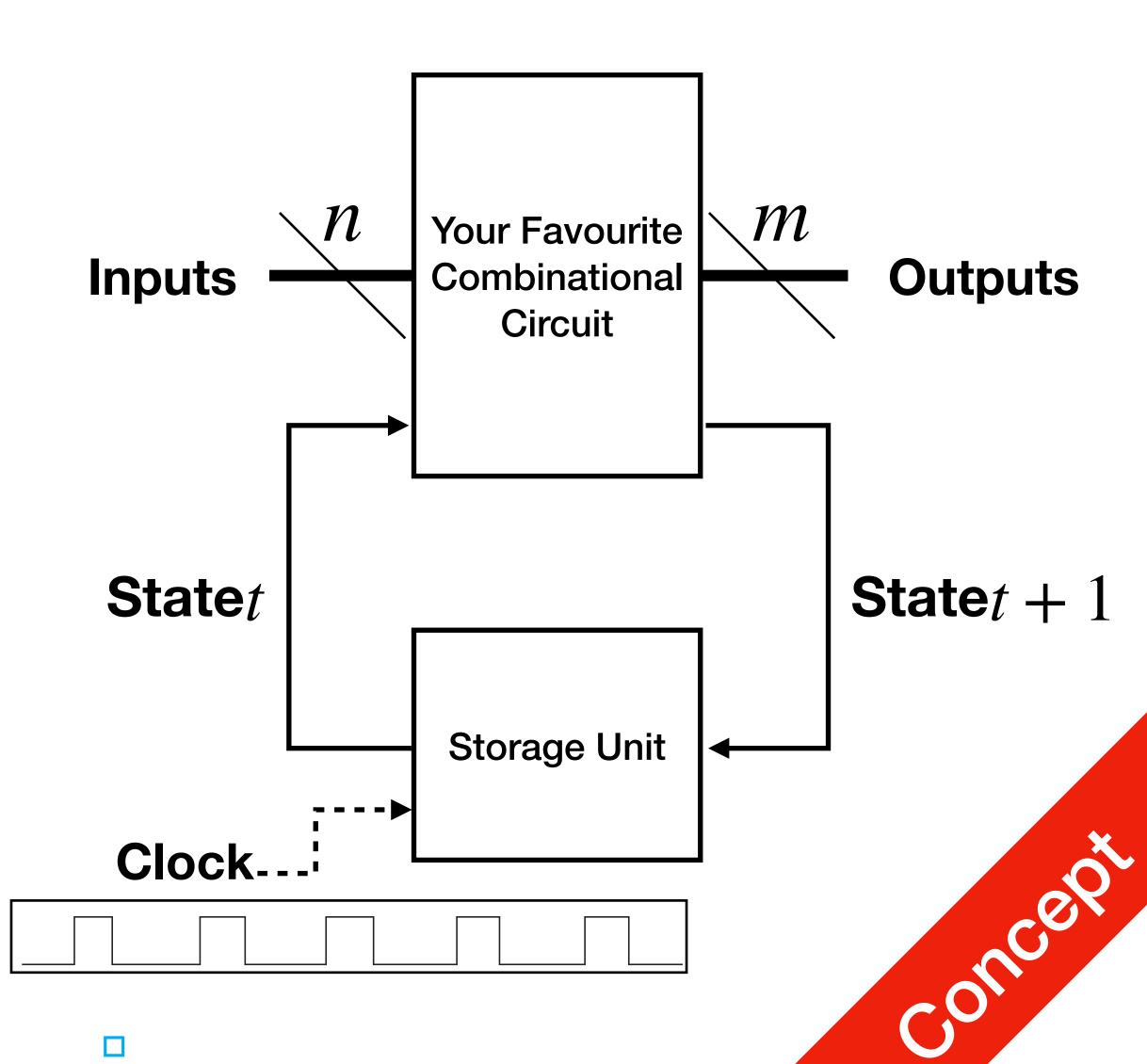

#### Problems with Latches

- Transparent: changes happen instantly

- Time *t*, input changes

- Time (t, t + 1), output stabilises

- Time t+1, output stored in Storage Unit

#### Problems with Latch

Latches cannot accomplish this!

$\boldsymbol{m}$

**Outputs**

Transparent: changes happ

• Time *t*, input changes

• Time (t, t + 1), output stabilises

• Time t+1, output stored in Storage Unit

During this period, storage unit must keep outputting  $State_t$ , otherwise output may not stabilise

ur Favourite

mbinational

Circuit

#### Flip-Flops

- Time t, clock flips, new input arrives

- Time (t, t + 1): output  $State_t$

- meanwhile, new inputs arrives;

State<sub>t+1</sub> stabilises

- Time t+1, clock flips, storage rewritten as  $State_{t+1}$ , new input arrives

- Time (t + 1, t + 2): output  $State_{t+1}$

- •

#### Flip-Flops

- Time *t*, clock flips, new input arrives

- Time (t, t + 1): output  $State_t$

- meanwhile, new inputs arrives;  $State_{t+1}$  stabilises

- Time t+1, clock flips, storage rewritten as  $\mathrm{State}_{t+1}$ , new input arrives

- Time (t + 1, t + 2): output  $State_{t+1}$

• ...

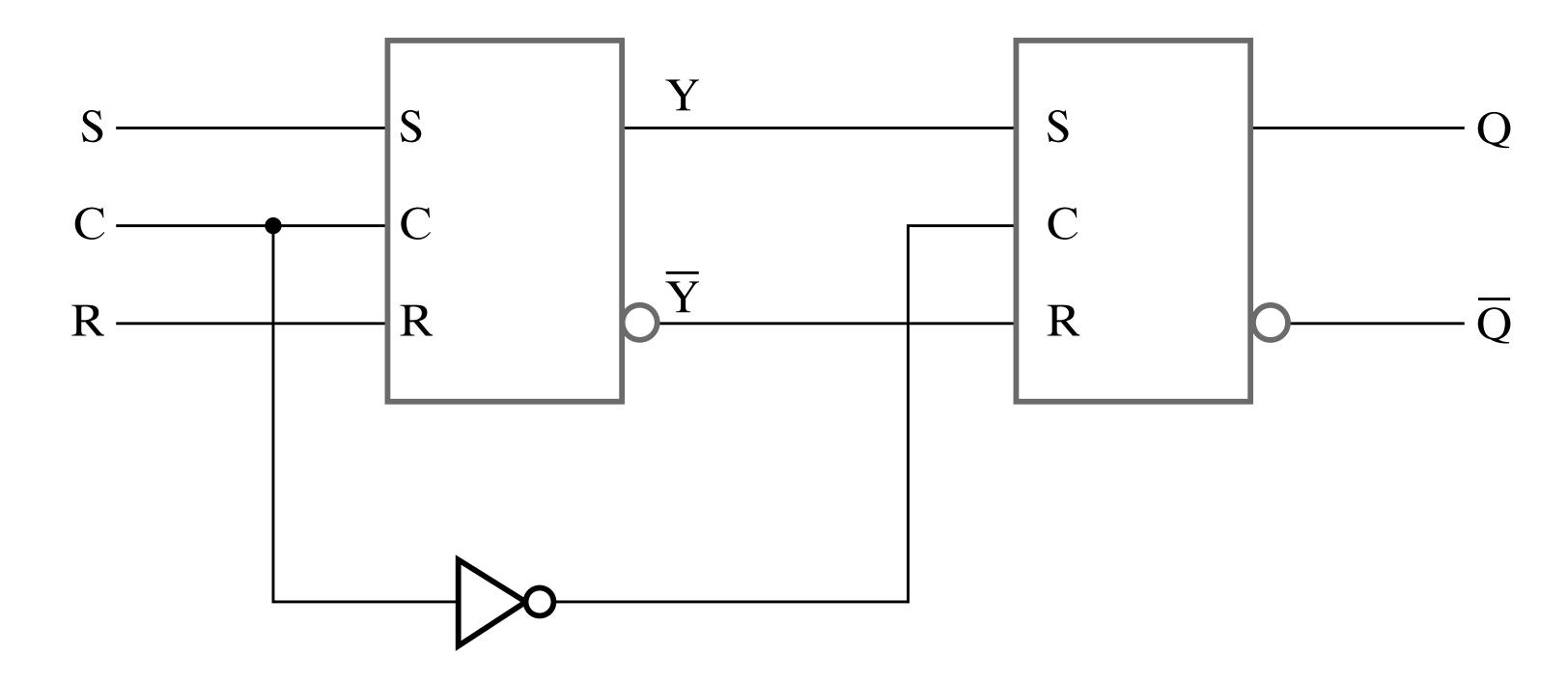

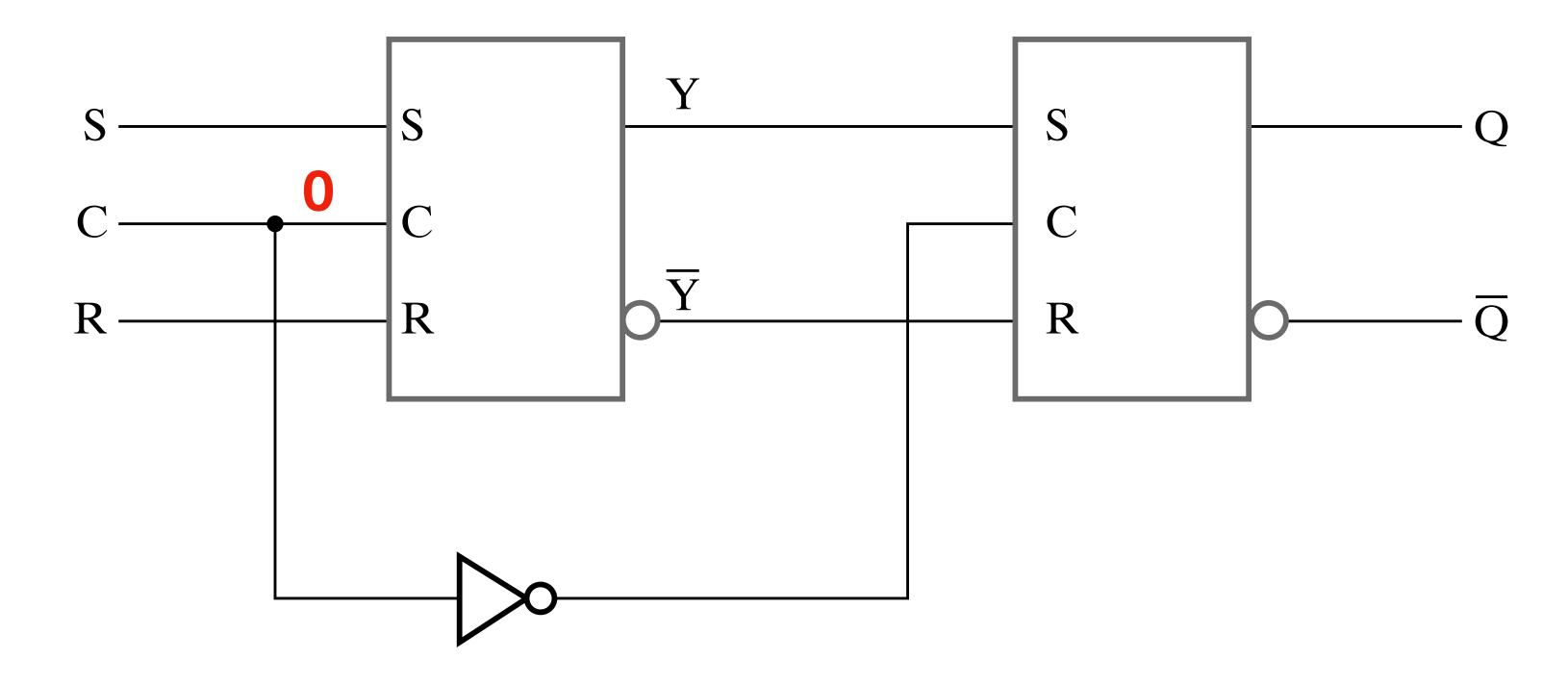

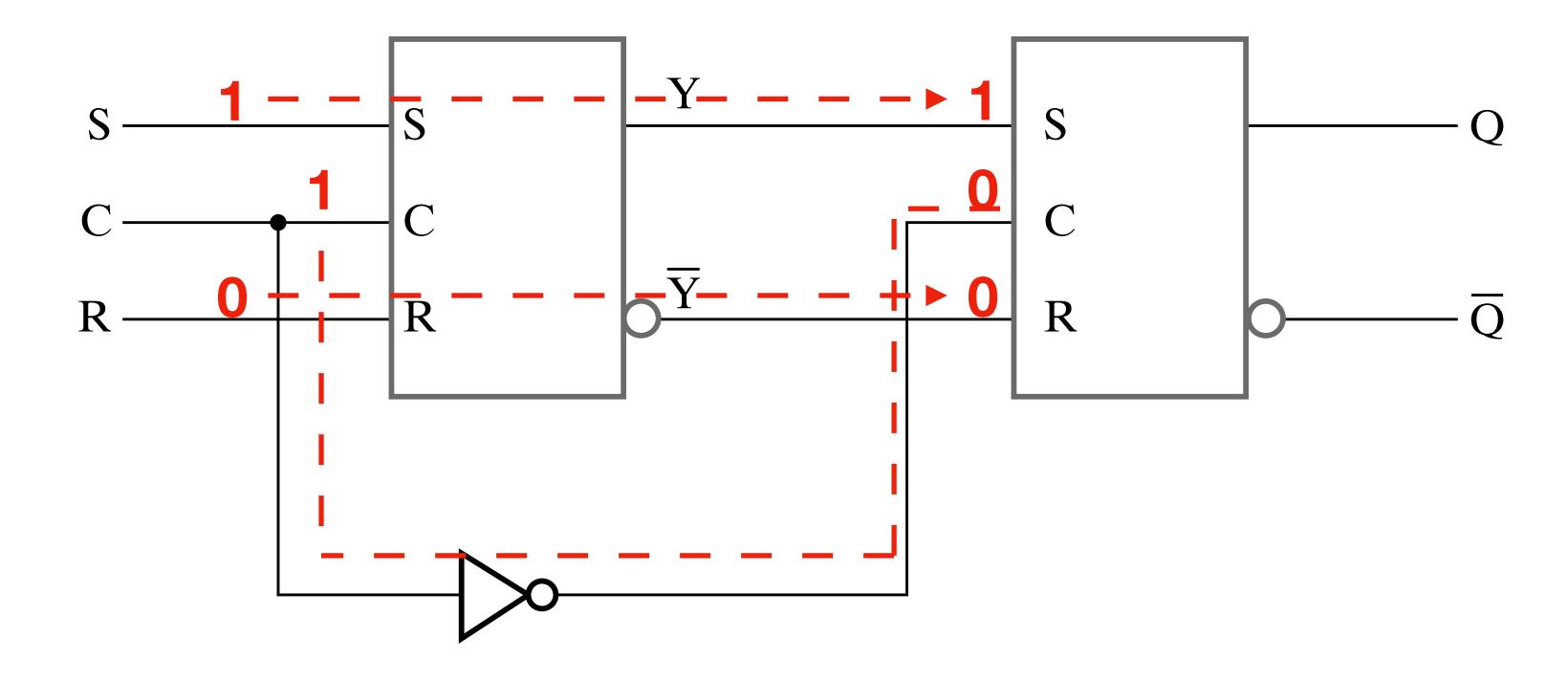

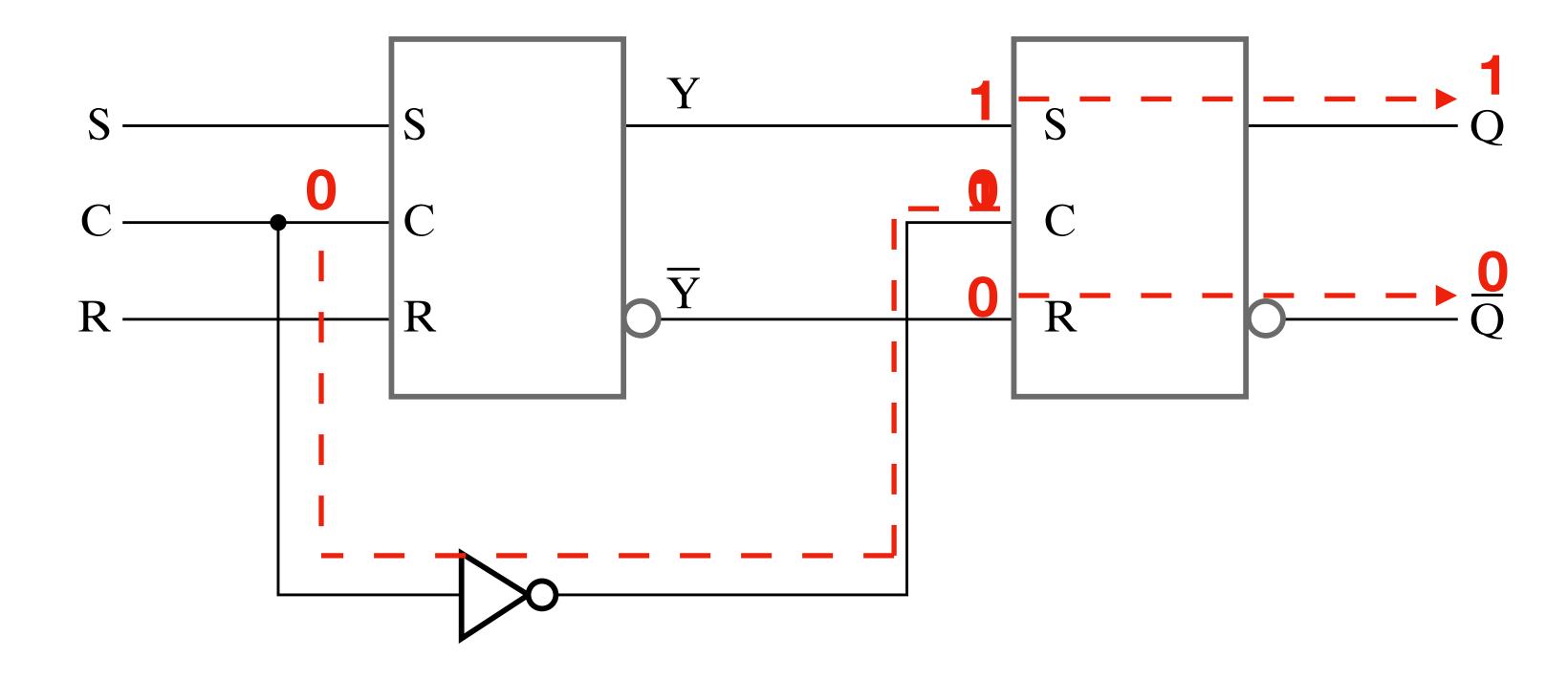

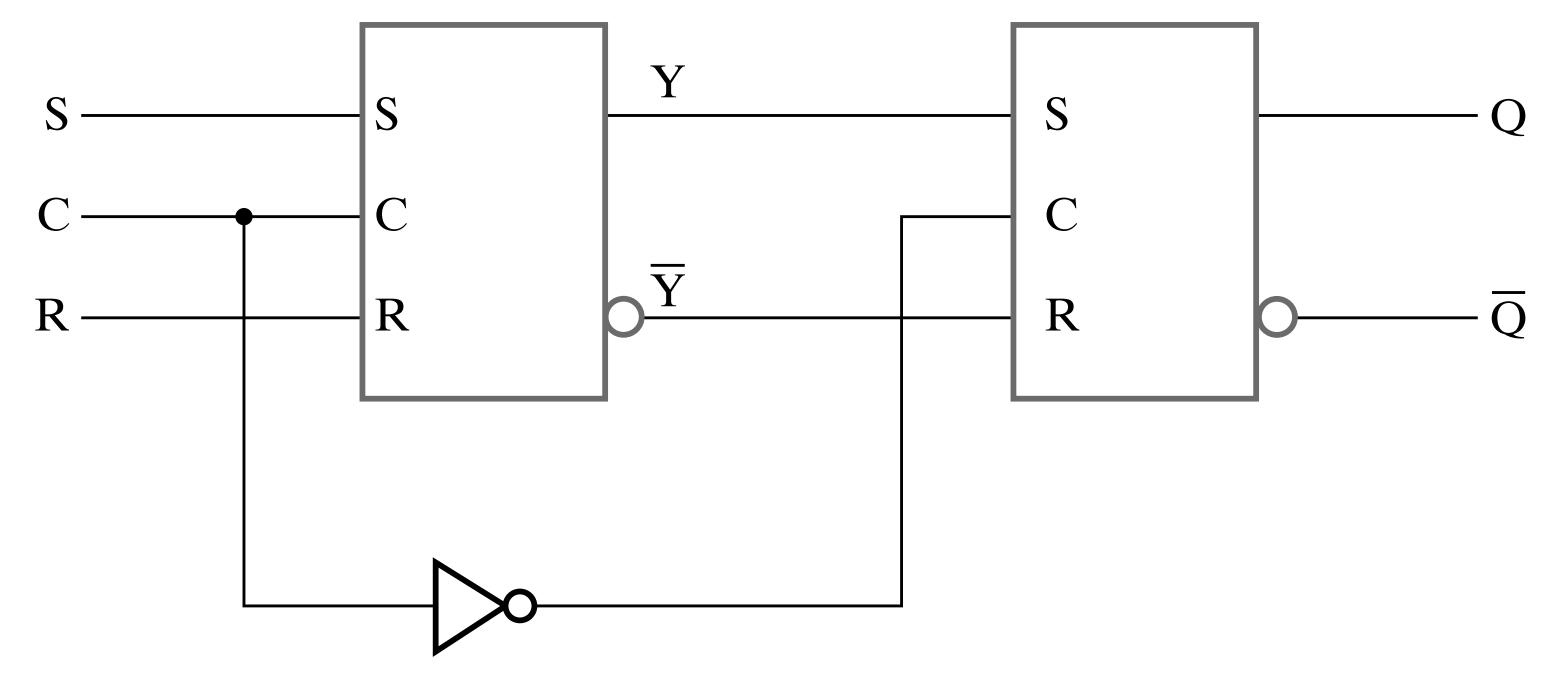

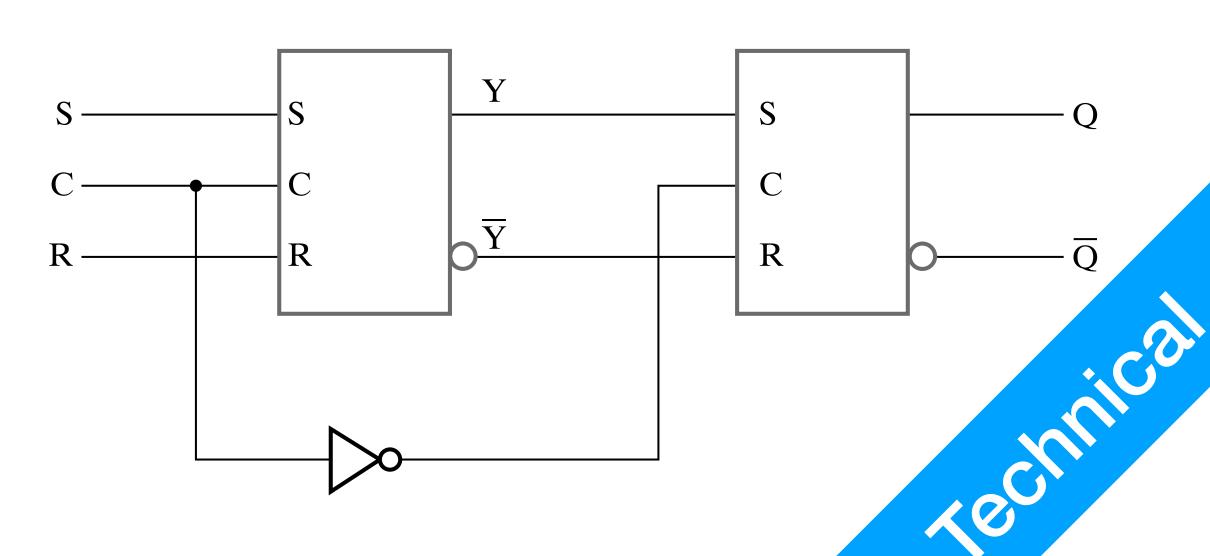

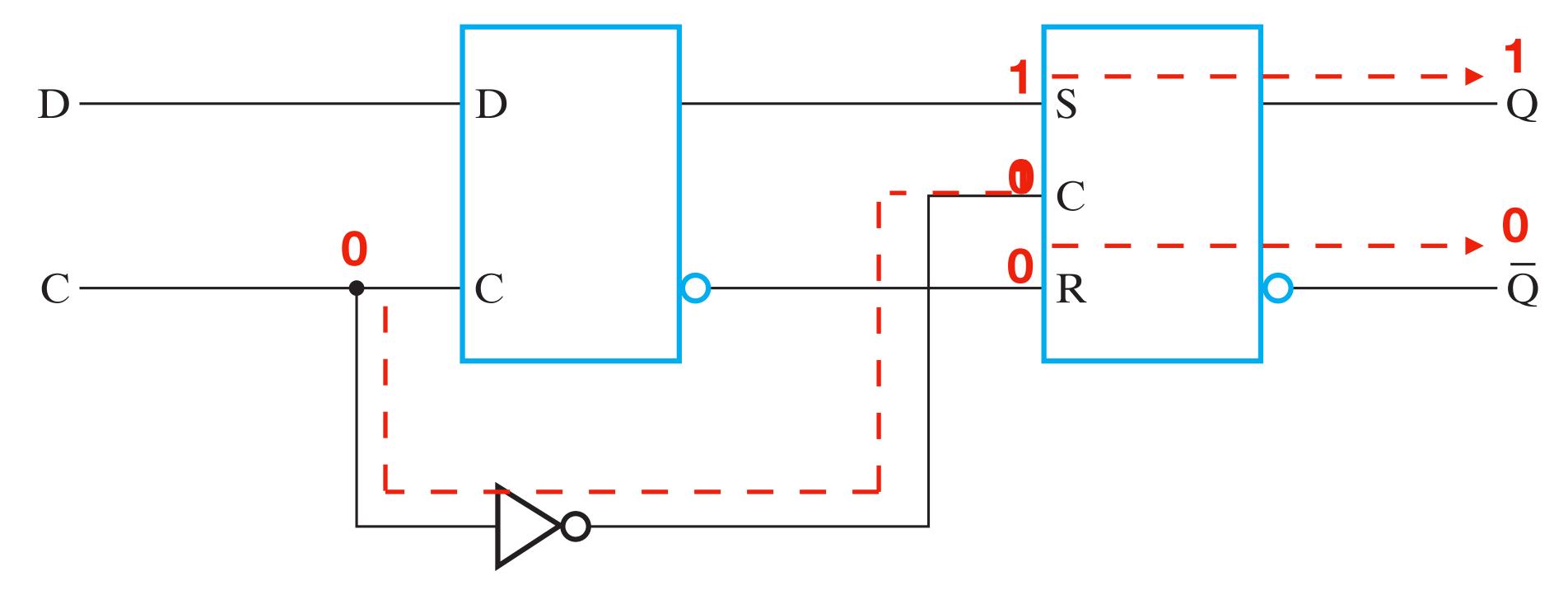

- Constructed using SR latches, left Master, right Slave

- Output state changes require  $C=0 \rightarrow C=1 \rightarrow C=0$  (Positive Pulse)

- Constructed using SR latches, left Master, right Slave

- Output state changes require  $C=0 \rightarrow C=1 \rightarrow C=0$  (Positive Pulse)

- Constructed using SR latches, left Master, right Slave

- Output state changes require  $C=0 \rightarrow C=1 \rightarrow C=0$  (Positive Pulse)

- Constructed using SR latches, left Master, right Slave

- Output state changes require  $C=0 \rightarrow C=1 \rightarrow C=0$  (Positive Pulse)

- Constructed using SR latches, left Master, right Slave

- Output state changes require  $C=0 \rightarrow C=1 \rightarrow C=0$  (Positive Pulse)

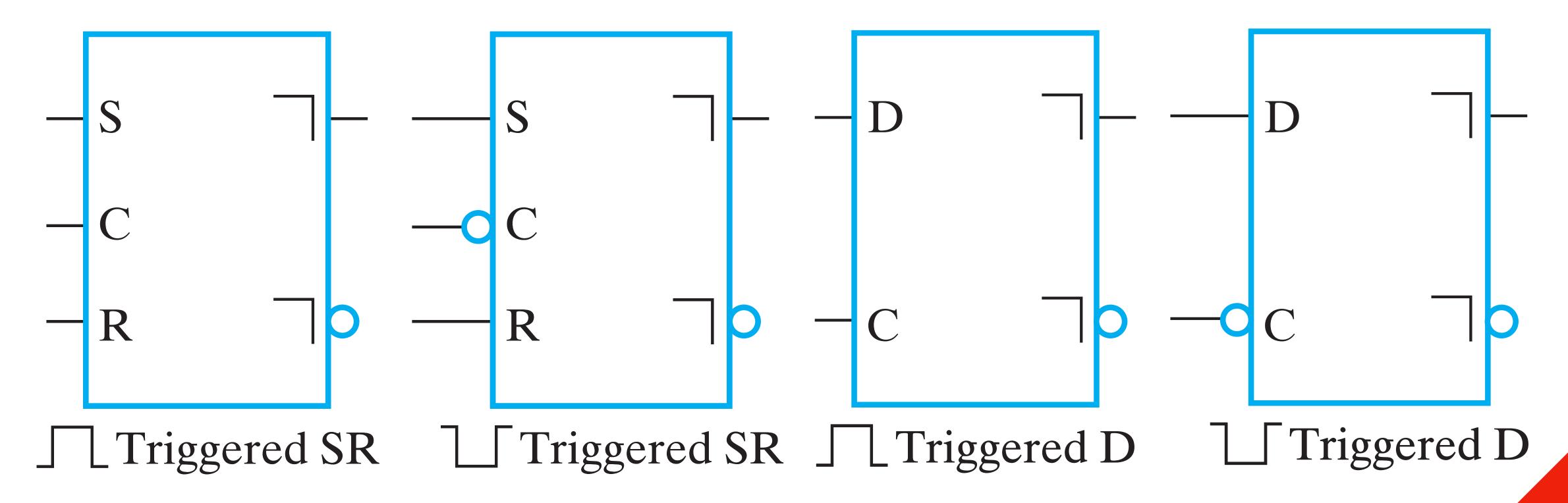

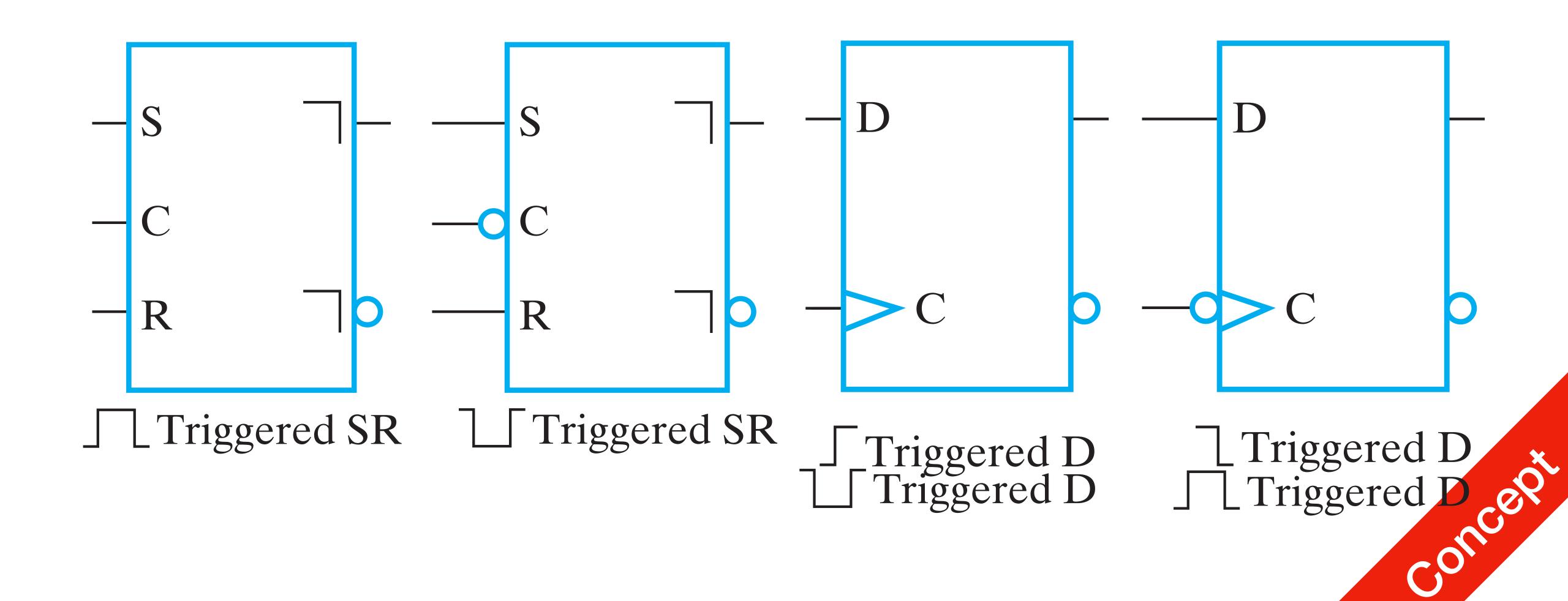

- Also called: **Positive Pulse Triggered** SR (Flip-Flop)

- Output state changes require  $C = 1 \rightarrow C = 0 \rightarrow C = 1$  (Negative Pulse)

- Negative Pulse Triggered SR (Flip-Flop)

## Implement Positive Pulse Triggered $SR^{\overline{SR}}$

• Implement SR Latch with Control Input using  $\overline{SR}$  Latch

$\begin{array}{c} C \\ \hline Q \\ \hline R \\ \hline \end{array}$

• Implement Positive Pulse Triggered SR using SR latch with Control Input

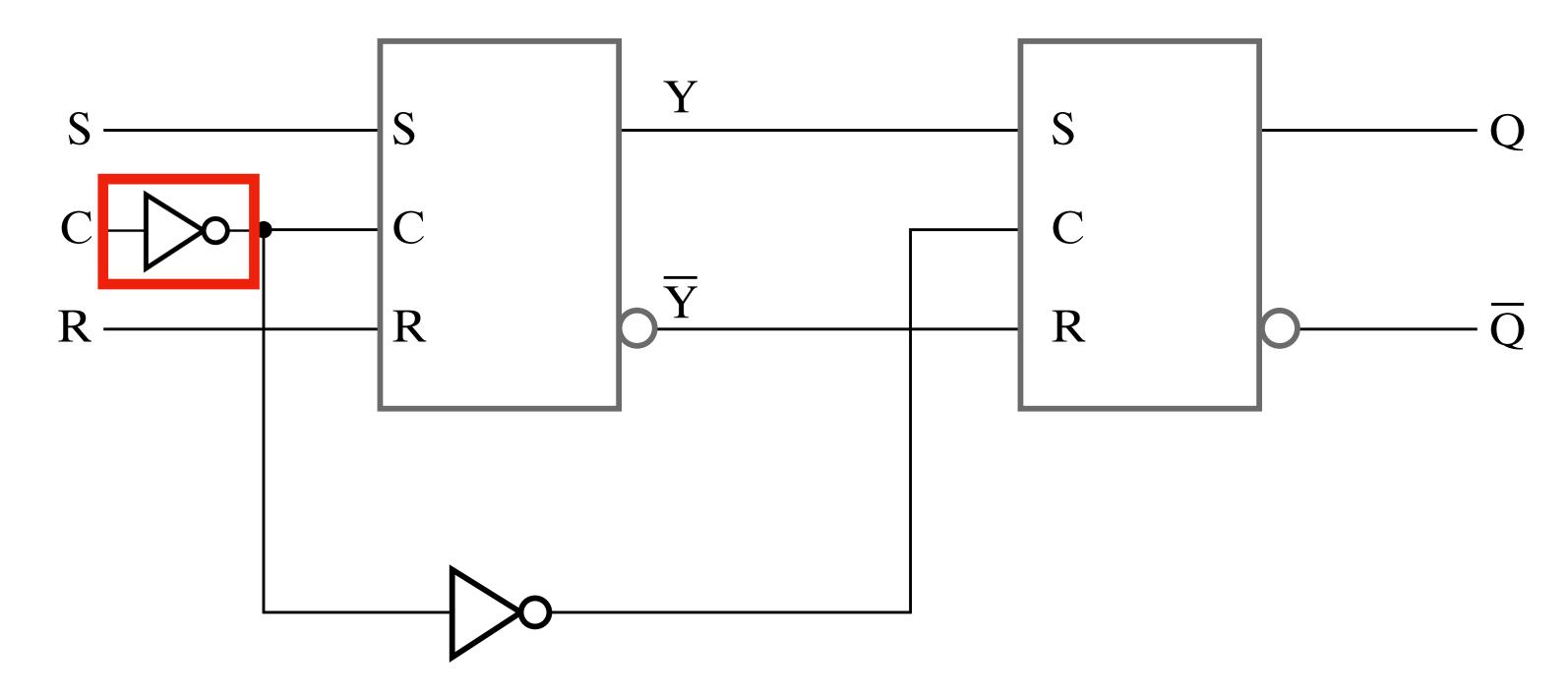

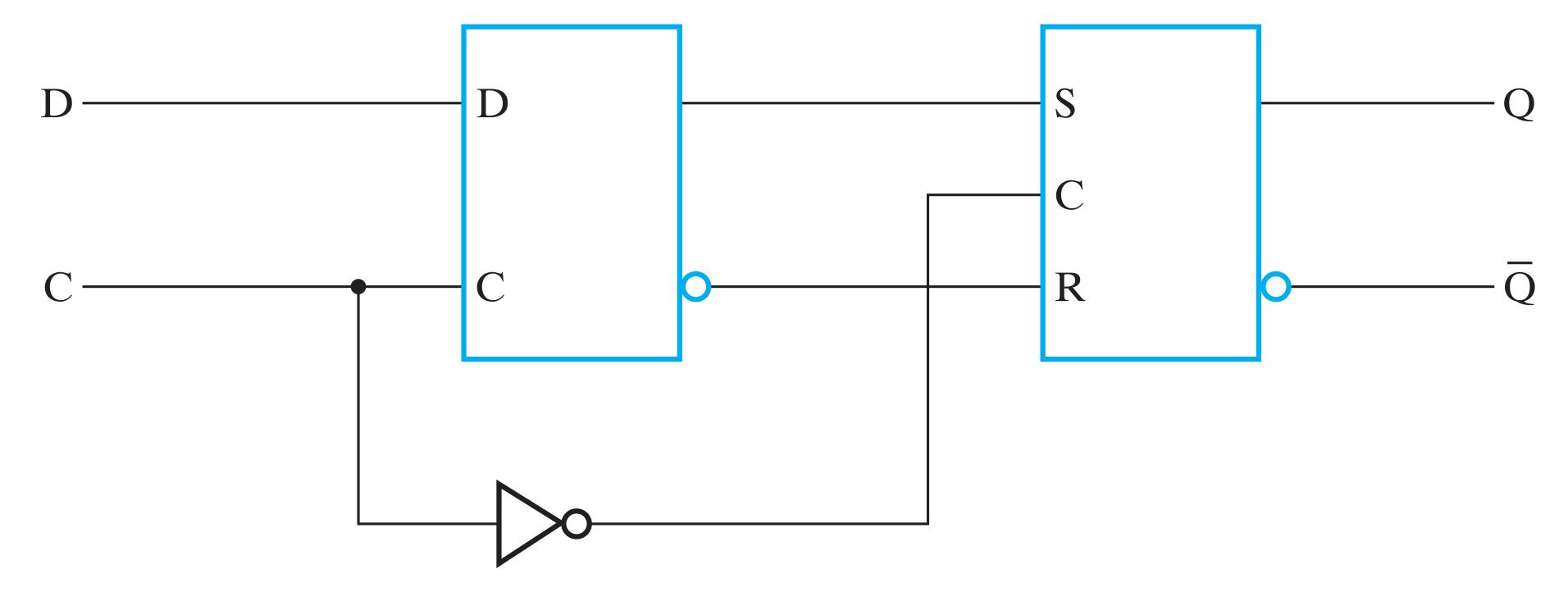

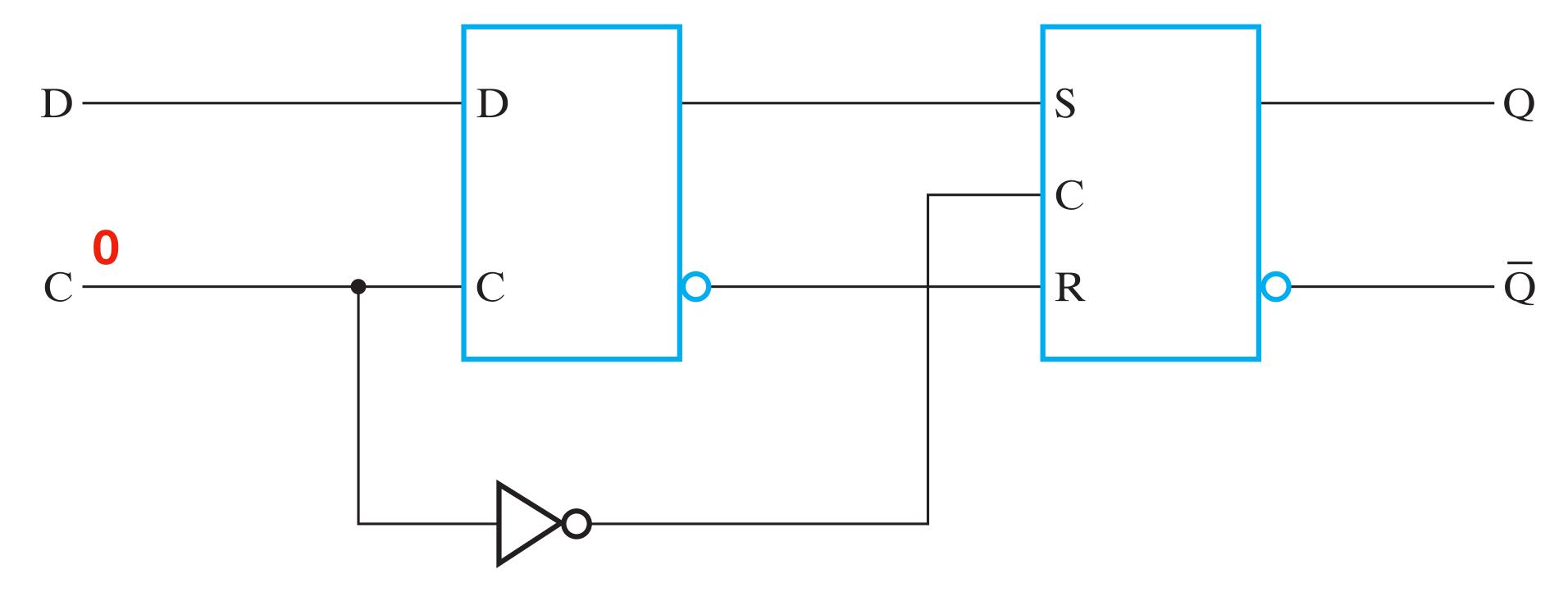

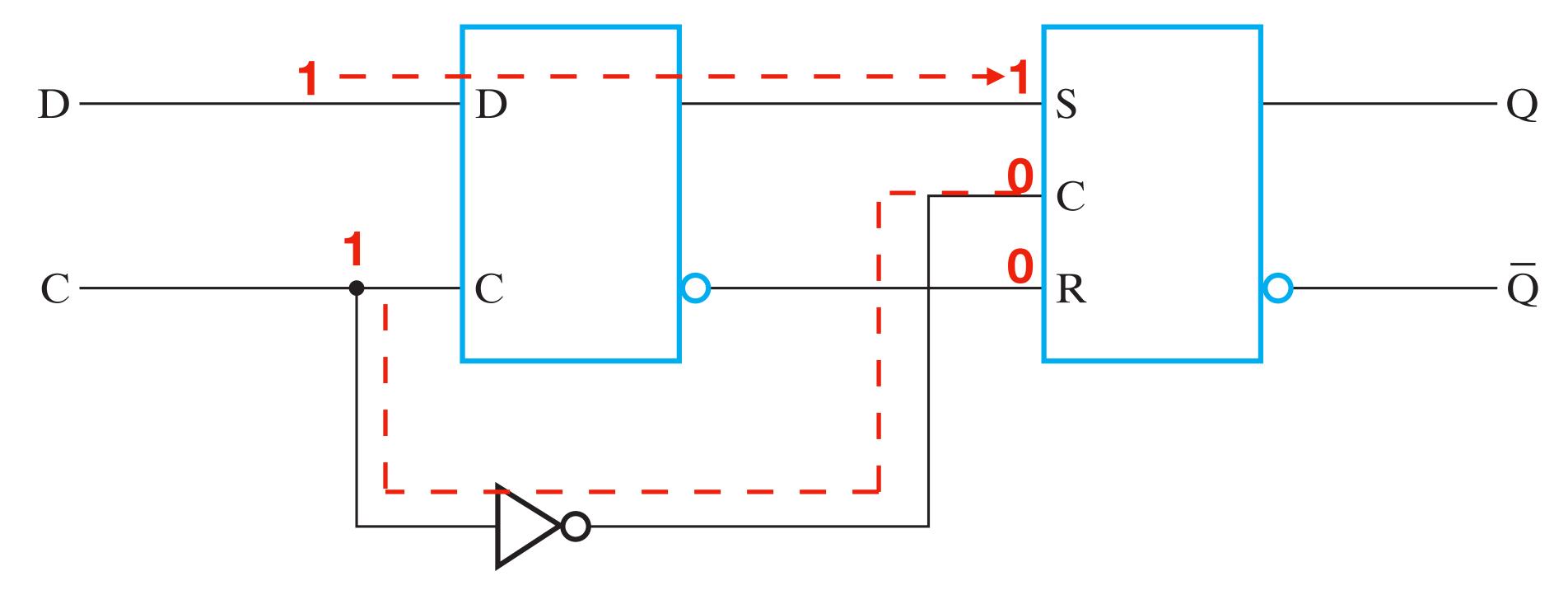

- ullet Replaces SR master in SR Master-Slave with D master Latch

- Negative Edge Triggered D (Flip-Flop):  $C=1 \rightarrow C=0$

- ullet Replaces SR master in SR Master-Slave with D master Latch

- Negative Edge Triggered D (Flip-Flop):  $C=1 \rightarrow C=0$

- ullet Replaces SR master in SR Master-Slave with D master Latch

- Negative Edge Triggered D (Flip-Flop):  $C=1 \rightarrow C=0$

- ullet Replaces SR master in SR Master-Slave with D master Latch

- Negative Edge Triggered D (Flip-Flop):  $C=1 \rightarrow C=0$

#### Flip Flops

#### Flip Flops

#### Summary