#### CSCI 150 Introduction to Digital and Computer System Design Lecture 3: Combinational Logic Design VI

Jetic Gū 2020 Summer Semester (S2)

#### Overview

- Focus: Arithmetic Functional Blocks

- Architecture: Combinatory Logical Circuits

- Textbook v4: Ch4 4.3, 4.7; v5: Ch2 2.9, Ch3 3.10

- Core Ideas:

- 1. Subtraction I

- 2. VHDL

#### Review **Unsigned Binary Adder**

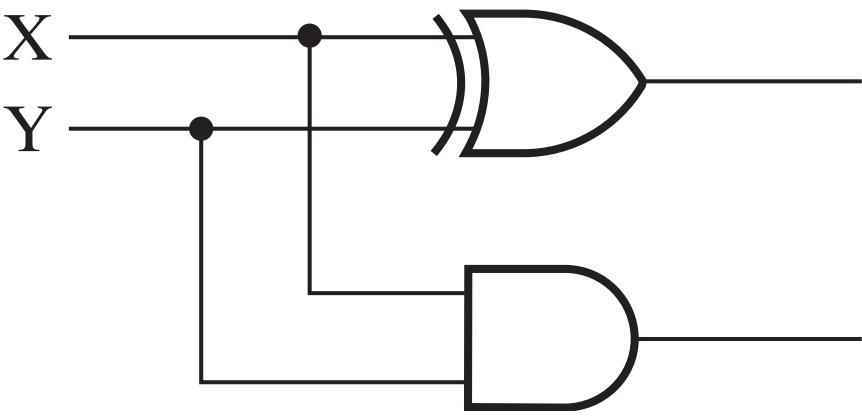

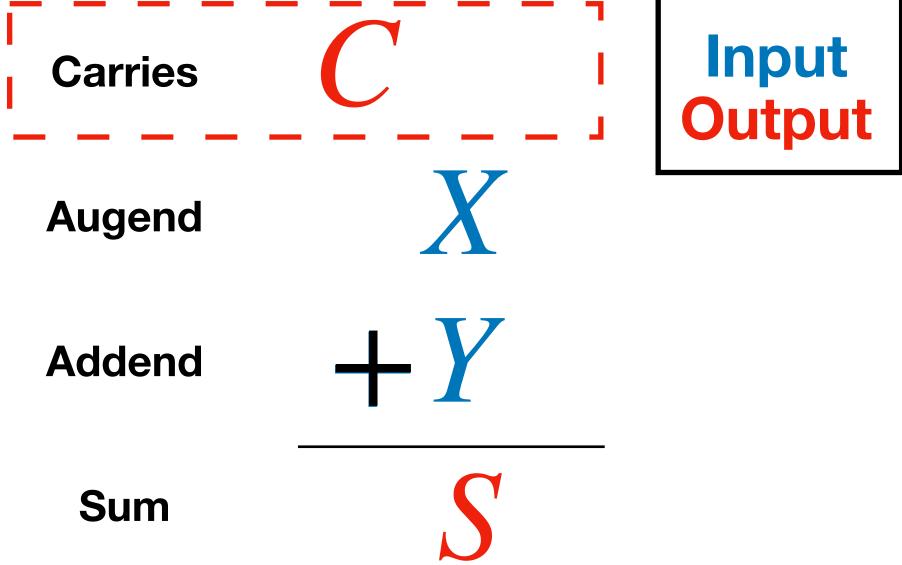

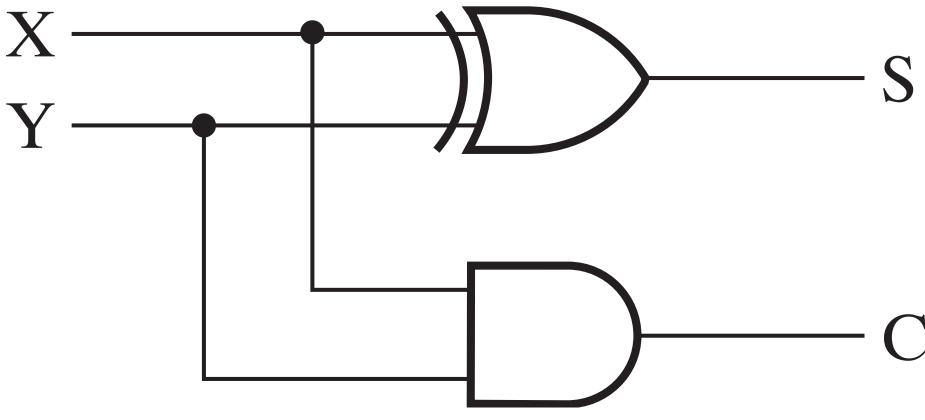

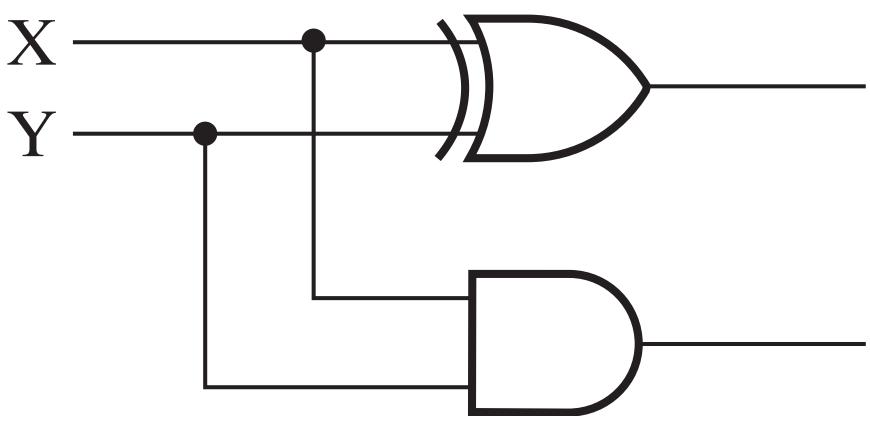

#### 1-bit Half Adder

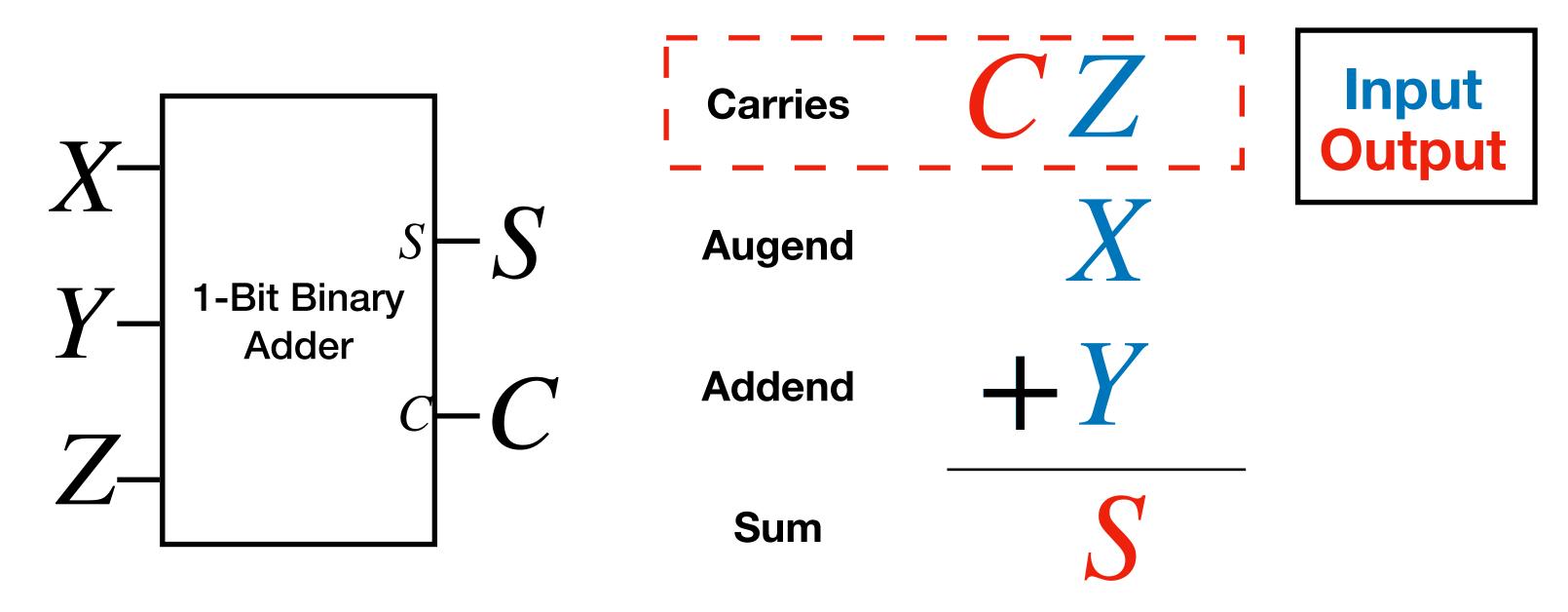

• Half adder input *X*, *Y* output *S*, *C*

#### 1-bit Half Adder

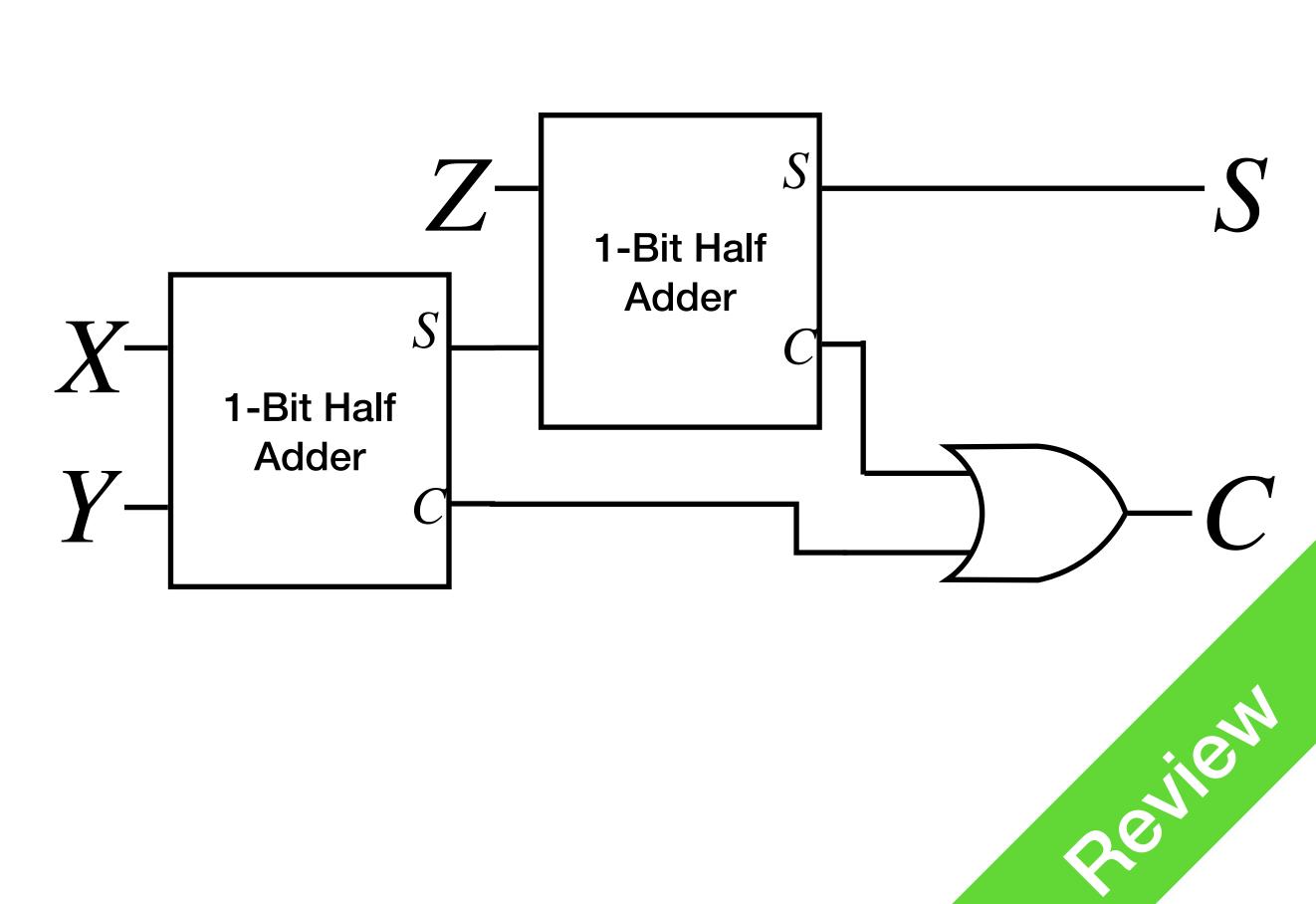

> • Full adder input *X*, *Y*, *Z*; output S, C

#### 1-bit Full Adder

#### **1-bit Full Adder**

• Half adder1 input X, Y output S', C'

• Full adder input *X*, *Y*, *Z*; output S, C

**P0**

**Binary Adder**

- Half adder2 input *S'*, *Z* output *S*, *C*"

- C = C' + C''

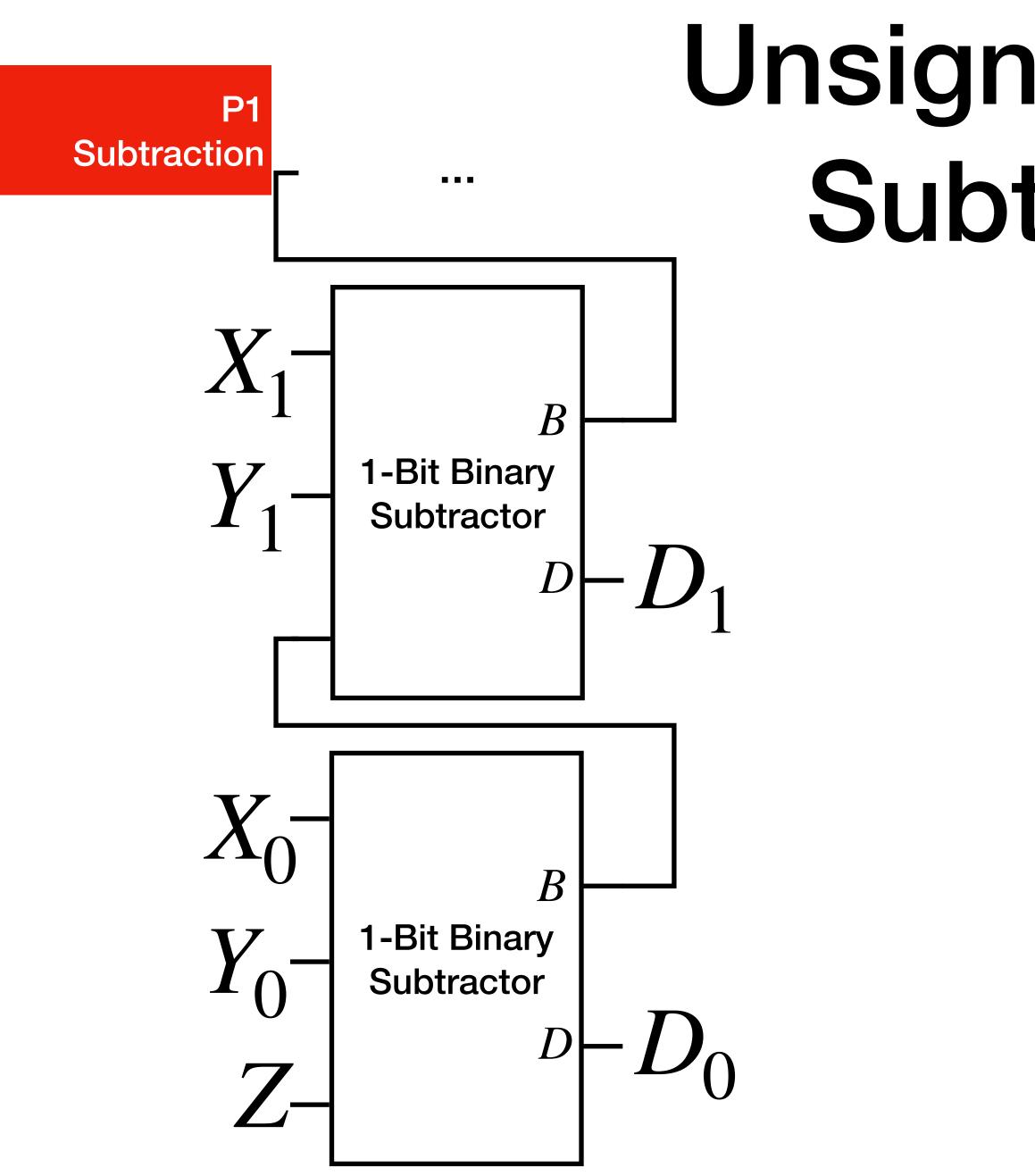

P1 Subtraction

## Unsigned Binary Subtraction I

- Input: Minuend and Subtrahend Previous borrow

- Output: Last borrow, difference

## Borrows0Minuend10110Subtrahend-10011

Difference

- Input: Minuend and Subtrahend Previous borrow

- Output: Last borrow, difference

This method works when the Minuend is greater than the Subtrahend!

| Borrows    | 000110                   |

|------------|--------------------------|

| Minuend    | 10110<br>Input<br>Output |

|            |                          |

| Subtrahend | -10011                   |

| Difference | 00011                    |

#### X > Y, F = X - Y

We learned to perform subtraction, the greater number

• We learned to perform subtraction, by subtracting the smaller number from

- Input: Minuend and Subtrahend Previous borrow

- Output: Last borrow, difference

Borrows0000110Minuend101100Subtrahend-100111Difference000111

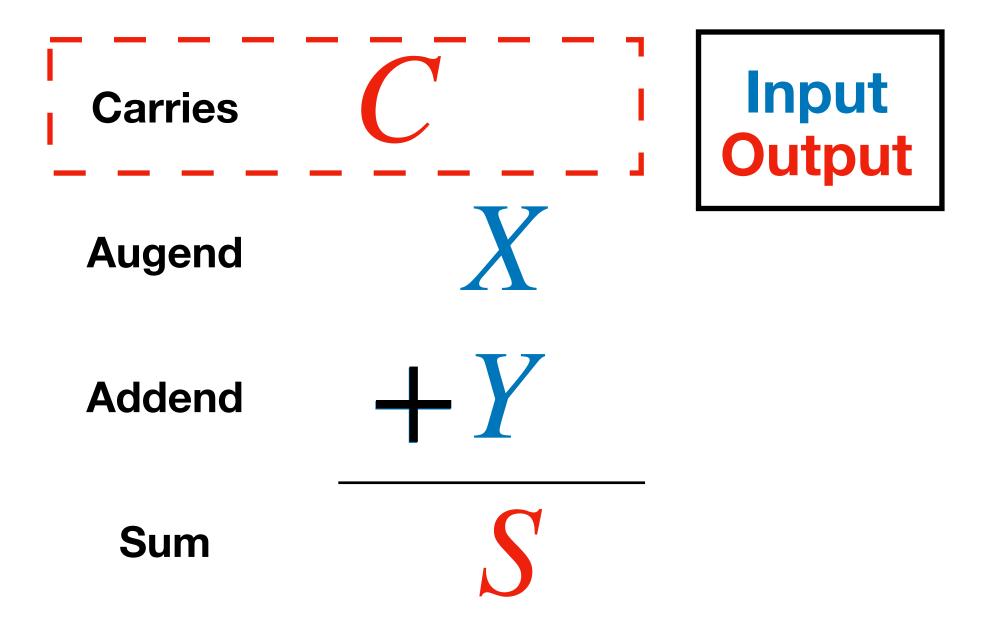

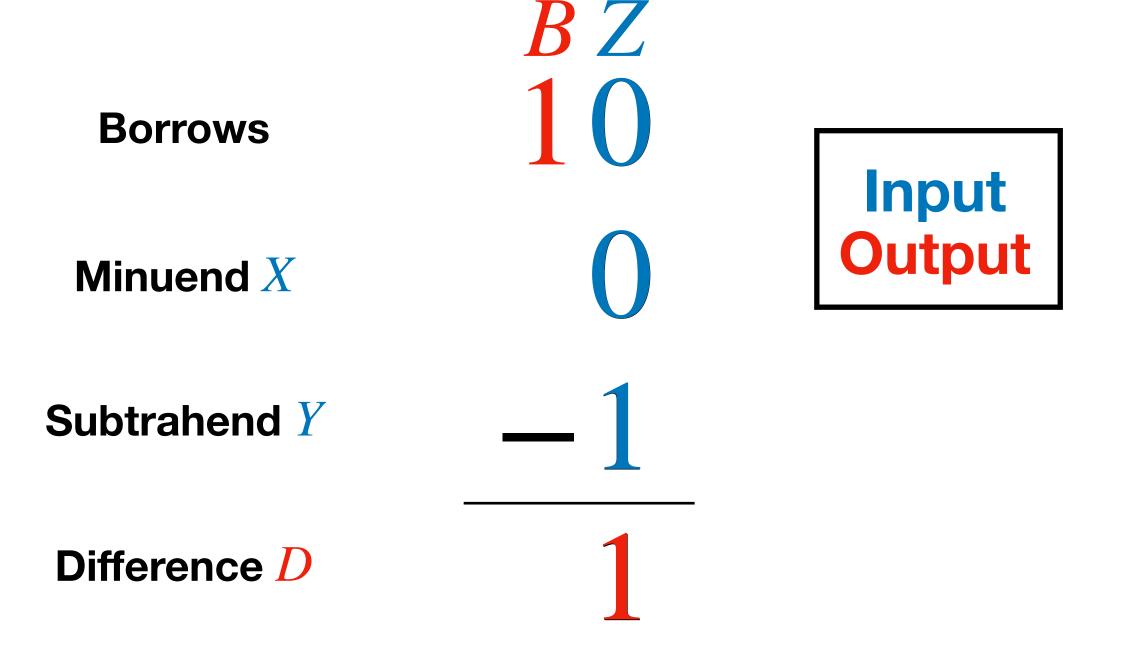

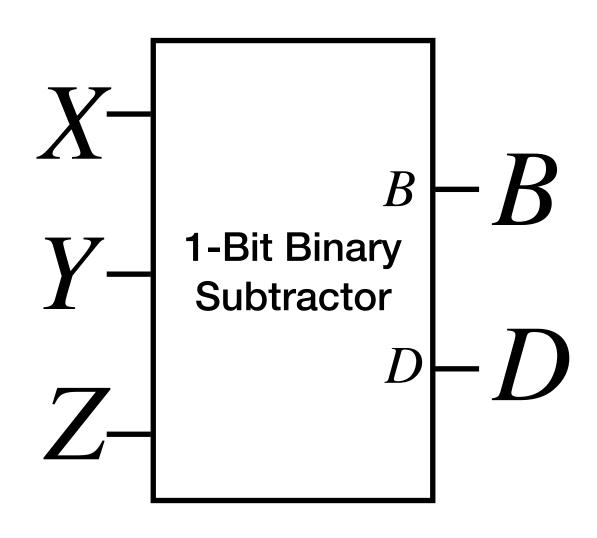

## Unsigned 1-bit Binary Subtraction

- Input: Minuend X and Subtrahend YPrevious borrow Z

- Output: Last borrow *B*, difference *D*

Borrows

Minuend X

Subtrahend Y

Difference **D**

Input Output

#### P1 Subtraction

#### Unsigned 1-bit Binary Subtraction

- Input: Minuend X and Subtrahend YPrevious borrow Z

- Output: Last borrow *B*, difference *D*

| X | Y | Ζ | B | D |

|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 | 1 |

| 0 | 1 | 0 | 1 | 1 |

| 0 | 1 | 1 | 1 | 0 |

| 1 | 0 | 0 | 0 | 1 |

| 1 | 0 | 1 | 0 | 0 |

| 1 | 1 | 0 | 0 | 0 |

| 1 | 1 | 1 | 1 | 1 |

#### **Unsigned 1-bit Binary** Subtraction

- Implementation using 3-to-8 Decoder

- $B = \Sigma m(1,2,3,7)$

- $D = \Sigma m(1,2,4,7)$

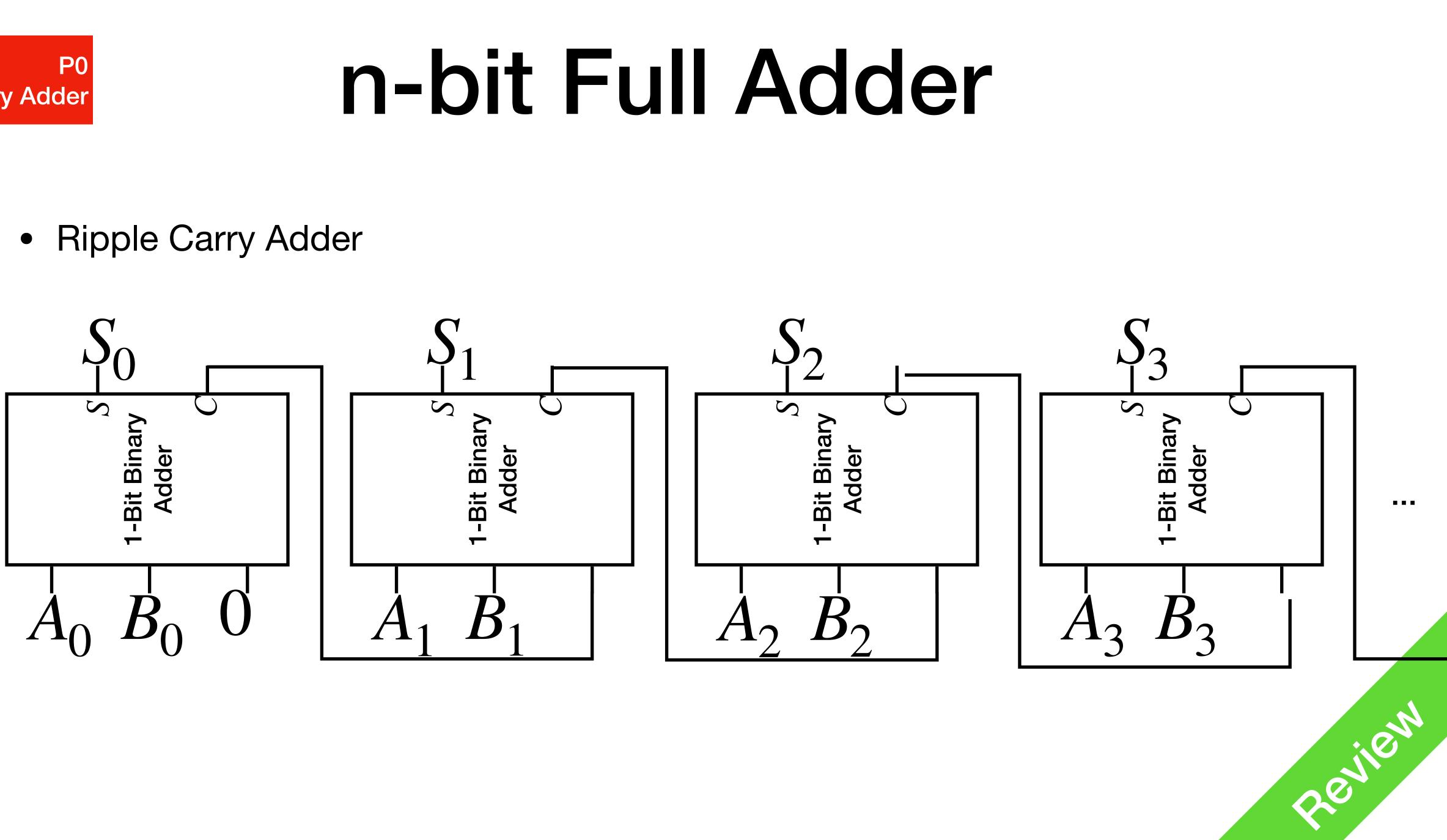

#### Unsigned Binary Subtraction

- Input: Minuend and Subtrahend Previous borrow

- Output: Last borrow, difference

Technology

• 1 bit Unsigned Subtractor

# BorrowsBorrowsConstrained of Constrained of Con

#### Unsigned Binary Subtraction

Technology

• 1 bit Unsigned Subtractor

## $\begin{array}{ccc} B & Z \\ 0000100 \\ Minuend X_{0:n-1} & 10110 \end{array} \quad \begin{array}{c} Input \\ 0utput \end{array}$ Subtrahend $Y_{0:n-1} - 10011 \\ Difference D_{0:n-1} & 00011 \end{array}$

## Hardware Description Language

VHDL (VHSIC-HDL): Very High Speed Integrated Circuit Hardware Description Language

#### What is HDL

- Designing complex circuits using logic circuit diagrams is inefficient

- Hardware Description Language

- Like programming language, describes hardware structures and behaviours

- More efficient

- Common languages

- Verilog

- VHDL

| File | View Help           |        |

|------|---------------------|--------|

|      | New                 | Ctrl+N |

|      | Open                | Ctrl+0 |

|      | Examples            |        |

|      | Page Setup          |        |

|      | Print Setup         |        |

|      | 1 Circuit2.cct      |        |

|      | 2 3-bit Counter.cct |        |

|      | 3 Simulate.CCT      |        |

| _    | Exit                | Alt+F4 |

| New                           |   | ОК     |

|-------------------------------|---|--------|

| Circuit                       | ~ |        |

| Text Document                 |   | Cancel |

| Device Symbol<br>Model Wizard |   |        |

| Sim | ulation Model Wizard                                                                                           |

|-----|----------------------------------------------------------------------------------------------------------------|

|     |                                                                                                                |

|     | Source                                                                                                         |

|     | Create a new, empty model                                                                                      |

|     | This selection will allow you to<br>will generate a shell for the mo                                           |

|     | O Select an existing file Browse                                                                               |

|     | None<br>Use this setting to create a syn<br>attached. You can use it just f<br>purposes or attach a model late |

|     | Destination                                                                                                    |

|     | Open the new model as an indep                                                                                 |

|     | Create a new symbol with the sp                                                                                |

|     | C Attach the new model to the sele                                                                             |

|     |                                                                                                                |

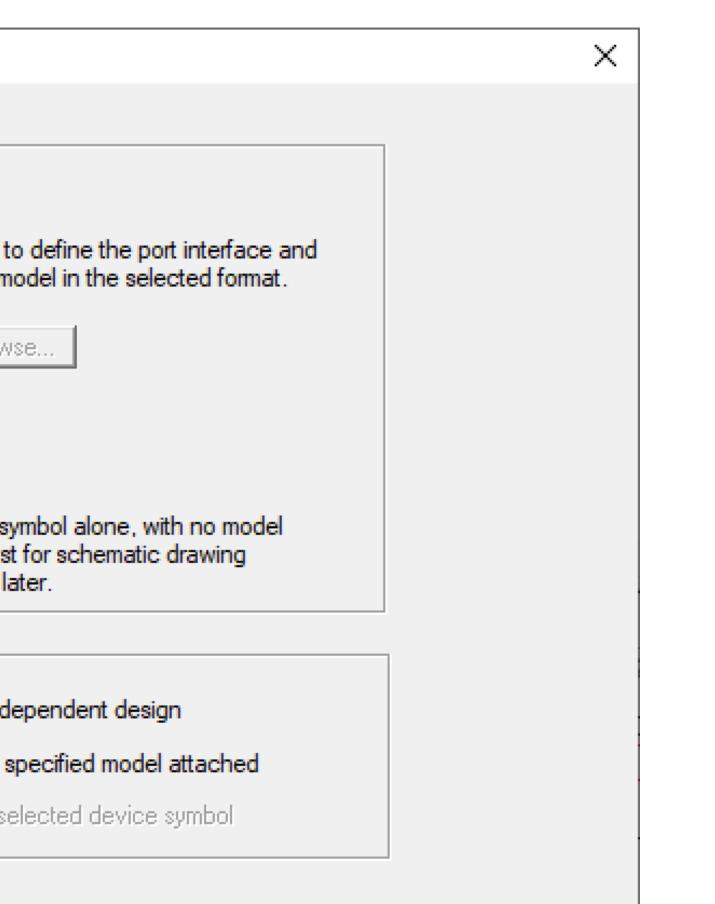

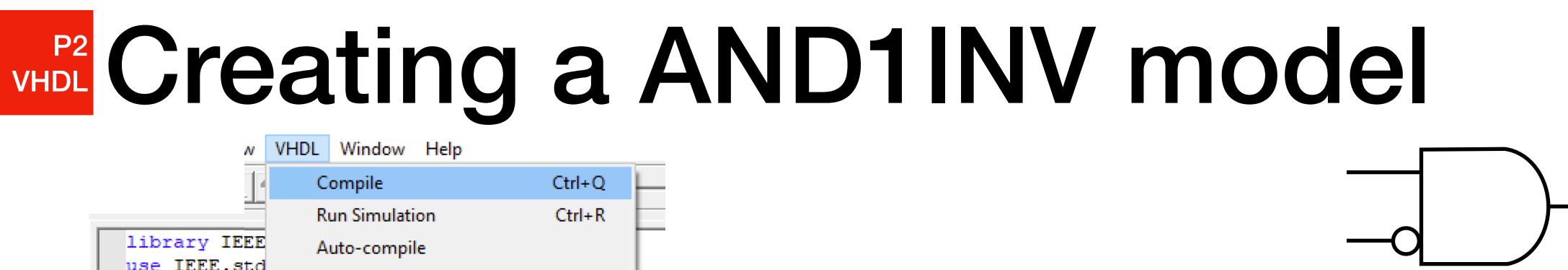

## VHDL Creating a A

| ourc    | e                                                                                                                                                    |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------|

| Θ       | Create a new, empty model                                                                                                                            |

|         | This selection will allow you to define the port interface and<br>will generate a shell for the model in the selected format.                        |

| 0       | Select an existing file Browse                                                                                                                       |

| 0       | None                                                                                                                                                 |

|         | Use this setting to create a symbol alone, with no model<br>attached. You can use it just for schematic drawing<br>purposes or attach a model later. |

| )estir  | nation                                                                                                                                               |

| 0       | Open the new model as an independent design                                                                                                          |

| $\odot$ | Create a new symbol with the specified model attached                                                                                                |

| ~       | Attach the new model to the selected device symbol                                                                                                   |

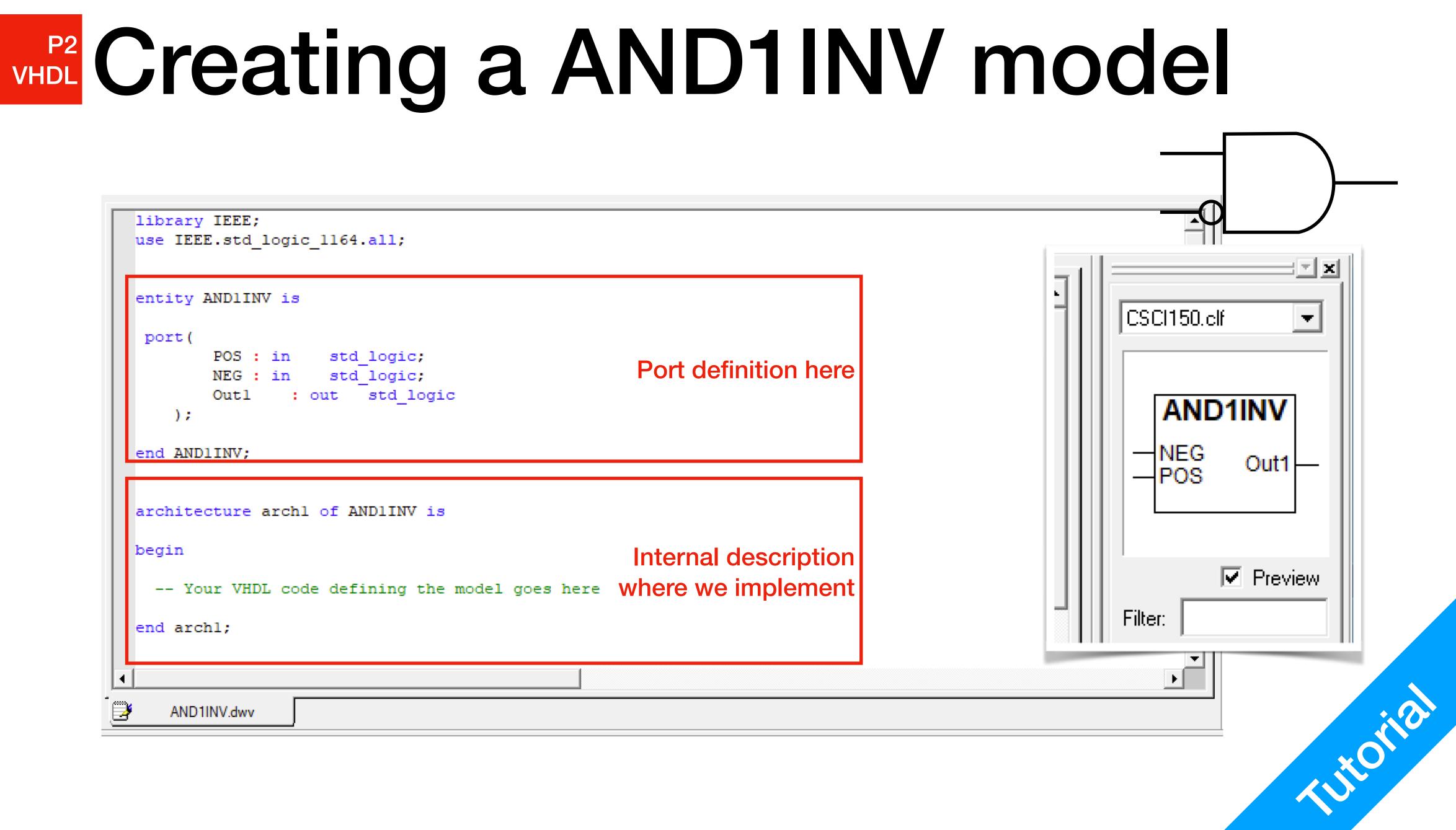

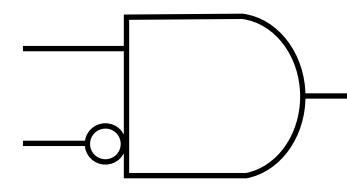

|   | <b>ND1INV model</b>                                                                                                                                       |   |  |

|---|-----------------------------------------------------------------------------------------------------------------------------------------------------------|---|--|

| × |                                                                                                                                                           |   |  |

|   | Model Info                                                                                                                                                | × |  |

|   | Select the desired model type           Structural Circuit         Create a VHDL language file which can be used to describe the function of this device. |   |  |

|   | Enter a name for the new model AND1INV                                                                                                                    |   |  |

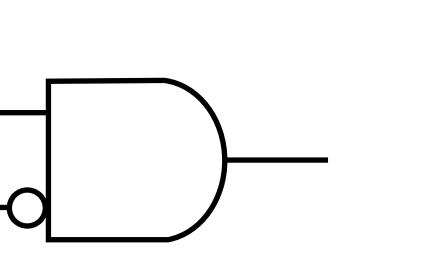

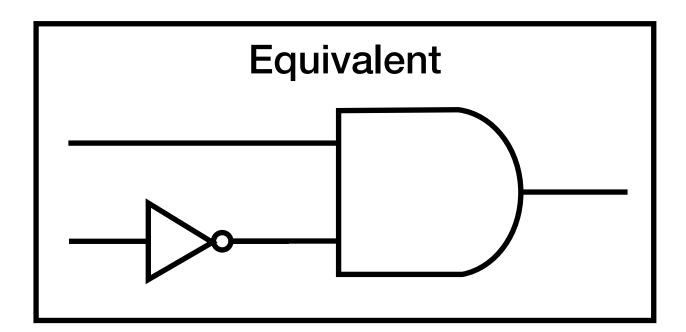

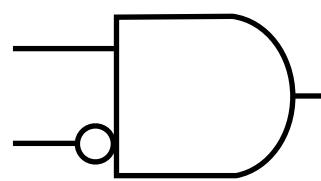

- This is where you define all inputs and outputs

- Input: POS

- Input: NEG

- Output: Out1

| odel Port Interface                                                                                                                                                                            |                                              | $\times$ |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|----------|

| Use the controls at right to add pins to the interface list. NOTE: If you are attaching this model to an existing device symbol, the interface list must exactly match the pins on the symbol. | Function<br>Input<br>Output<br>Bidirectional |          |

|                                                                                                                                                                                                | << Add Single Bit                            |          |

|                                                                                                                                                                                                | Left Bit Number                              |          |

|                                                                                                                                                                                                | << Add Vector                                |          |

| Drag and drop to re-order items in the list                                                                                                                                                    | >> Remove                                    |          |

|                                                                                                                                                                                                |                                              |          |

3. Type the Name and select the Function accordingly, then press Add Single Bit, click Finish to create the model file.

- This is where you define all inputs and outputs

- Input: POS

- Input: NEG

- Output: Out1

| Use the controls at right to add pins to the interface list. NOTE: If you are attaching this model to an existing device symbol, the interface list must exactly match the pins on the symbol. | Function<br>© Input<br>© Output<br>© Bidirectional |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|

|                                                                                                                                                                                                | Name                                               |

| e Func Left Right                                                                                                                                                                              | << Add Single Bit                                  |

| In<br>Out                                                                                                                                                                                      | Vector<br>Left Bit Number                          |

|                                                                                                                                                                                                | Right Bit Number                                   |

|                                                                                                                                                                                                | << Add Vector                                      |

| Drag and drop to re-order items in the list                                                                                                                                                    | >> Remove                                          |

|                                                                                                                                                                                                |                                                    |

3. Type the Name and select the Function accordingly, then press Add Single Bit, click Finish to create the model file.

#### Pin Locations

You can now specify where on the symbol you would like the pins to be placed. To move pins, just drag and drop between the boxes representing the left, top, right and bottom of the symbol.

| Left pins<br>NEG<br>POS | Top pins<br>(left to right)    | Right pins Out 1 |

|-------------------------|--------------------------------|------------------|

|                         |                                | Symbol Label     |

|                         | Bottom pins<br>(left to right) | AND1INV          |

4. The programme will ask you for Pin Location assignment. Just click Next.

$\times$

```

library IEEE;

use IEEE.std_logic_ll64.all;

entity ANDIINV is

port (

POS : in std_logic;

NEG : in std logic;

Outl : out std logic

);

end AND1INV;

architecture archl of ANDLINV is

begin

-- Your VHDL code defining the model goes here where we implement

end arch1;

AND1INV.dwv

```

```

library IEEE;

use IEEE.std logic ll64.all;

entity ANDIINV is

port (

POS : in

std logic;

NEG : in

std logic;

: out std logic

Outl

);

end AND1INV;

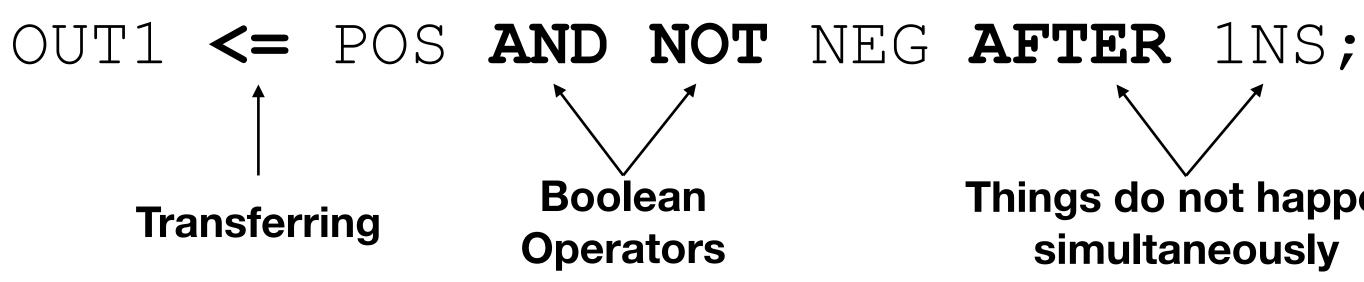

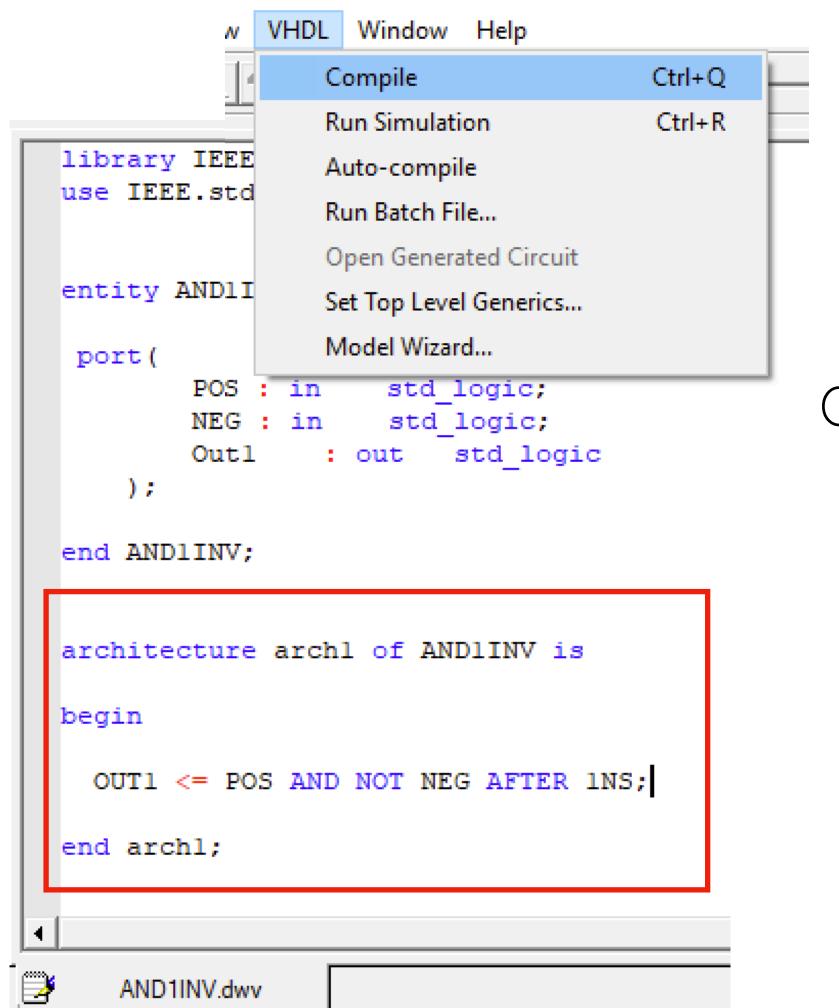

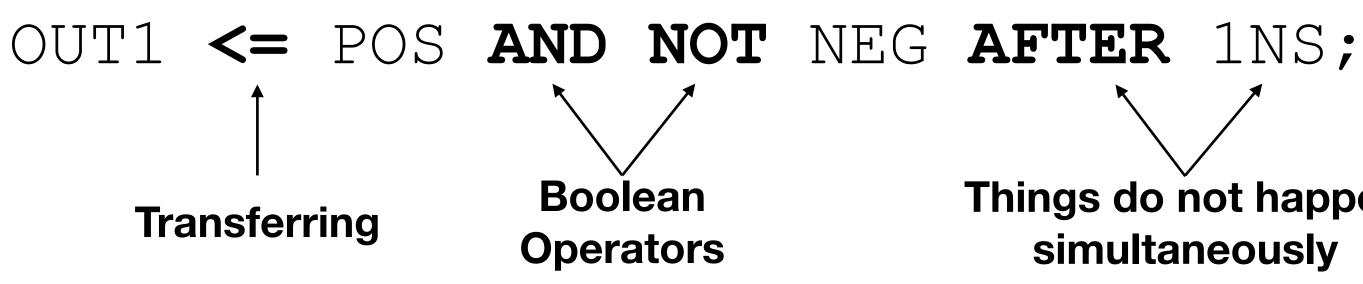

architecture archl of AND1INV is

begin

OUT1 <= POS AND NOT NEG AFTER 1NS;

end archl;

4

Þ

AND1INV.dwv

```

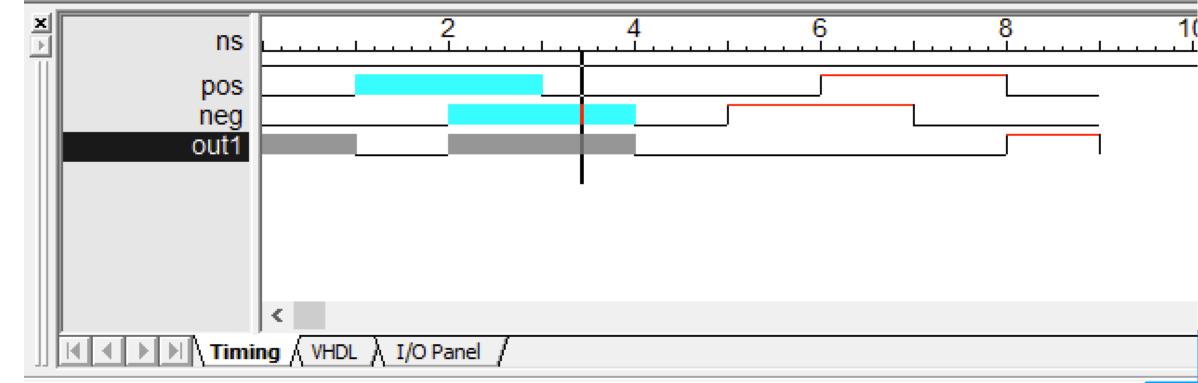

5. Type: OUT1 <= POS AND NOT NEG AFTER 1NS; This is the Boolean description of the OUT1 port

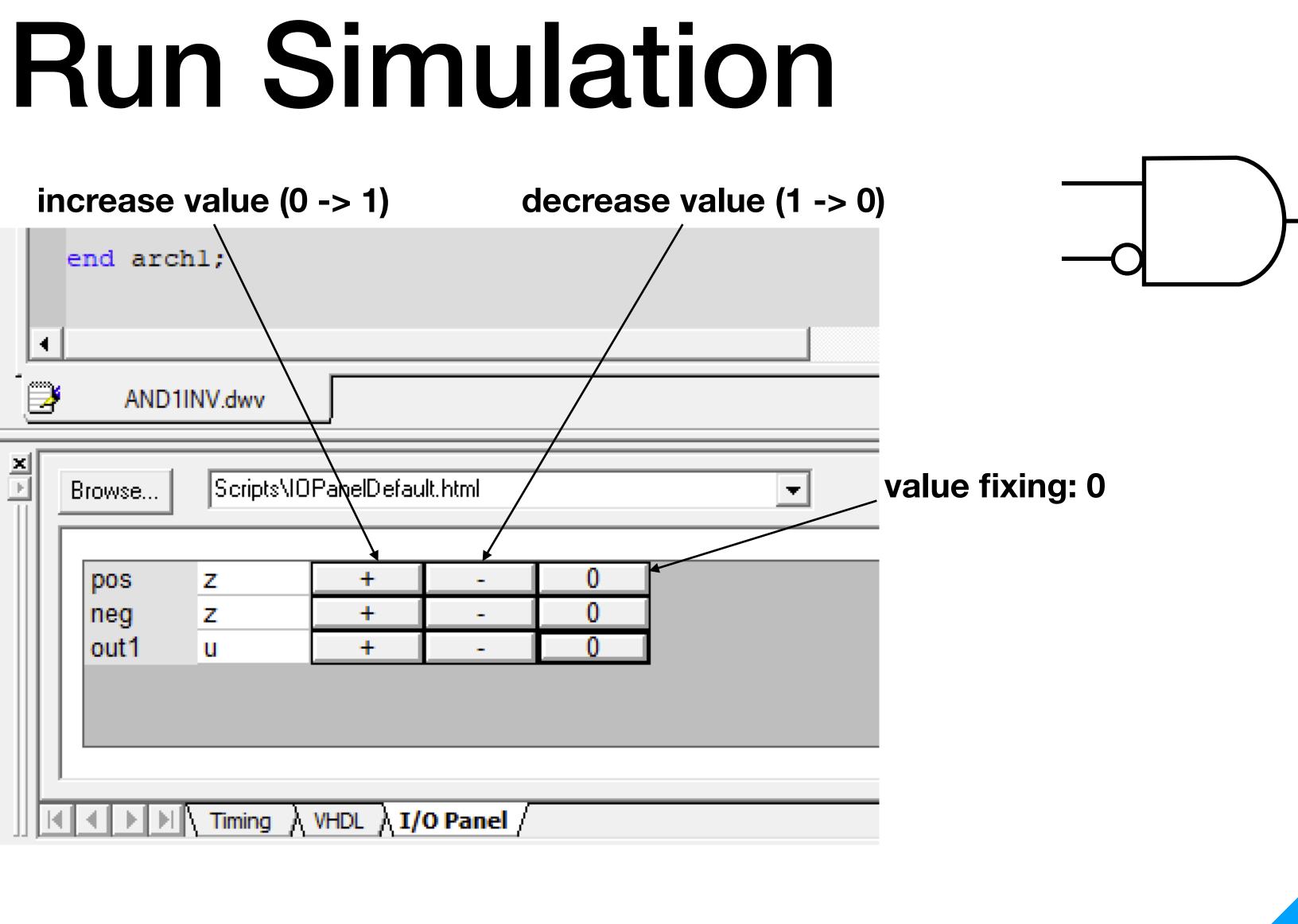

#### **Run Simulation**

**P2** VHDL

#### increase value (0 -> 1)

|   | e              | nd ar      | ch   | 1;      |    |      |

|---|----------------|------------|------|---------|----|------|

|   | <u>່</u><br>"ຮ | ANI        |      | IV.dwv  |    |      |

| 2 | 3              | AINL       | 7111 | vwb.vv  |    |      |

| × | E              | fowse      |      | Scripts | MO | Pane |

|   | Γ              | DOG        |      | -       |    |      |

|   |                | pos<br>neg |      | z<br>z  |    |      |

|   |                | out1       |      | u       | 4  |      |

|   |                |            |      |         |    |      |

|   |                |            |      |         |    |      |

|   | K              |            | N    | Timing  | λ  | VHD  |

**P2** VHDL

#### 7. Play with the buttons in the I/O panel

## **Run Simulation**

| • | end arc | :hl;        |             |           |   |   |

|---|---------|-------------|-------------|-----------|---|---|

|   | AND     | 1INV.dwv    |             |           |   |   |

|   | Browse  | Scripts\IC  | )PanelDefai | ult.html  |   | - |

|   |         |             |             |           | - |   |

|   | pos     | z           | +           | -         | 0 |   |

|   | neg     | z           | +           | -         | 0 |   |

|   | out1    | u           | +           | -         | 0 |   |

|   |         |             |             |           |   |   |

|   |         |             |             |           |   |   |

|   | ,       |             |             |           |   |   |

|   |         | \ Timing  } |             | O Panel / |   |   |

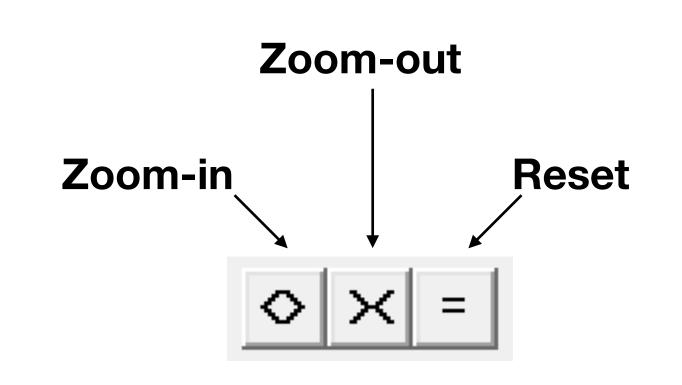

8. Changes are reflected in the Timing Diagram. Use Zoom panel to Zoom In and Out

#### Exe1: 1-bit Half Adder

- Create a new component in VHDL called HalfAdder1

- Input: X, Y

**P2**

VHDL

- Output: S, C

- **Don't use** AFTER

#### architecture arch1 of HalfAdder is

#### begin

$S \ll X X OR Y;$

$C \ll X AND Y;$

end arch1;

#### Exe1: 1-bit Half Adder