## CSCI 150 Introduction to Digital and Computer System Design Lecture 4: Sequential Circuit Flashback

Jetic Gū 2020 Winter Semester (S1)

# Overview

- Focus: Sequential Circuit Exercises

- Architecture: von Neumann

- Textbook v4: Ch5; v5: Ch4

- Core Ideas:

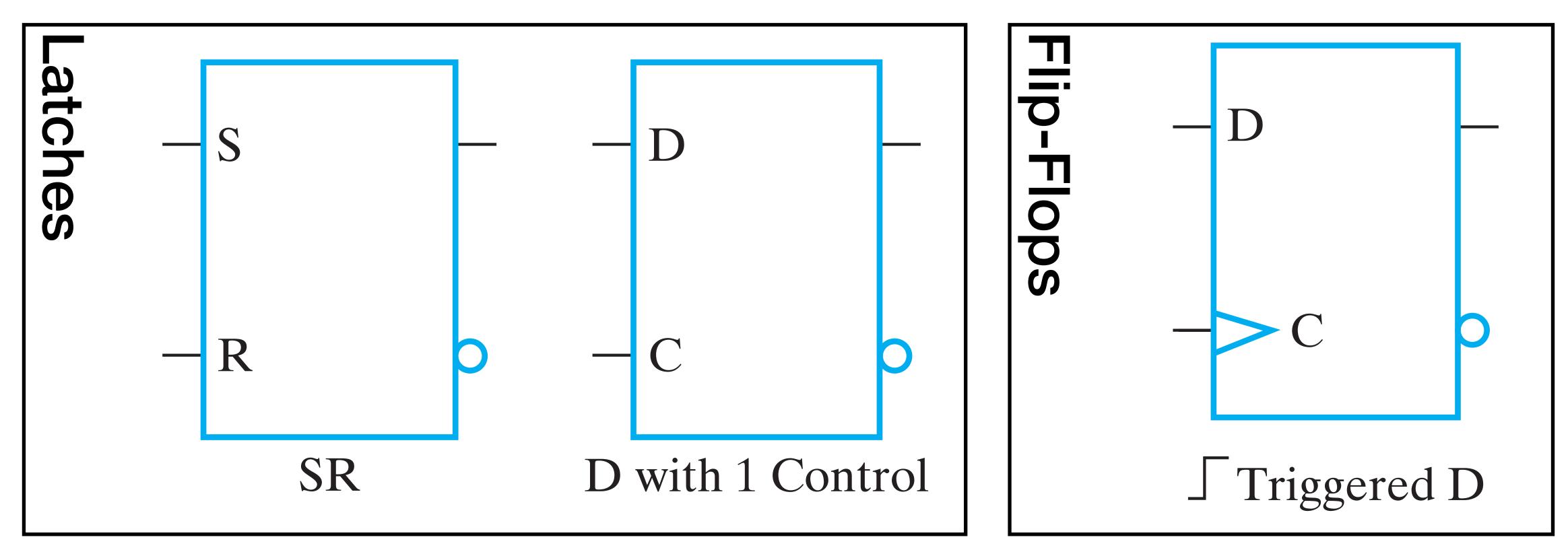

- 1. Latches and Flip-Flips

- 2. State Diagram and State Table

- 3. Exercise

# How to study for CSCI 150

- You have to study

- Attend lectures and pay attention

- Do you OWN Homework and Labs

- ASK if you have questions

# Latches and Flip-Flops

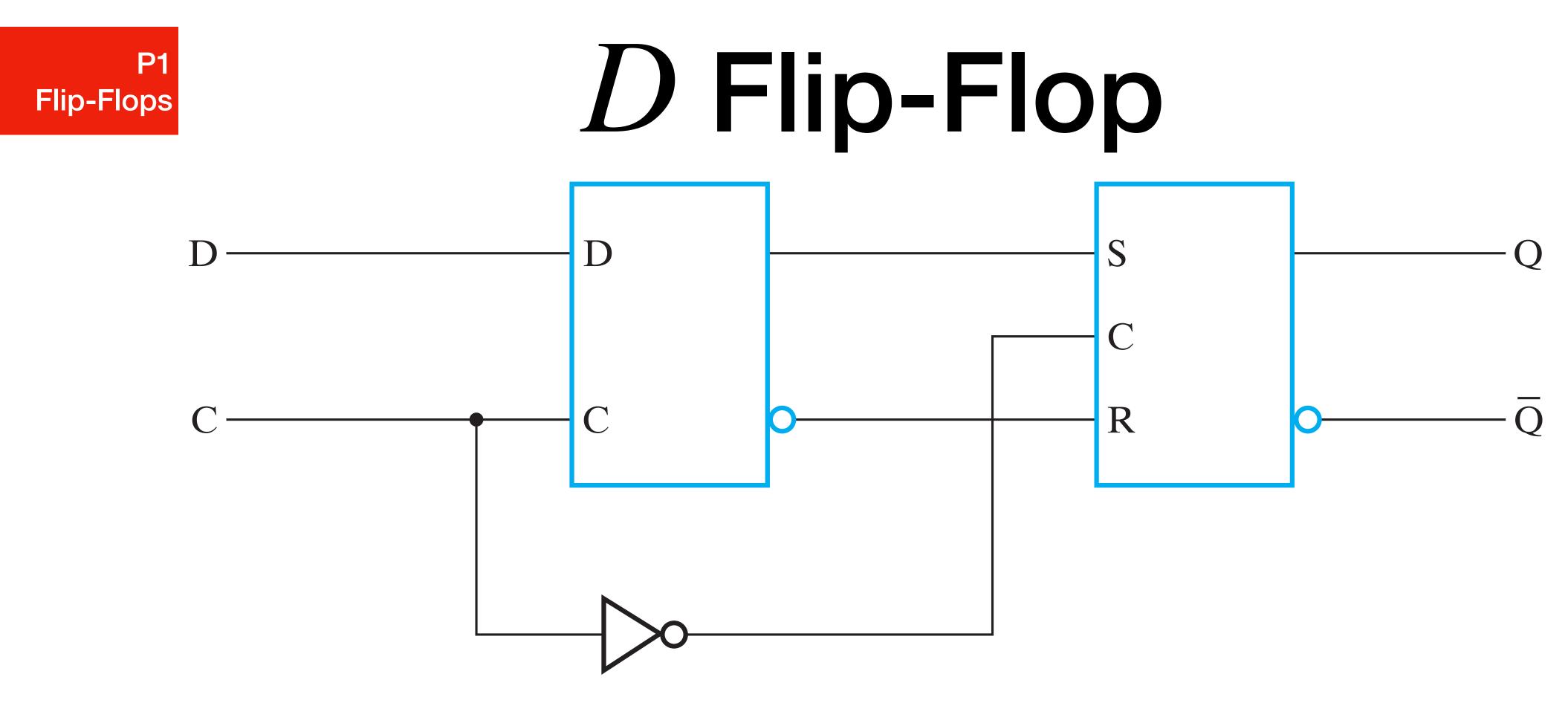

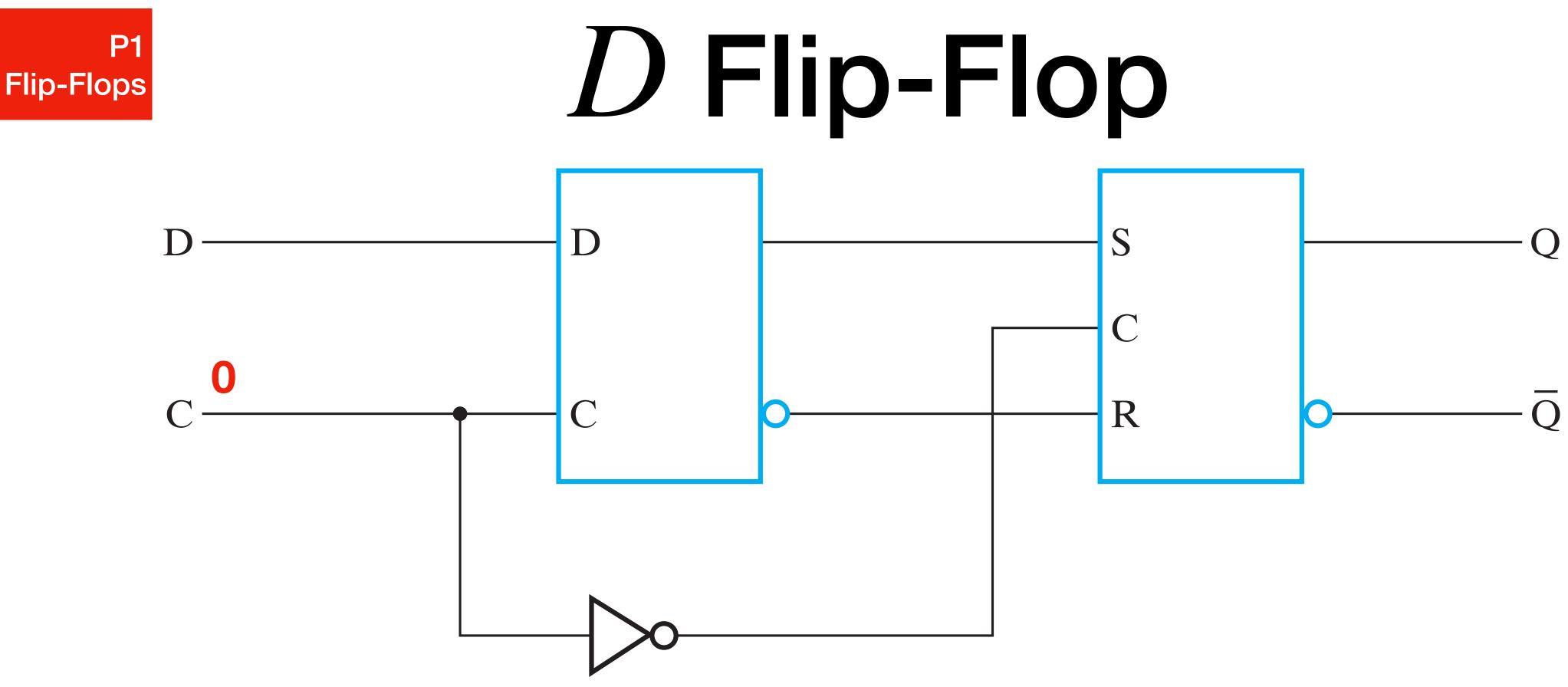

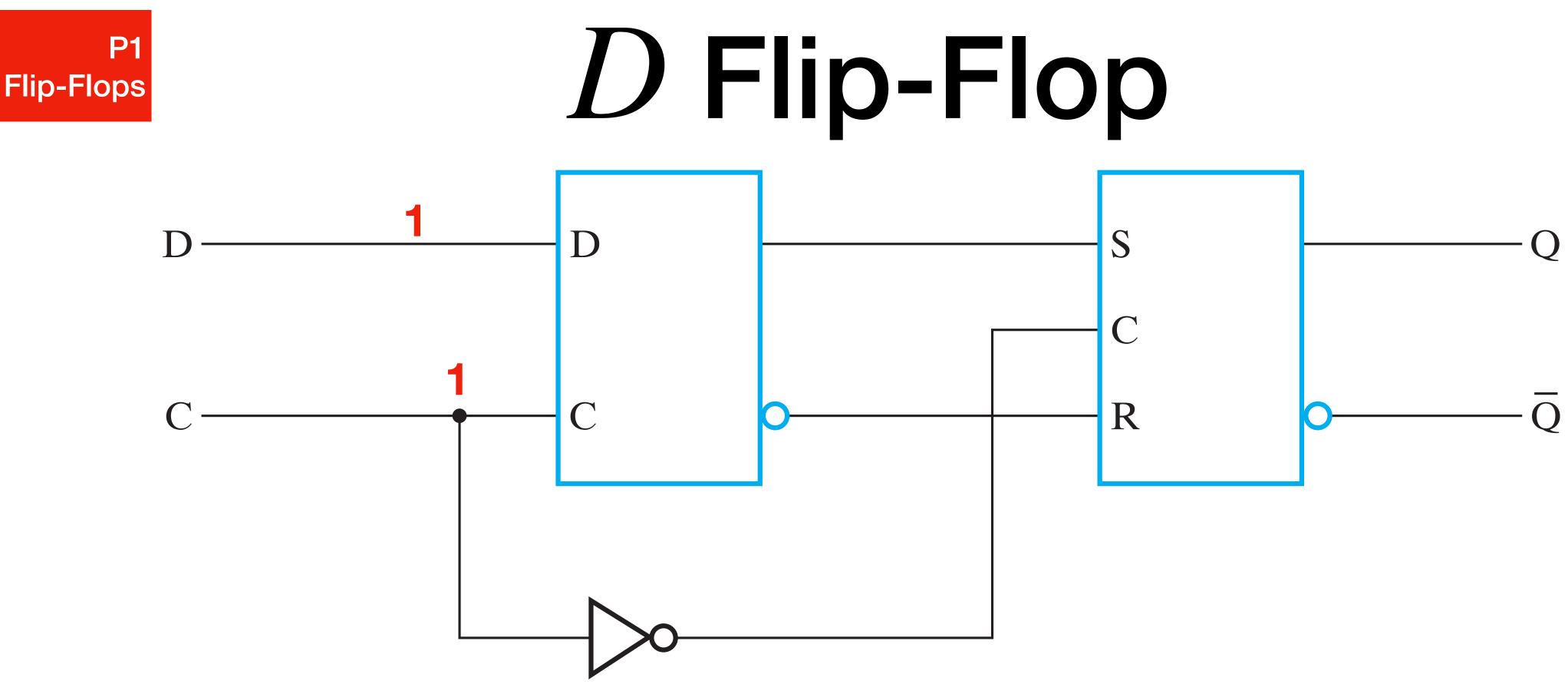

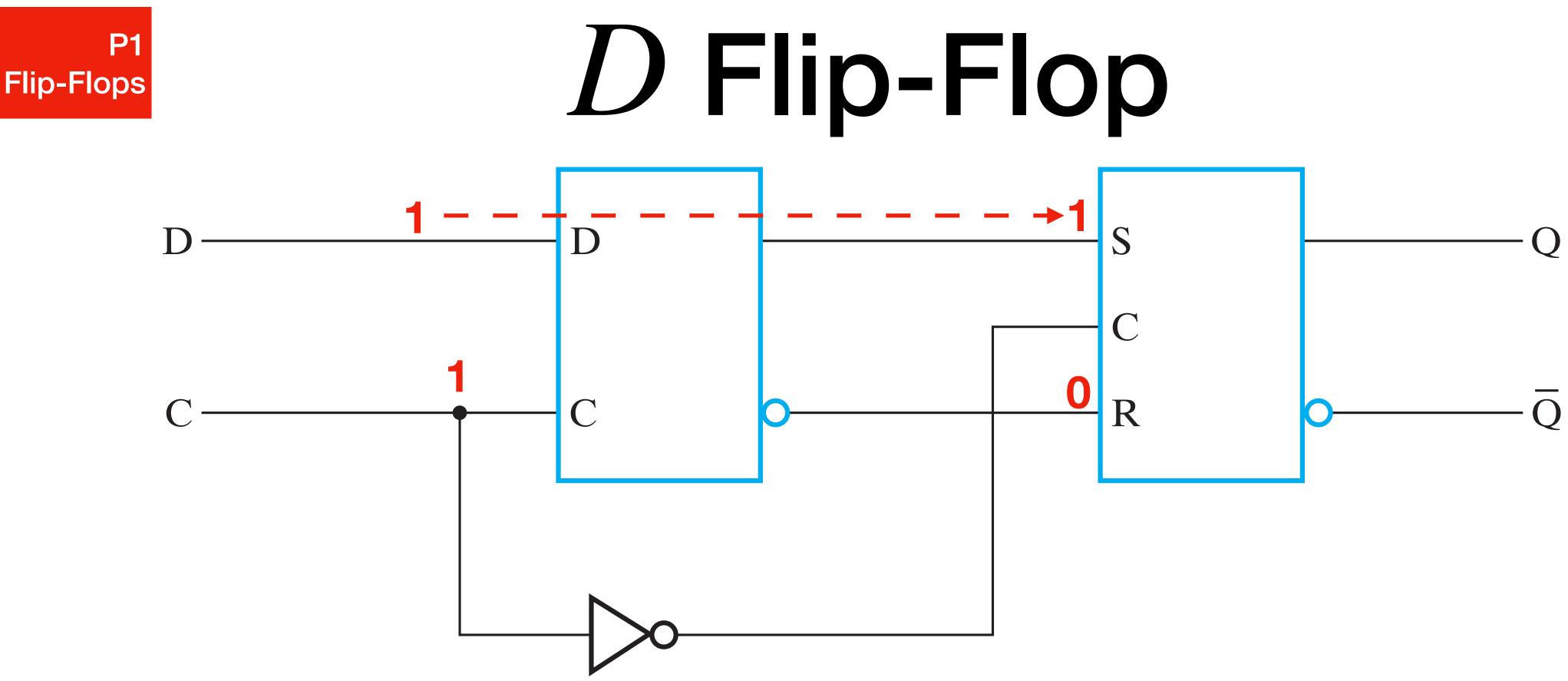

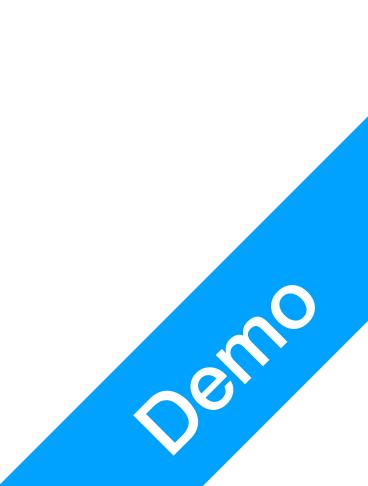

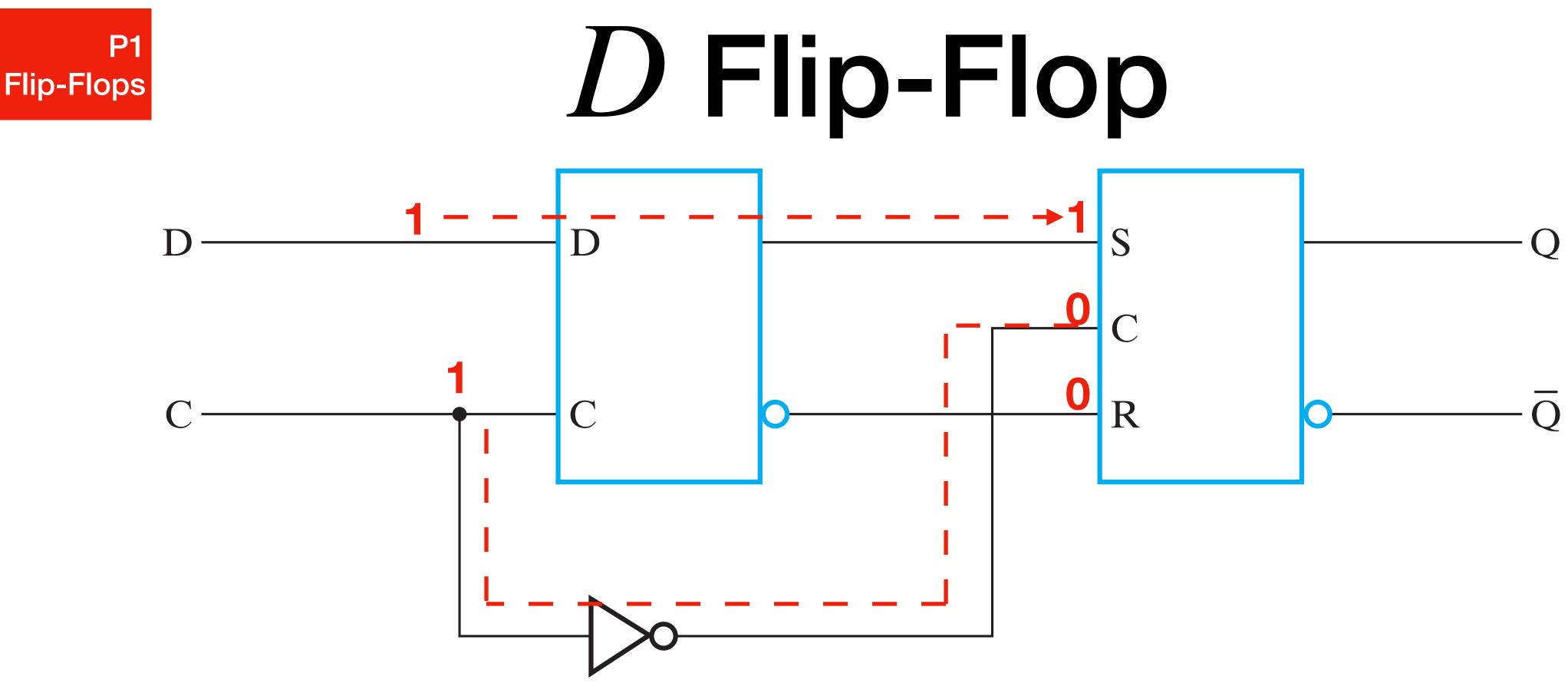

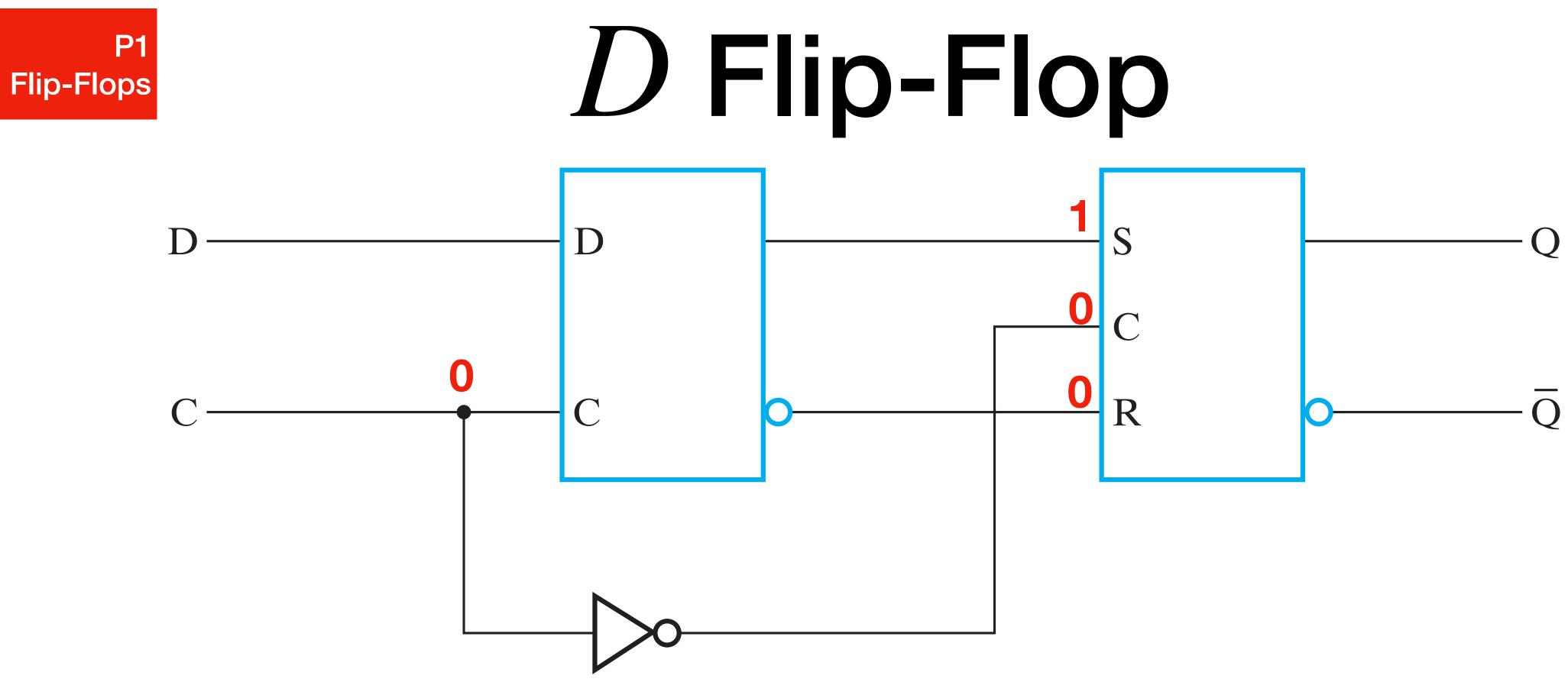

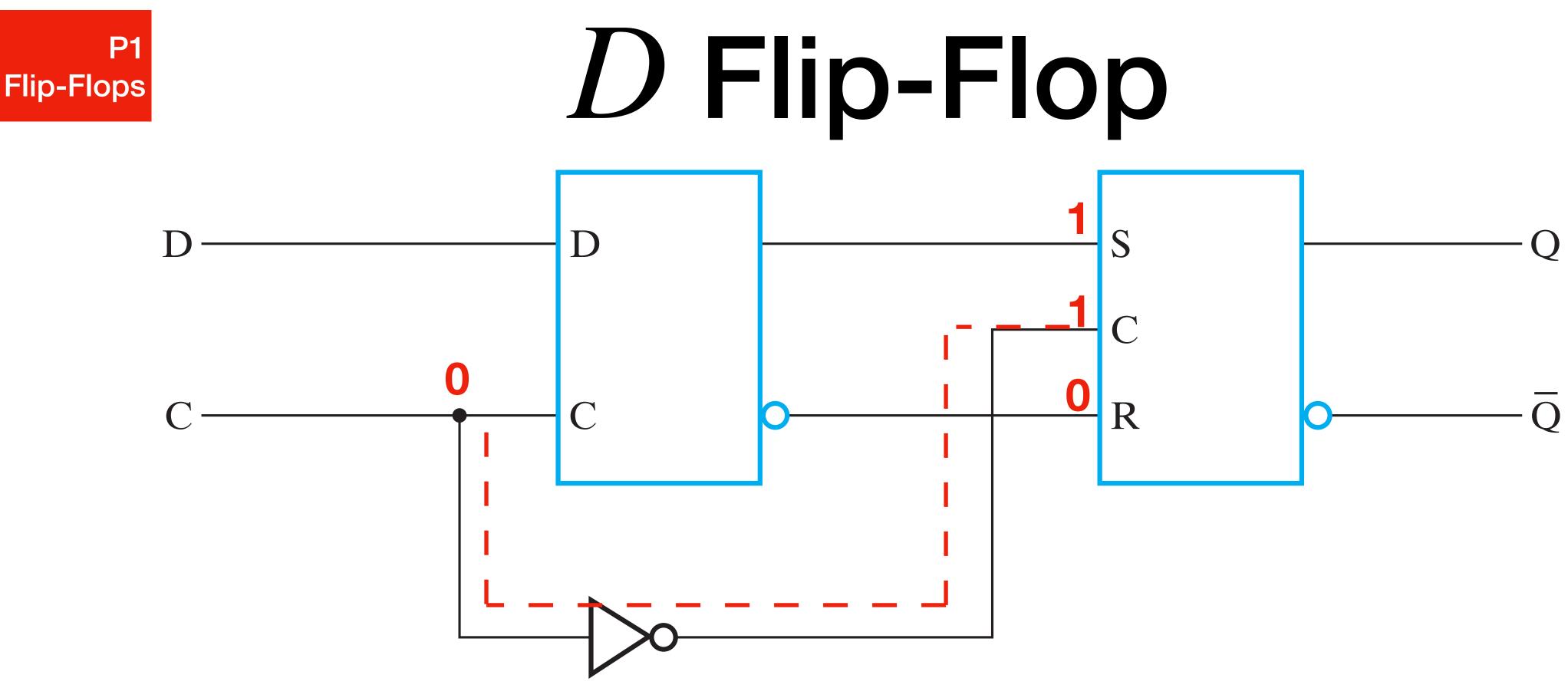

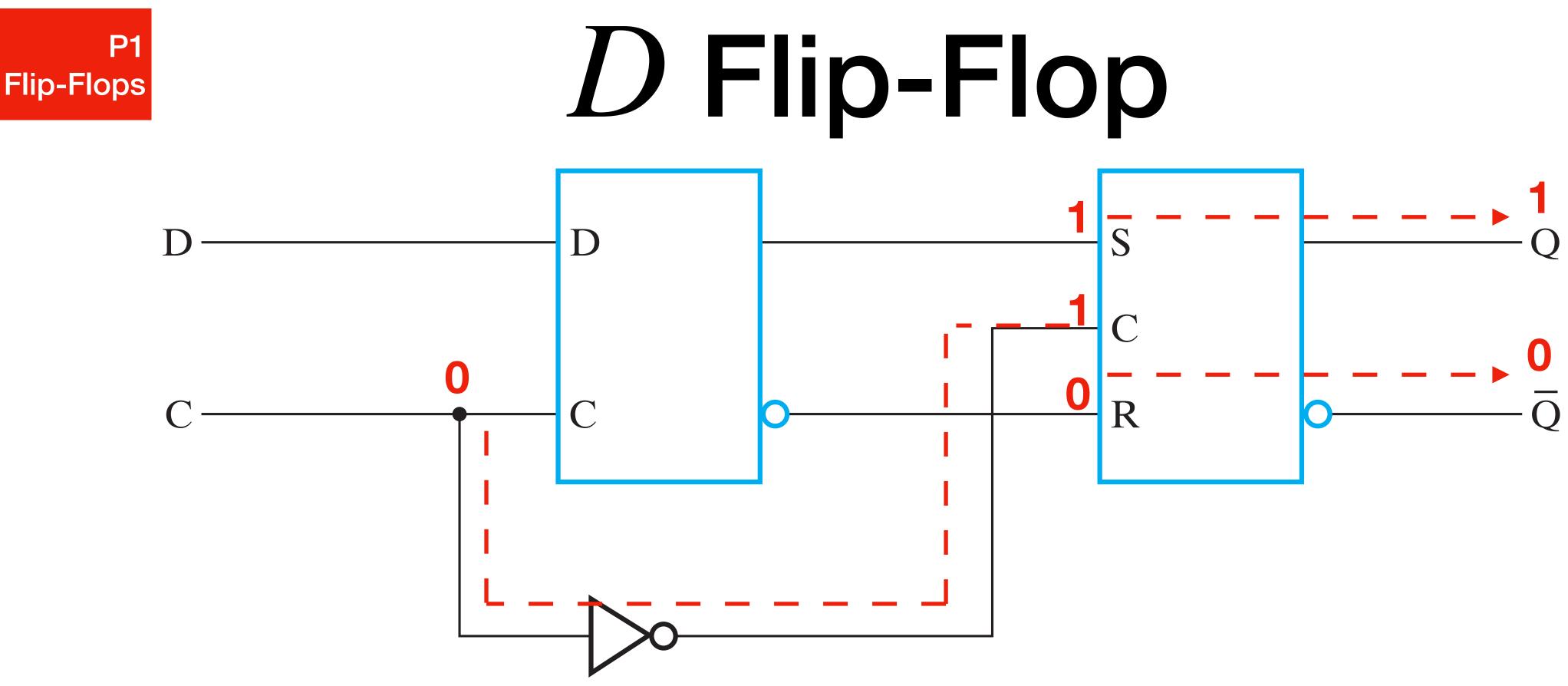

### **P1** Flip-Flops

# Latches and Flip-Flops

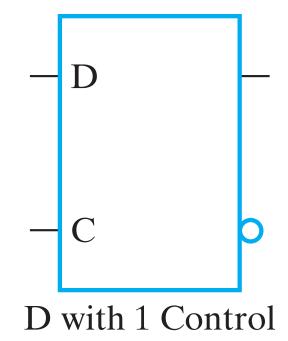

- Latches are Transparent

- Internal values change immediately after C pin receives positive signal

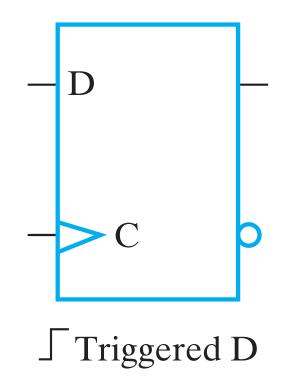

- Flip-Flops

- Two latches: one changes immediately, the other changes at the next step

- Replaces SR master in SR Master-Slave with D master Latch

- Negative Edge Triggered D (Flip-Flop):  $C = 1 \rightarrow C = 0$

- Replaces SR master in SR Master-Slave with D master Latch

- Negative Edge Triggered D (Flip-Flop):  $C = 1 \rightarrow C = 0$

- Replaces SR master in SR Master-Slave with D master Latch

- Negative Edge Triggered D (Flip-Flop):  $C = 1 \rightarrow C = 0$

- Replaces SR master in SR Master-Slave with D master Latch

- Negative Edge Triggered D (Flip-Flop):  $C = 1 \rightarrow C = 0$

- Replaces SR master in SR Master-Slave with D master Latch

- Negative Edge Triggered D (Flip-Flop):  $C = 1 \rightarrow C = 0$

- Replaces SR master in SR Master-Slave with D master Latch

- Negative Edge Triggered D (Flip-Flop):  $C = 1 \rightarrow C = 0$

- Replaces SR master in SR Master-Slave with D master Latch

- Negative Edge Triggered D (Flip-Flop):  $C = 1 \rightarrow C = 0$

- Replaces SR master in SR Master-Slave with D master Latch

- Negative Edge Triggered D (Flip-Flop):  $C = 1 \rightarrow C = 0$

- Replaces SR master in SR Master-Slave with D master Latch

- Negative Edge Triggered D (Flip-Flop):  $C = 1 \rightarrow C = 0$

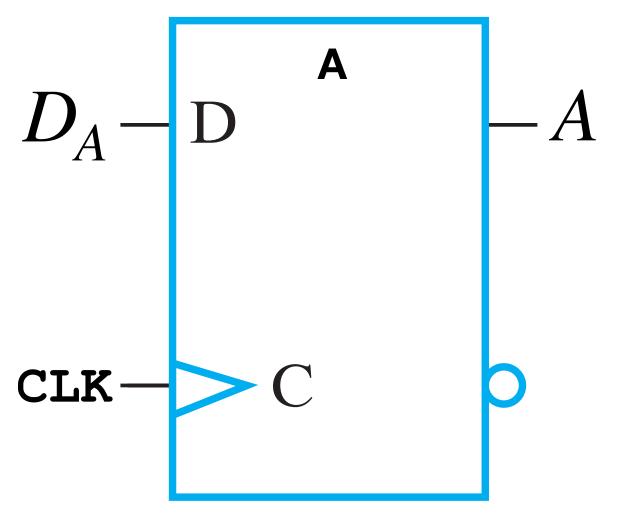

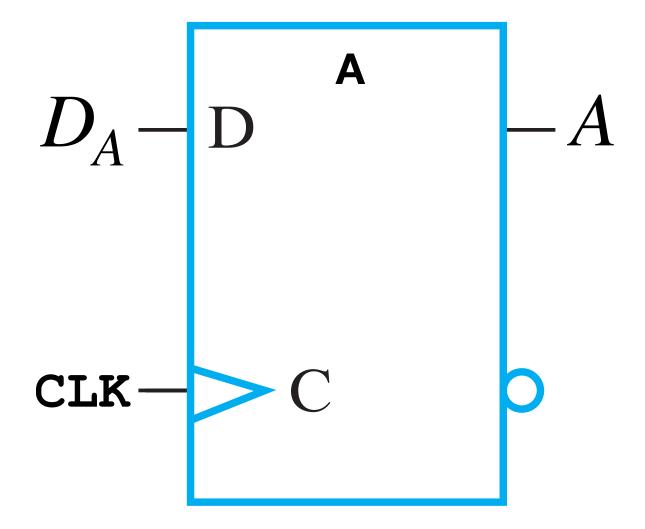

# **Circuit Sequential Circuit Analysis**

- Any D flip-flop named A in a sequential circuit at anytime

- Is giving out A (present state)

- Is receiving  $D_A$  (next state)

- State Table: treat A as input,  $D_A$  as output in Truth Table

# **Circuit Sequential Circuit Analysis**

- When multiple Flip-Flops 0,1,...,n-1 are in a circuit

- the combined internal value  $A_{n-1:0}$ is called the present state

- the combined receiving value  $D_{A_{n-1:0}}$ is called the next state

# State Table

### **Input Pins**

W, X, Y, Z, ...

### **Output Pins**

I, J, K, L, ...

#### **Truth** Table

## State

### **Present State**

### **Input Pins**

A, B, C, D, ...

W, X, Y, Z, ...

S

|          | able               |                                                                     |

|----------|--------------------|---------------------------------------------------------------------|

|          | <b>Output Pins</b> | Next State                                                          |

|          | I, J, K, L,        | D <sub>A</sub> , D <sub>B</sub> , D <sub>C</sub> , D <sub>D</sub> , |

|          |                    |                                                                     |

| tate Tab | le                 |                                                                     |

|          |                    |                                                                     |

- State transitions

- Transition Conditions and Output Conditions

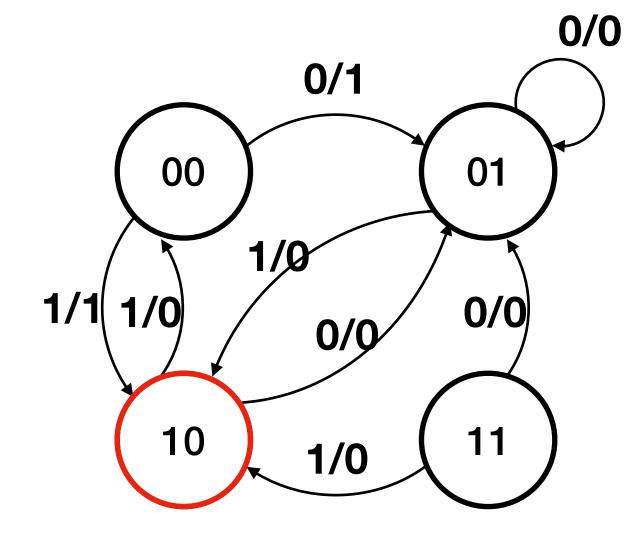

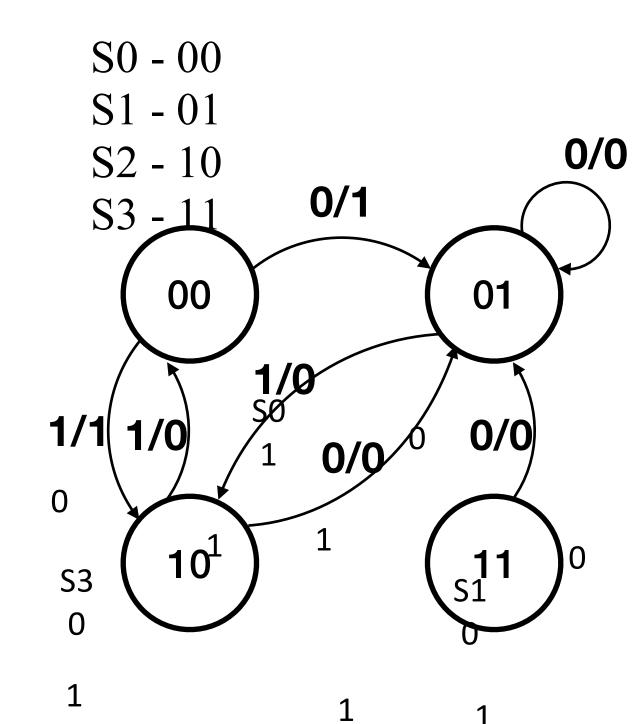

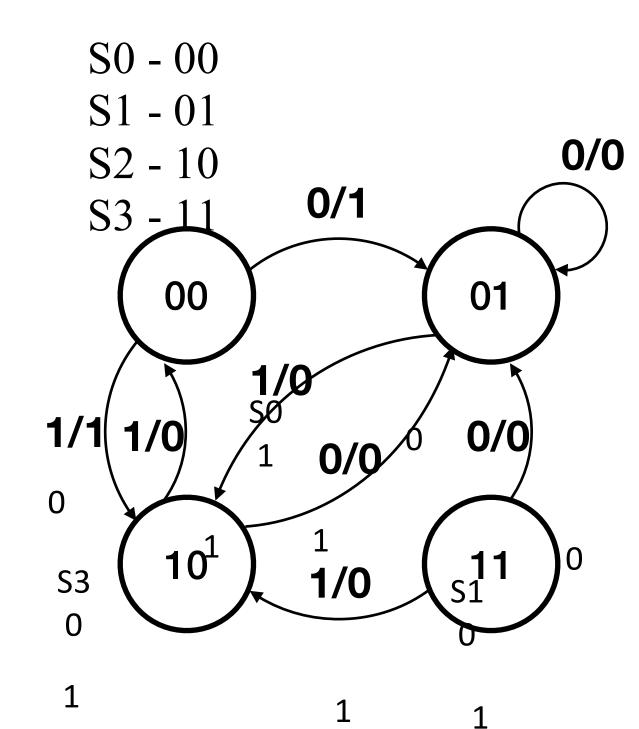

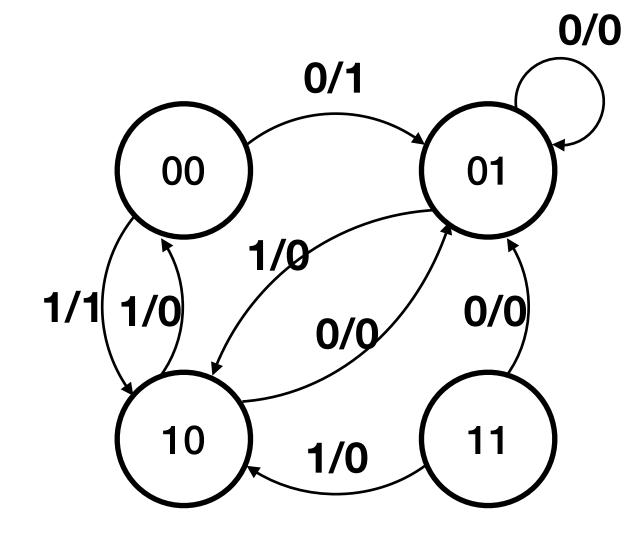

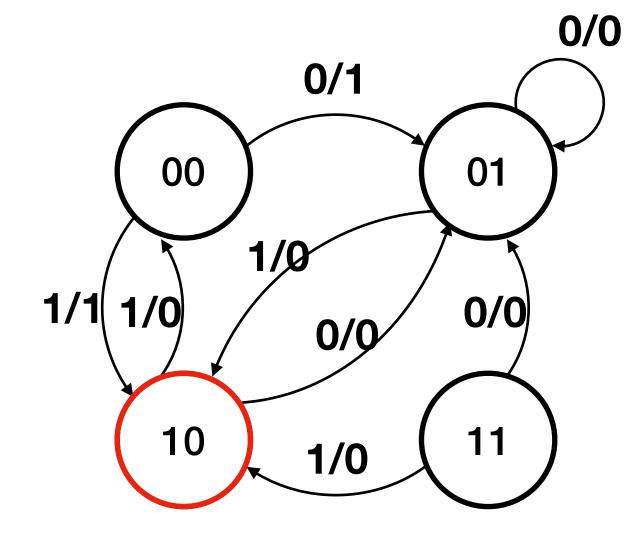

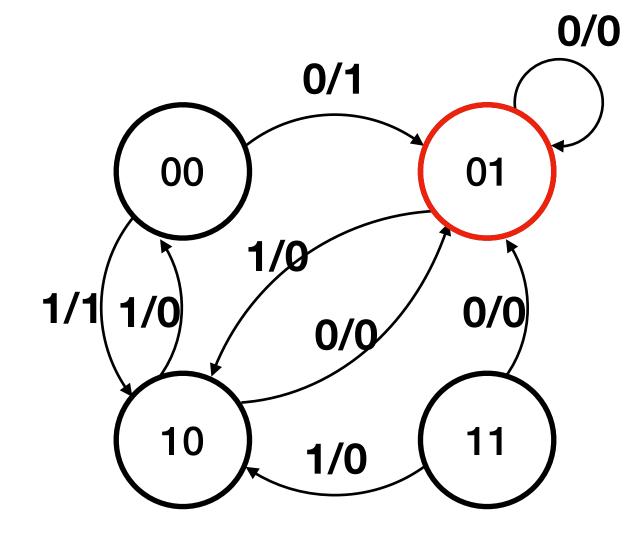

# State Diagram

state

- State transitions

- Transition Conditions and Output Conditions

# State Diagram

state

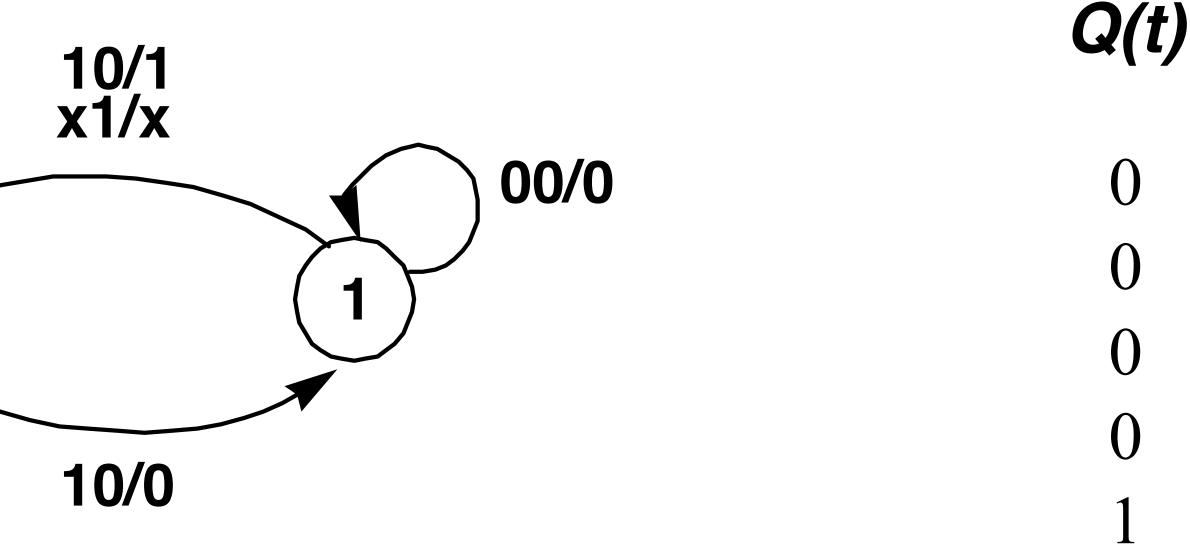

# State Assignments

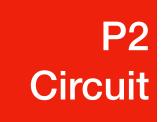

**P2** Circuit

- Given states written in variables A, B, C, D, E...

- Sequential assignment, *n* states, log *n* bits

- A = 000, B = 001, C = 010, D = 011, E = 100, ...

- One-hot assignment, *n* states, *n* bits

- A = 00000001, B = 00000010, C = 00000100, D = 00001000, $E = 00010000, \dots$

- Input equation for  $D_{A_{n-1}}$ , using  $A_{n-1:0}$  as input

- Output equation for actual outputs

# **Equation Determination**

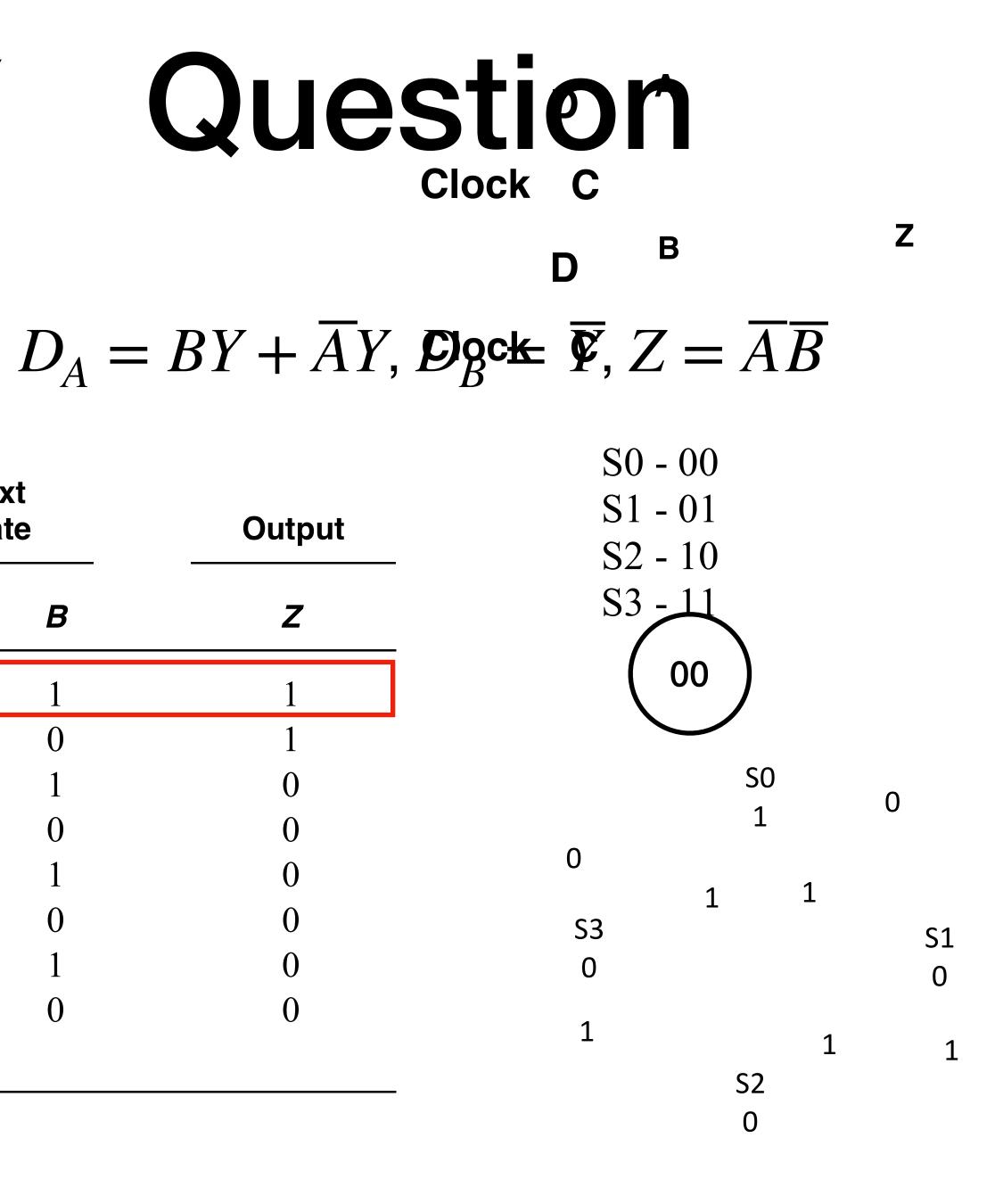

## $D_A = BY + \overline{A}Y, D_R = \overline{Y}, Z = \overline{A}\overline{B}$

### 1. Identify flip-flops (present states and next states), inputs, and outputs

- Present State: AB; Next State:  $D_A D_B$ ; Input: Y; Output: Z;

- 2. Draw State Table / State Diagram

## Question

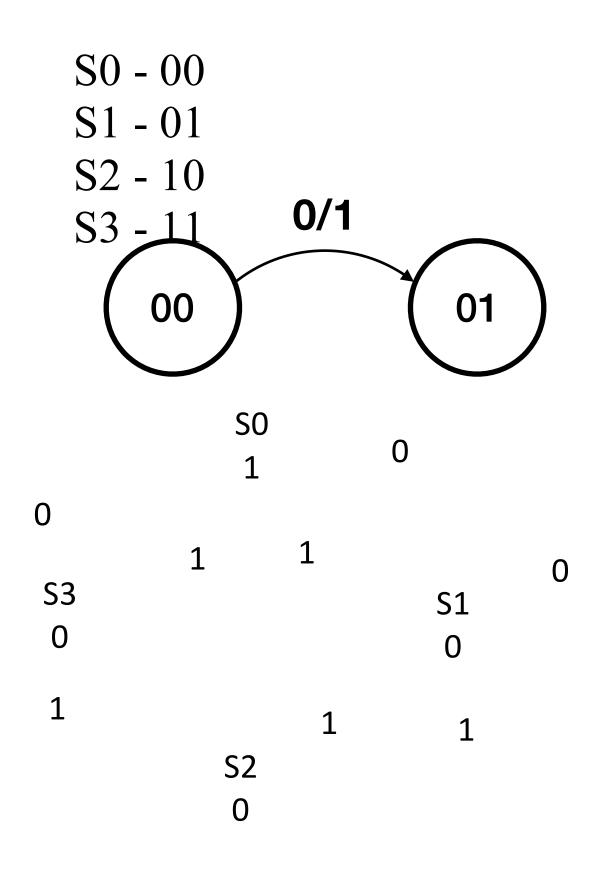

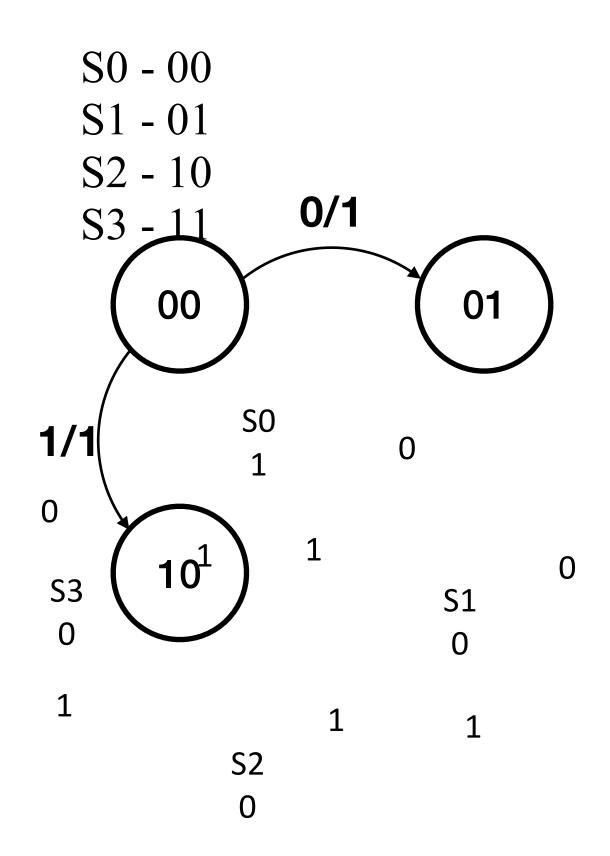

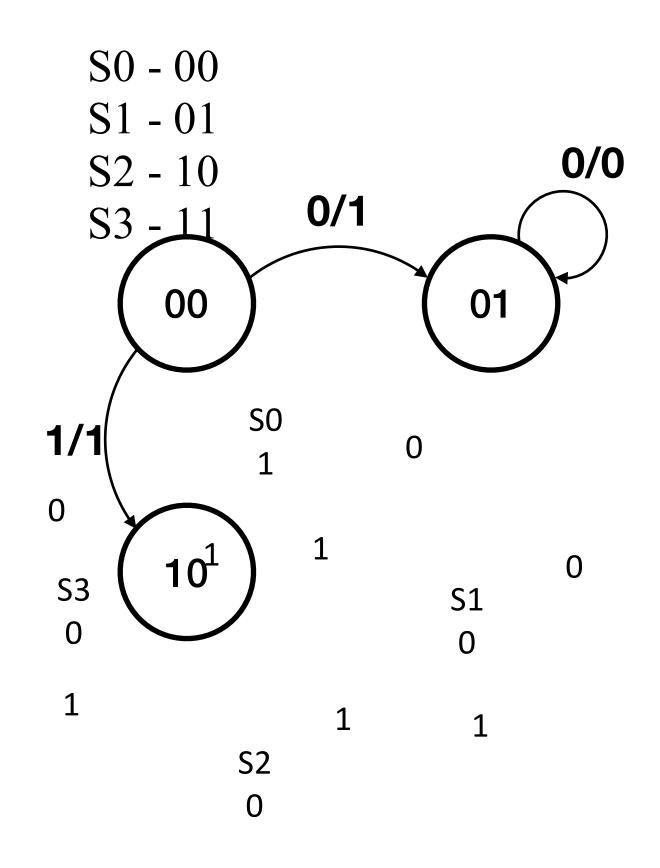

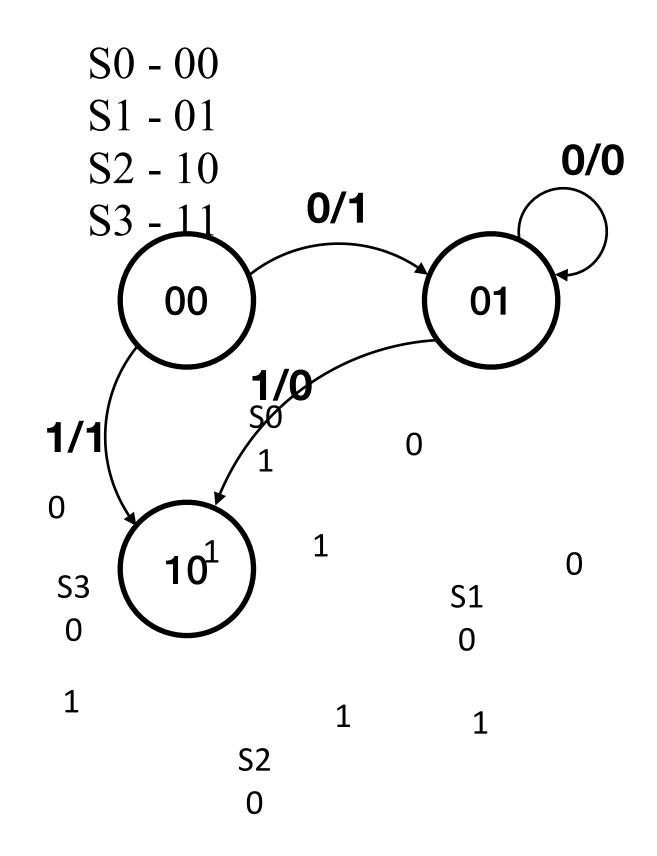

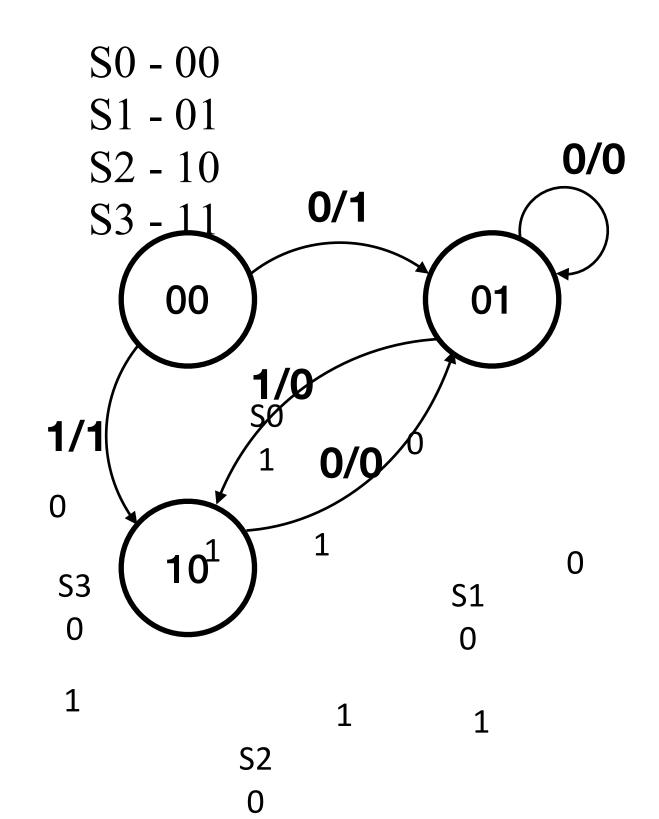

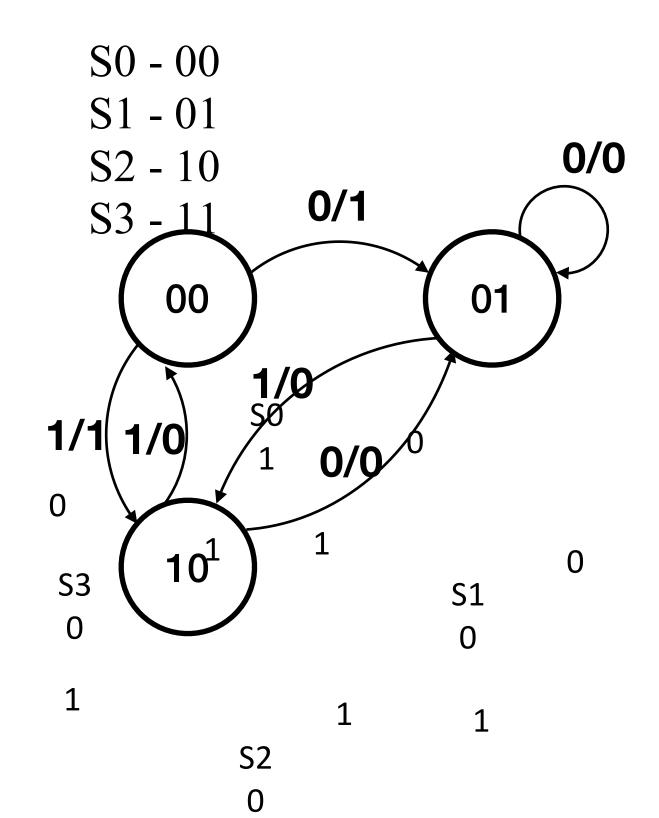

## Clock C Ζ В D S0 - 00 S1 - 01 S2 - 10 **S3 -** 11

# Question $D_A = BY + \overline{A}Y, D_B \subset \overline{V}, Z = \overline{A}\overline{B}$

| Present<br>state |   | Input | Next<br>state |   | Output |

|------------------|---|-------|---------------|---|--------|

| A                | B | Y     | Α             | В | Ζ      |

| 0                | 0 | 0     | 0             | 1 | 1      |

| 0                | 0 | 1     | 1             | 0 | 1      |

| 0                | 1 | 0     | 0             | 1 | 0      |

| 0                | 1 | 1     | 1             | 0 | 0      |

| 1                | 0 | 0     | 0             | 1 | 0      |

| 1                | 0 | 1     | 0             | 0 | 0      |

| 1                | 1 | 0     | 0             | 1 | 0      |

| 1                | 1 | 1     | 1             | 0 | 0      |

Υ

S0 1 0 0 1 1 0 **S**3 S1 0 0 1 1 1 S2 0

Υ

| Pres<br>state |   | Input | Next<br>state |   | Output |

|---------------|---|-------|---------------|---|--------|

| A             | B | Y     | A             | B | Ζ      |

| 0             | 0 | 0     | 0             | 1 | 1      |

| 0             | 0 | 1     | 1             | 0 | 1      |

| 0             | 1 | 0     | 0             | 1 | 0      |

| 0             | 1 | 1     | 1             | 0 | 0      |

| 1             | 0 | 0     | 0             | 1 | 0      |

| 1             | 0 | 1     | 0             | 0 | 0      |

| 1             | 1 | 0     | 0             | 1 | 0      |

| 1             | 1 | 1     | 1             | 0 | 0      |

|               |   |       |               |   |        |

#### Question Clock C Ζ Β D $D_A = BY + \overline{A}Y, D_B \subset \overline{V}, Z = \overline{A}\overline{B}$ S0 - 00 **S1 - 01** S2 - 10 S3 - 11 S0 1 0 0 1 1 **S**3 S1 0 0 1 1 1 S2 0

1/1 cise

Υ

| Pres<br>state |   | Input | Next<br>state |   | Output |

|---------------|---|-------|---------------|---|--------|

| A             | B | Y     | A             | B | Ζ      |

| 0             | 0 | 0     | 0             | 1 | 1      |

| 0             | 0 | 1     | 1             | 0 | 1      |

| 0             | 1 | 0     | 0             | 1 | 0      |

| 0             | 1 | 1     | 1             | 0 | 0      |

| 1             | 0 | 0     | 0             | 1 | 0      |

| 1             | 0 | 1     | 0             | 0 | 0      |

| 1             | 1 | 0     | 0             | 1 | 0      |

| 1             | 1 | 1     | 1             | 0 | 0      |

|               |   |       |               |   |        |

## Question Clock C В D

# $D_A = BY + \overline{A}Y, D_B \subset \overline{V}, Z = \overline{A}\overline{B}$

| Pres<br>state |   | Input | Next<br>state |   | Output |

|---------------|---|-------|---------------|---|--------|

| A             | B | Y     | Α             | B | Ζ      |

| 0             | 0 | 0     | 0             | 1 | 1      |

| 0             | 0 | 1     | 1             | 0 | 1      |

| 0             | 1 | 0     | 0             | 1 | 0      |

| 0             | 1 | 1     | 1             | 0 | 0      |

| 1             | 0 | 0     | 0             | 1 | 0      |

| 1             | 0 | 1     | 0             | 0 | 0      |

| 1             | 1 | 0     | 0             | 1 | 0      |

| 1             | 1 | 1     | 1             | 0 | 0      |

|               |   |       |               |   |        |

Υ

Ζ

## Question Clock C В D

# $D_A = BY + \overline{A}Y, D_B \in \overline{V}, Z = \overline{A}\overline{B}$

| Pres<br>state |   | Input | Next<br>state |   | Output |

|---------------|---|-------|---------------|---|--------|

| A             | B | Y     | Α             | B | Ζ      |

| 0             | 0 | 0     | 0             | 1 | 1      |

| 0             | 0 | 1     | 1             | 0 | 1      |

| 0             | 1 | 0     | 0             | 1 | 0      |

| 0             | 1 | 1     | 1             | 0 | 0      |

| 1             | 0 | 0     | 0             | 1 | 0      |

| 1             | 0 | 1     | 0             | 0 | 0      |

| 1             | 1 | 0     | 0             | 1 | 0      |

| 1             | 1 | 1     | 1             | 0 | 0      |

|               |   |       |               |   |        |

Υ

## Question Clock C В D

# $D_A = BY + \overline{A}Y, D_B \subset \overline{V}, Z = \overline{A}\overline{B}$

| Pres<br>stat |   | Input | Next<br>state |   | Output |

|--------------|---|-------|---------------|---|--------|

| A            | В | Y     | Α             | B | Ζ      |

| 0            | 0 | 0     | 0             | 1 | 1      |

| 0            | 0 | 1     | 1             | 0 | 1      |

| 0            | 1 | 0     | 0             | 1 | 0      |

| 0            | 1 | 1     | 1             | 0 | 0      |

| 1            | 0 | 0     | 0             | 1 | 0      |

| 1            | 0 | 1     | 0             | 0 | 0      |

| 1            | 1 | 0     | 0             | 1 | 0      |

| 1            | 1 | 1     | 1             | 0 | 0      |

|              |   |       |               |   |        |

Υ

## Question Clock C В D

# $D_A = BY + \overline{A}Y, D_B \subset \overline{V}, Z = \overline{A}\overline{B}$

| Pres<br>state | sent<br>e | Input | Next<br>state |   | Output |

|---------------|-----------|-------|---------------|---|--------|

| A             | В         | Y     | Α             | B | Ζ      |

| 0             | 0         | 0     | 0             | 1 | 1      |

| 0             | 0         | 1     | 1             | 0 | 1      |

| 0             | 1         | 0     | 0             | 1 | 0      |

| 0             | 1         | 1     | 1             | 0 | 0      |

| 1             | 0         | 0     | 0             | 1 | 0      |

| 1             | 0         | 1     | 0             | 0 | 0      |

| 1             | 1         | 0     | 0             | 1 | 0      |

| 1             | 1         | 1     | 1             | 0 | 0      |

|               |           |       |               |   |        |

Υ

## Question Clock C В D

# $D_A = BY + \overline{A}Y, D_B \in \overline{V}, Z = \overline{A}\overline{B}$

| Pres<br>state |   | Input | Next<br>state |   | Output |

|---------------|---|-------|---------------|---|--------|

| Α             | В | Y     | Α             | B | Ζ      |

| 0             | 0 | 0     | 0             | 1 | 1      |

| 0             | 0 | 1     | 1             | 0 | 1      |

| 0             | 1 | 0     | 0             | 1 | 0      |

| 0             | 1 | 1     | 1             | 0 | 0      |

| 1             | 0 | 0     | 0             | 1 | 0      |

| 1             | 0 | 1     | 0             | 0 | 0      |

| 1             | 1 | 0     | 0             | 1 | 0      |

| 1             | 1 | 1     | 1             | 0 | 0      |

|               |   |       |               |   |        |

Υ

## Question Clock C В D

# $D_A = BY + \overline{A}Y, D_B \subset \overline{V}, Z = \overline{A}\overline{B}$

| Pres<br>stat | sent<br>e | Input | Next<br>state |   | Output |

|--------------|-----------|-------|---------------|---|--------|

| Α            | В         | Y     | Α             | В | Ζ      |

| 0            | 0         | 0     | 0             | 1 | 1      |

| 0            | 0         | 1     | 1             | 0 | 1      |

| 0            | 1         | 0     | 0             | 1 | 0      |

| 0            | 1         | 1     | 1             | 0 | 0      |

| 1            | 0         | 0     | 0             | 1 | 0      |

| 1            | 0         | 1     | 0             | 0 | 0      |

| 1            | 1         | 0     | 0             | 1 | 0      |

| 1            | 1         | 1     | 1             | 0 | 0      |

|              |           |       |               |   |        |

Υ

## Question Clock C В D

# $D_A = BY + \overline{A}Y, D_B \in \overline{V}, Z = \overline{A}\overline{B}$

| Pres<br>stat | sent<br>e | Input | Next<br>state |   | Output |

|--------------|-----------|-------|---------------|---|--------|

| Α            | В         | Y     | A             | B | Z      |

| 0            | 0         | 0     | 0             | 1 | 1      |

| 0            | 0         | 1     | 1             | 0 | 1      |

| 0            | 1         | 0     | 0             | 1 | 0      |

| 0            | 1         | 1     | 1             | 0 | 0      |

| 1            | 0         | 0     | 0             | 1 | 0      |

| 1            | 0         | 1     | 0             | 0 | 0      |

| 1            | 1         | 0     | 0             | 1 | 0      |

| 1            | 1         | 1     | 1             | 0 | 0      |

|              |           |       |               |   |        |

Υ

## Question Clock C В D

# $D_A = BY + \overline{A}Y, D_B \in \overline{V}, Z = \overline{A}\overline{B}$

| Pres<br>stat | sent<br>e | Input | Next<br>state |   | Output |  |

|--------------|-----------|-------|---------------|---|--------|--|

| A            | B         | Y     | A             | B | Ζ      |  |

| 0            | 0         | 0     | 0             | 1 | 1      |  |

| 0            | 0         | 1     | 1             | 0 | 1      |  |

| 0            | 1         | 0     | 0             | 1 | 0      |  |

| 0            | 1         | 1     | 1             | 0 | 0      |  |

| 1            | 0         | 0     | 0             | 1 | 0      |  |

| 1            | 0         | 1     | 0             | 0 | 0      |  |

| 1            | 1         | 0     | 0             | 1 | 0      |  |

| 1            | 1         | 1     | 1             | 0 | 0      |  |

Υ

S2 0

Ζ

## Question Clock C В D

# $D_A = BY + \overline{A}Y, D_B \in \overline{V}, Z = \overline{A}\overline{B}$

| Present<br>state |   | Input | Next<br>state |   | Output |

|------------------|---|-------|---------------|---|--------|

| A                | B | Y     | A             | B | Ζ      |

| 0                | 0 | 0     | 0             | 1 | 1      |

| 0                | 0 | 1     | 1             | 0 | 1      |

| 0                | 1 | 0     | 0             | 1 | 0      |

| 0                | 1 | 1     | 1             | 0 | 0      |

| 1                | 0 | 0     | 0             | 1 | 0      |

| 1                | 0 | 1     | 0             | 0 | 0      |

| 1                | 1 | 0     | 0             | 1 | 0      |

| 1                | 1 | 1     | 1             | 0 | 0      |

Υ

S2 0

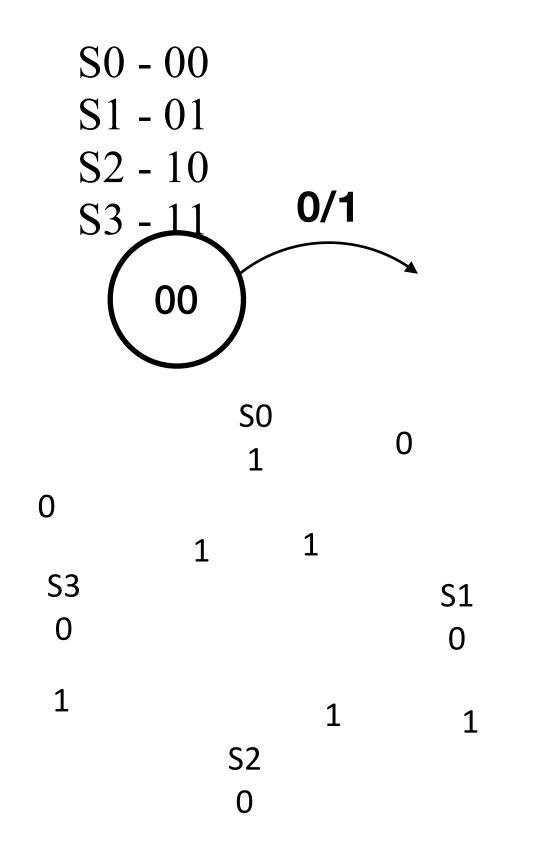

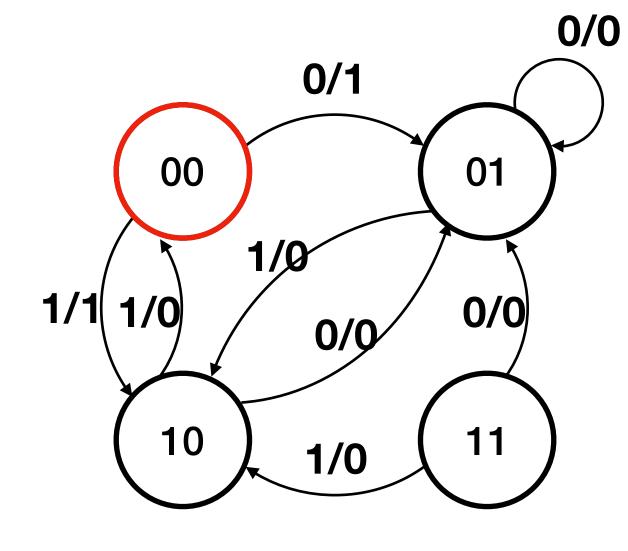

- Initial state 00

- Write down the state transition from input 0101

- 00

- Write down the output

- Initial state 00

- Write down the state transition from input 0101

- 00

- Write down the output

- Initial state 00

- Write down the state transition from input 0101

- 00

- Write down the output

- Initial state 00

- Write down the state transition from input 0101

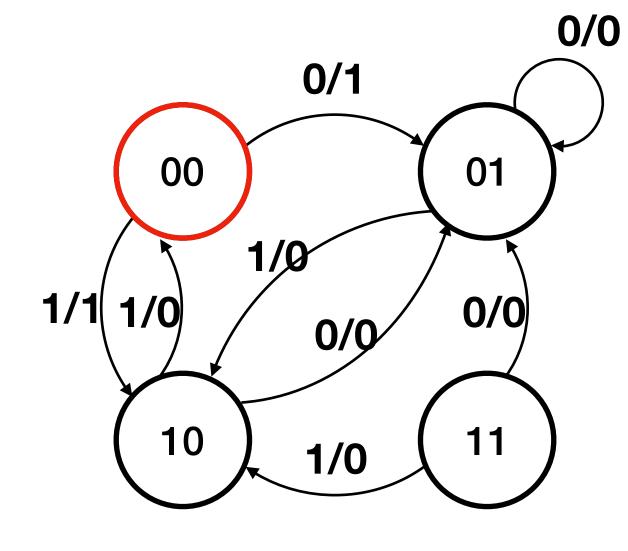

- 00→01

- Write down the output

- Initial state 00

- Write down the state transition from input 0101

- $00 \rightarrow 01 \rightarrow 10$

- Write down the output

- 10

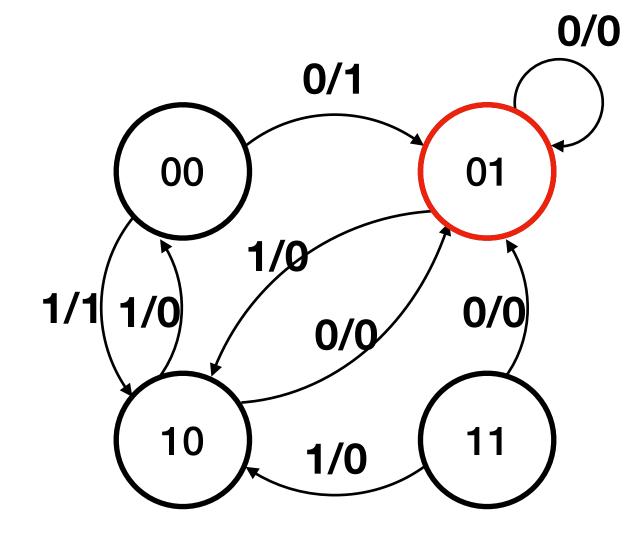

- Initial state 00

- Write down the state transition from input 0101

- $00 \rightarrow 01 \rightarrow 10 \rightarrow 01$

- Write down the output

- 100

- Initial state 00

- Write down the state transition from input 0101

- $00 \rightarrow 01 \rightarrow 10 \rightarrow 01 \rightarrow 10$

- Write down the output

- 1000