Jetic Gū

Columbia College

This assignment is due on 21 March. 2020

Please remember to write your name and student number.

Please submit a single PDF for each assignment. Handwritten submissions and proprietary formats (e.g. Pages or MS Word) will not be accepted. The Lab portion must be submitted separately.

# **Assignment 4 Answer**

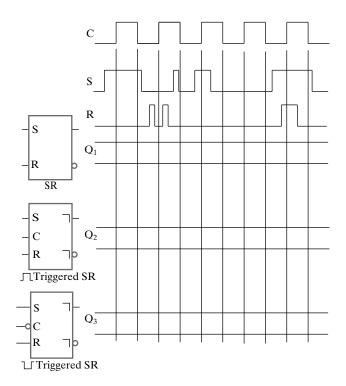

1. Clock, S and R waveforms, one latch and two flip-flops are shown in the following figure. For the latch and the flip-flops, carefully sketch the output waveform,  $Q_i$ , obtained in response to the input waveforms. Assume that the propagation delay of the storage elements is negligible. Initially, all storage elements store 0.

2. A sequential circuit has three D flip-flops A, B, and C, and one input X. The circuit is described by the following input equations:

A. Derive the state table for the circuit.

Seite 1 von 9

| Present State |   |   | Input | Next State |   |   |

|---------------|---|---|-------|------------|---|---|

| A             | В | С | х     | A          | В | С |

| 0             | 0 | 0 | 0     | 1          | 0 | 0 |

| 0             | 0 | 0 | 1     | 0          | 0 | 0 |

| 0             | 0 | 1 | 0     | 0          | 0 | 0 |

| 0             | 0 | 1 | 1     | 1          | 0 | 0 |

| 0             | 1 | 0 | 0     | 0          | 0 | 1 |

| 0             | 1 | 0 | 1     | 1          | 0 | 1 |

| 0             | 1 | 1 | 0     | 1          | 0 | 1 |

| 0             | 1 | 1 | 1     | 0          | 0 | 1 |

| 1             | 0 | 0 | 0     | 1          | 1 | 0 |

| 1             | 0 | 0 | 1     | 0          | 1 | 0 |

| 1             | 0 | 1 | 0     | 0          | 1 | 0 |

| 1             | 0 | 1 | 1     | 1          | 1 | 0 |

| 1             | 1 | 0 | 0     | 0          | 1 | 1 |

B. Draw two state diagrams, one for X=0 and the other for X=1.

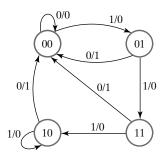

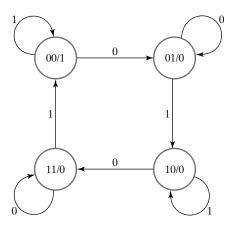

3. Starting from state 00 in the following state diagram, determine the state transitions and output sequence that will be generated when an input sequence of 10011011110 is applied.

$$01/0 -> 00/1 -> 00/0 -> 01/0 -> 11/0 -> 00/1 -> 01/0 -> 11/0 -> 10/0 -> 10/0 -> 00/1$$

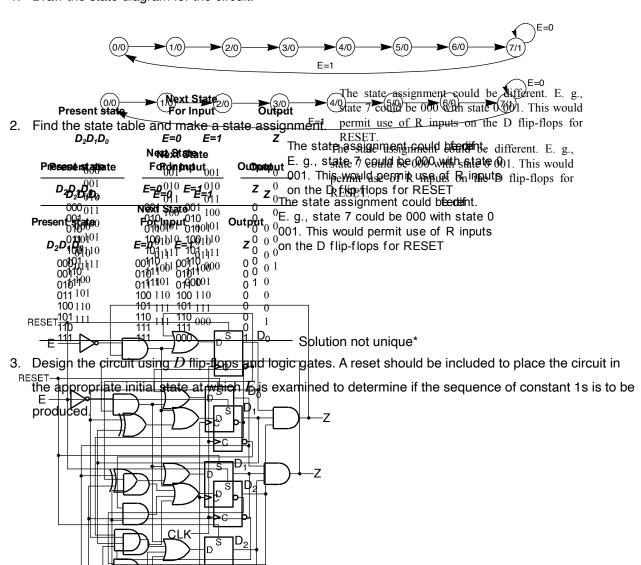

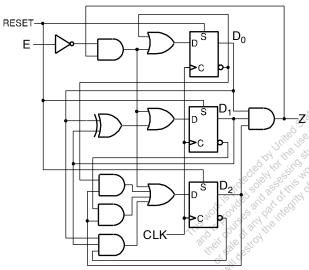

- 4. A Universal Serial Bus (USB) communication link requires a circuit that produces the sequence 00000001. You are to design a synchronous sequential circuit that starts producing this sequence for input E=1. Once the sequence starts, it completes. If E=1, during the last output in the sequence, the sequence repeats. Otherwise, if E=0, the output remains constant at 1.

- 1. Draw the state diagram for the circuit.

Seite 3 von 9

С

CLK

Solution not unique\*

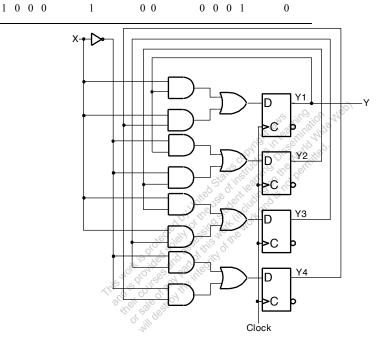

5. A sequential circuit has two flip-flops A and B, one input X, and one output Y. The state diagram is shown in the following figure. Design the circuit with D flip-flops using a 1-hot state assignment.

© 2016 Pearson Education, Inc., Hoboken, NJ. All rights reserved. This material is protected under all copyright laws as they currently exist. No portion of this material may be reproduced, in any form or by any means, without permission in writing from the publisher.

1 1

To use a one-hot assignment, the two flip-flops A and B need to be replaced with four flip-flops Y4, Y3, Y2. Y1.

| Present State |             | Input | Nex   | Output      |   |

|---------------|-------------|-------|-------|-------------|---|

| A B           | Y4 Y3 Y2 Y1 | X     | A' B" | Y4'Y3'Y2'Y1 | Z |

| 0 0           | 0 0 0 1     | 0     | 0 1   | 0 0 1 0     | 1 |

| 0 0           | 0 0 0 1     | 1     | 0 0   | 0 0 0 1     | 1 |

| 0 1           | 0 0 1 0     | 0     | 0 1   | 0 0 1 0     | 0 |

| 0 1           | 0 0 1 0     | 1     | 1 0   | 0 1 0 0     | 0 |

| 1 0           | 0 1 0 0     | 0     | 1 1   | 1 0 0 0     | 0 |

| 1 0           | 0 1 0 0     | 1     | 1 0   | 0 1 0 0     | 0 |

| 1 1           | 1 0 0 0     | 0     | 1 1   | 1 0 0 0     | 0 |

No Reset State Specified.

$\begin{aligned} &D1 = Y1' = X \cdot Y1 + X \cdot Y4 \\ &D2 = Y2' = \overline{X} \cdot Y1 + \overline{X} \cdot Y2 \\ &D3 = Y3' = X \cdot Y2 + X \cdot Y3 \\ &D4 = Y4' = \overline{X} \cdot Y3 + \overline{X} \cdot Y4 \end{aligned}$

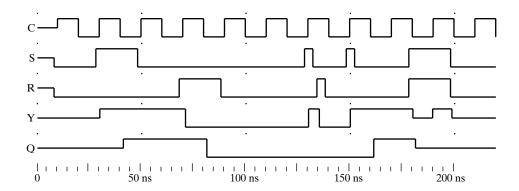

6. The following figure is the logic simulation of an SR Master–Slave flip-flop. Obtain a similar timing diagram for a positive-edge-triggered JK flip-flop during four clock pulses. Show the timing signals for C, J, K, Y, and Q. Assume that initially the output Q is equal to 1, with J=0 and K=1 for the first pulse. Then, for successive pulses, J goes to 1, followed by K going to 0 and then J going back to 0. Assume that each input changes near the negative edge of the pulse.

. . . . . .

## Lab 3

You must complete the following assignment and submit a <u>PDF of instructions</u> enough to replicate your results, and required documentation. You will also need to upload <u>LogicWork circuit design files</u> as specified, and <u>your own library file</u>. Then upload a <u>single ZIP file</u> to student portal. If you don't have the software, draw the circuit design only and include it in the PDF.

- 1. Save the library and circuit files we created in class containing the following designs in the final ZIP file:

- (1) D latch (circuit1-1.cct);

- (2) D flip-flop (circuit1-2.cct);

- (3) Implement  $D_A = \overline{X}A + XY$ ,  $D_B = \overline{X}B + XA$ , Z = XB (circuit1-3.cct);

- (4) Draw the state table and diagram for (3).

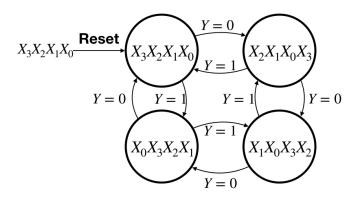

- 2. Draw the state diagram of rotator, write down the equations for each D flip-flop, and complete the implementation (circuit2.cct).

**Start state**  $X_3X_2X_1X_0$ : original 4-bit, implement using binary switches

Input Y

- 0: for left rotation (output  $X_2X_1X_0X_3$ );

- 1: for right rotation (output  $X_0X_3X_2X_1$ );

#### **Behaviour**

Every CLK triggers a shift

## **State Diagram:**

#### **State Assignment and Equations:**

Flip-flops A, B, C, D, initially  $ABCD = X_3X_2X_1X_0$

If

$$Y = 0$$

, at each time:  $D_A = B$ ,  $D_B = C$ ,  $D_C = D$ ,  $D_D = A$

If

$$Y = 1$$

, at each time:  $D_A = D$ ,  $D_B = A$ ,  $D_C = B$ ,  $D_D = C$

Basically, Y is used as switch between 2 options for each D flip-flops. This can be solved using a 2-to-1 multiplexer for each flip-flop.

$$D_A = (\overline{Y} \cdot B) + (Y \cdot D)$$

$$D_B = (\overline{Y} \cdot C) + (Y \cdot A)$$

$$D_C = (\overline{Y} \cdot D) + (Y \cdot B)$$

$$D_D = (\overline{Y} \cdot A) + (Y \cdot C)$$

### Circuit:

... I think at this point it should be simple enough.

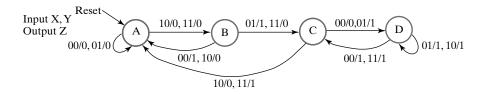

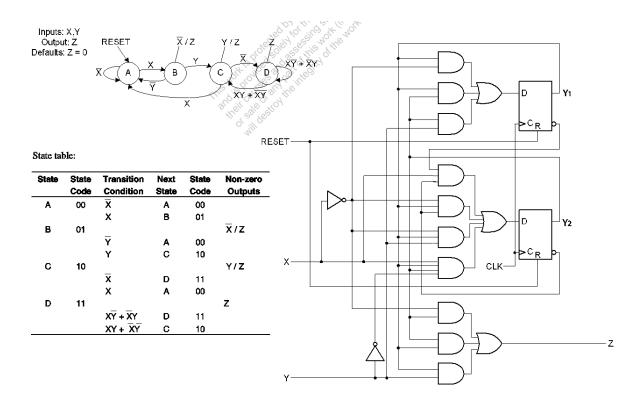

3. Find a state-machine diagram that is equivalent to the following state diagram. Reduce the complexity of the transition conditions as much as possible. Attempt to make outputs unconditional by changing Mealy outputs to Moore outputs. Make a state assignment to your state-machine diagram and find an implementation for the corresponding sequential circuit using D flop-flops, AND gates, OR gates, and inverters.

- (1) Draw the state-machine diagram.

- (2) Write down the Flip-Flop Input Equations and Output Equations.

- (3) Implement the circuit, save as circuit3.cct.

© 2016 Pearson Education, Inc., Hoboken, NJ. All rights reserved. This material is protected under all copyright laws as they currently exist. No portion of this material may be reproduced, in any form or by any means, without permission in writing from the publisher.