# CSCI 150 Introduction to Digital and Computer System Design Lecture 3: Combinational Logic Design VI

Jetic Gū 2020 Winter Semester (S1)

### Overview

- Focus: Arithmetic Functional Blocks

- Architecture: Combinatory Logical Circuits

- Textbook v4: Ch4 4.3, 4.7; v5: Ch2 2.9, Ch3 3.10

- Core Ideas:

- 1. Subtraction I

- 2. VHDL

### Review

Unsigned Binary Adder

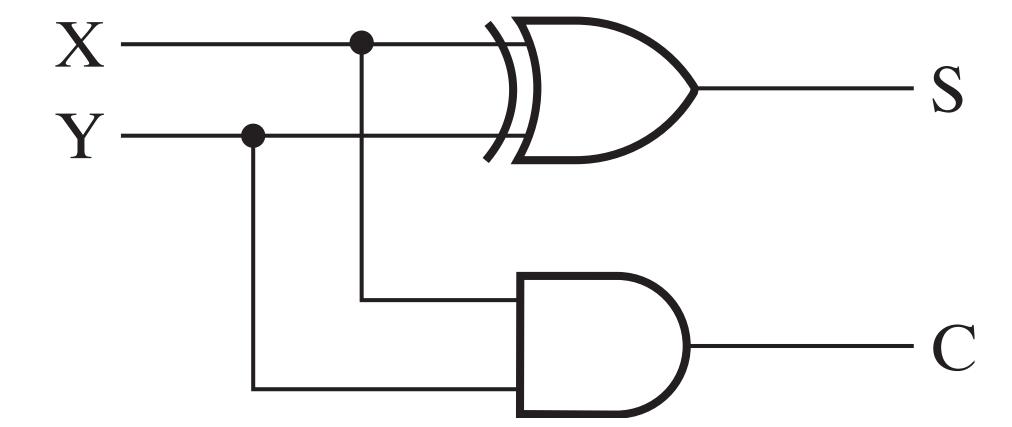

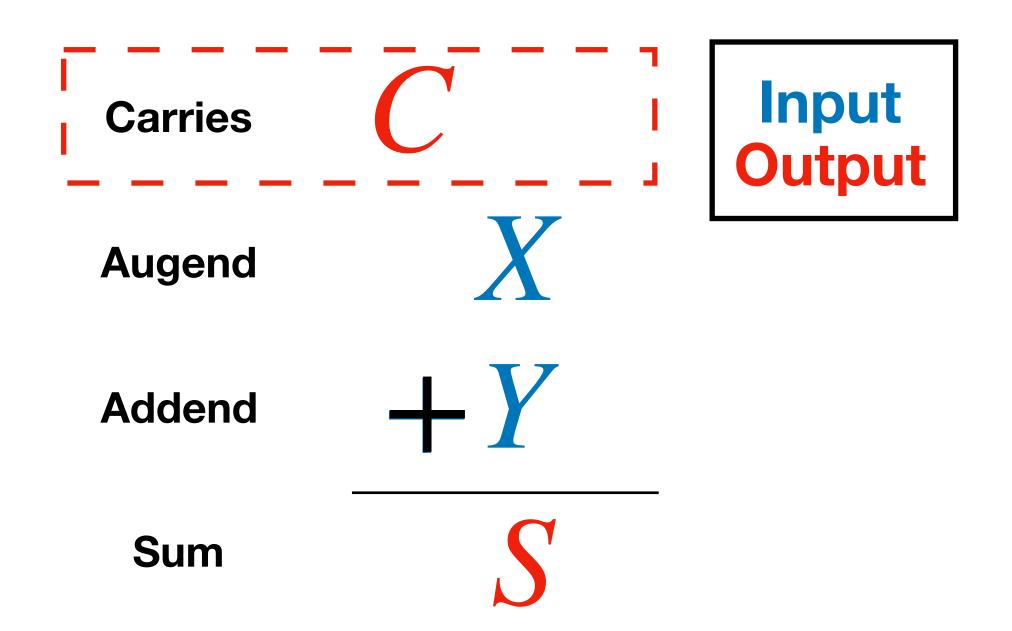

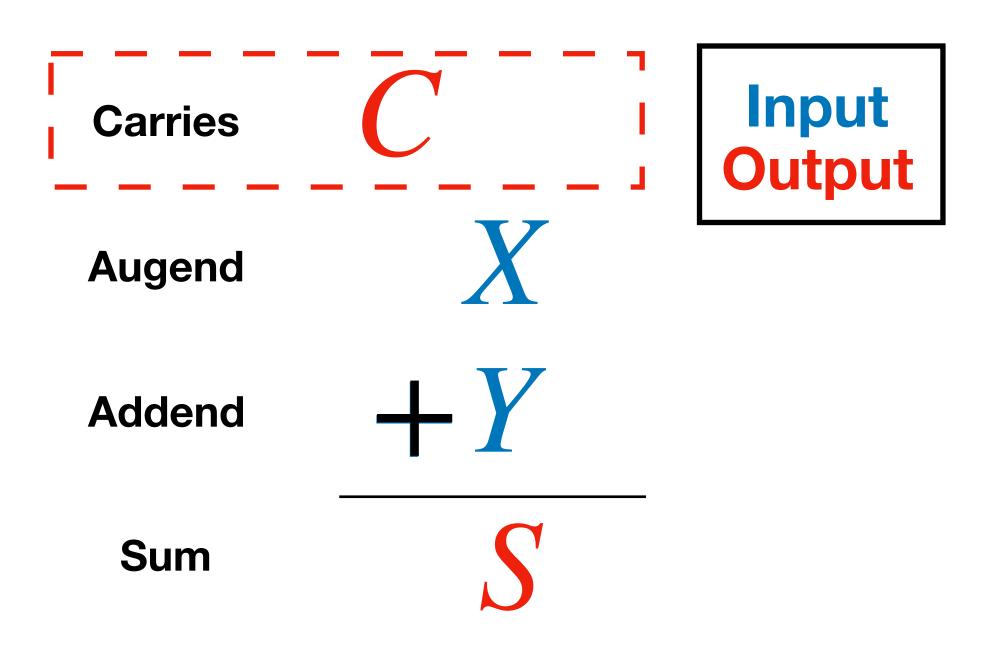

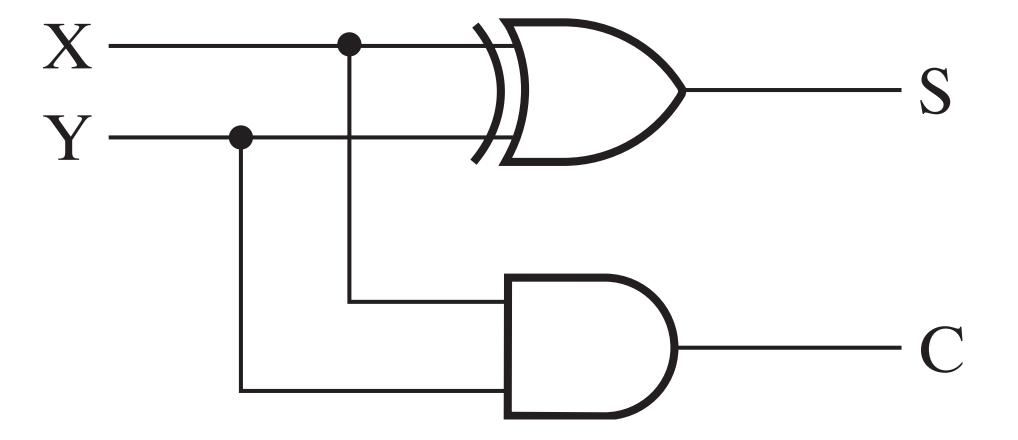

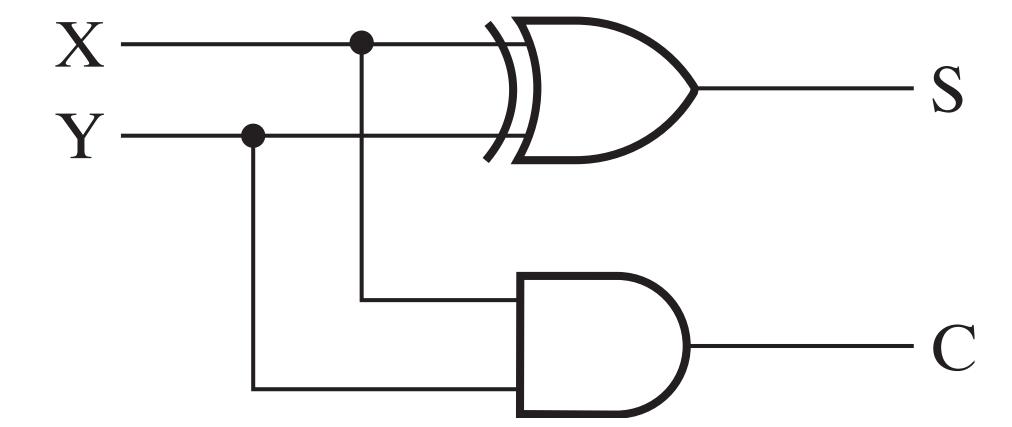

### 1-bit Half Adder

• Half adder input X, Y output S, C

Solie, Market States

### 1-bit Half Adder

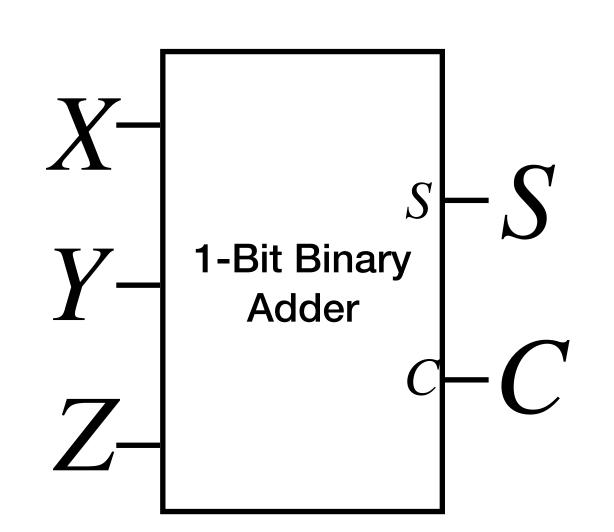

### 1-bit Full Adder

Full adder

input X, Y, Z;

output S, C

### 1-bit Full Adder

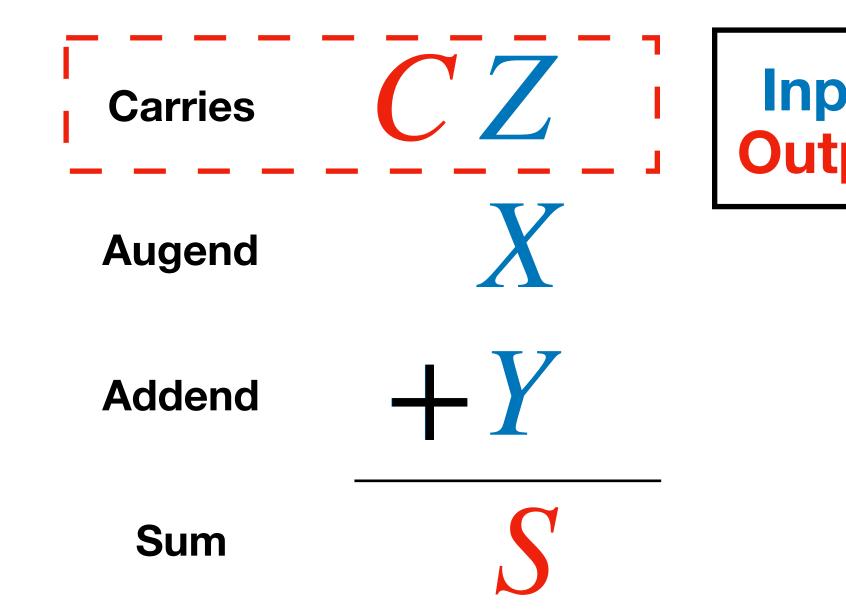

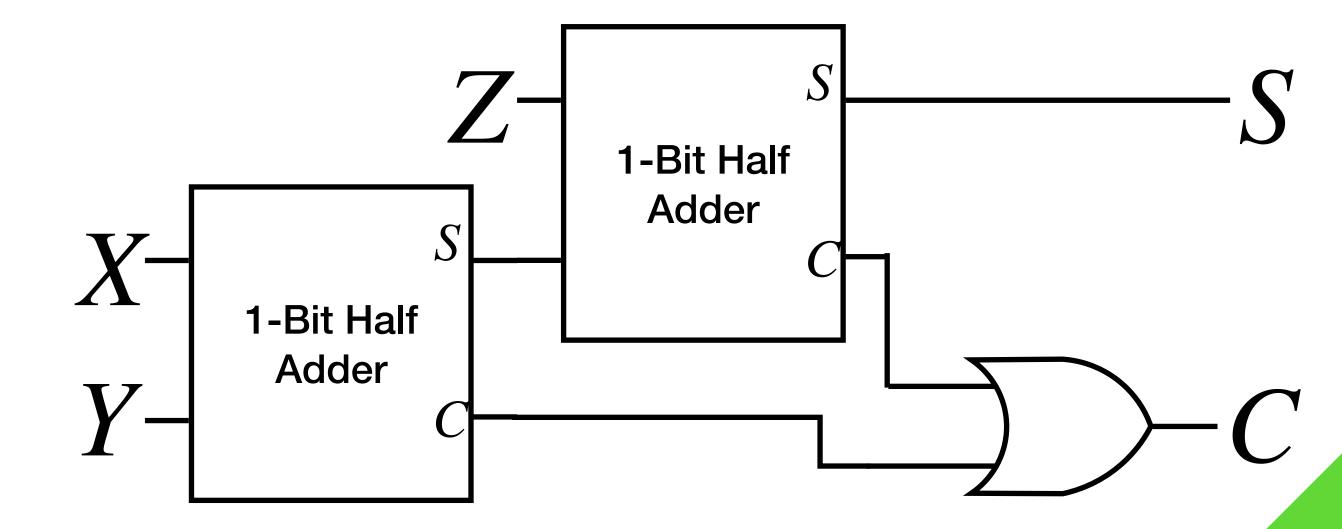

Full adder

input X, Y, Z;

output S, C

• Half adder1 input X, Y output S', C'

• Half adder2 input S', Z output S, C''

$$C = C' + C''$$

o Silon

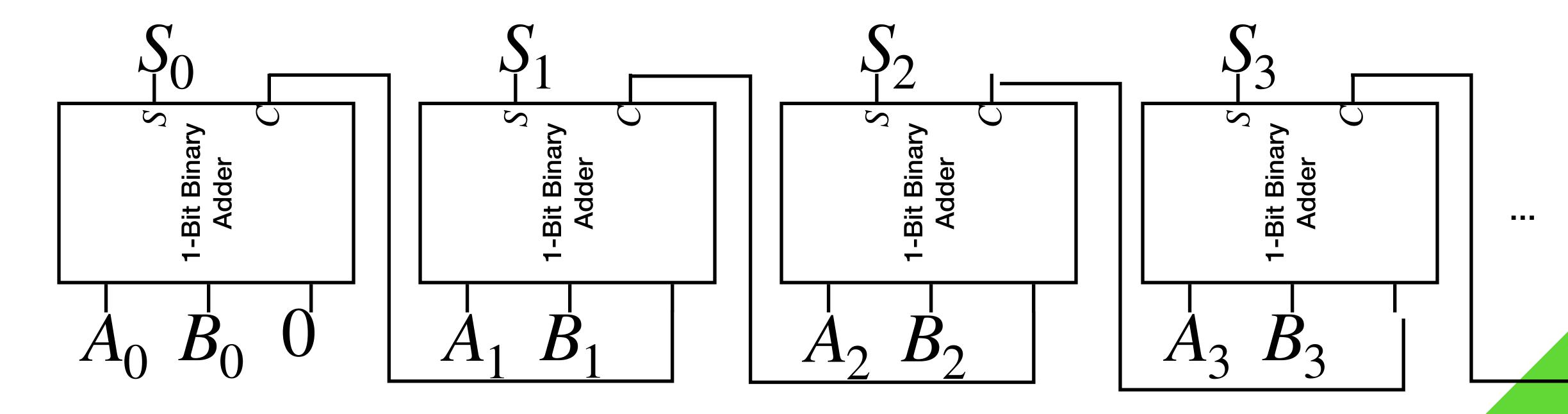

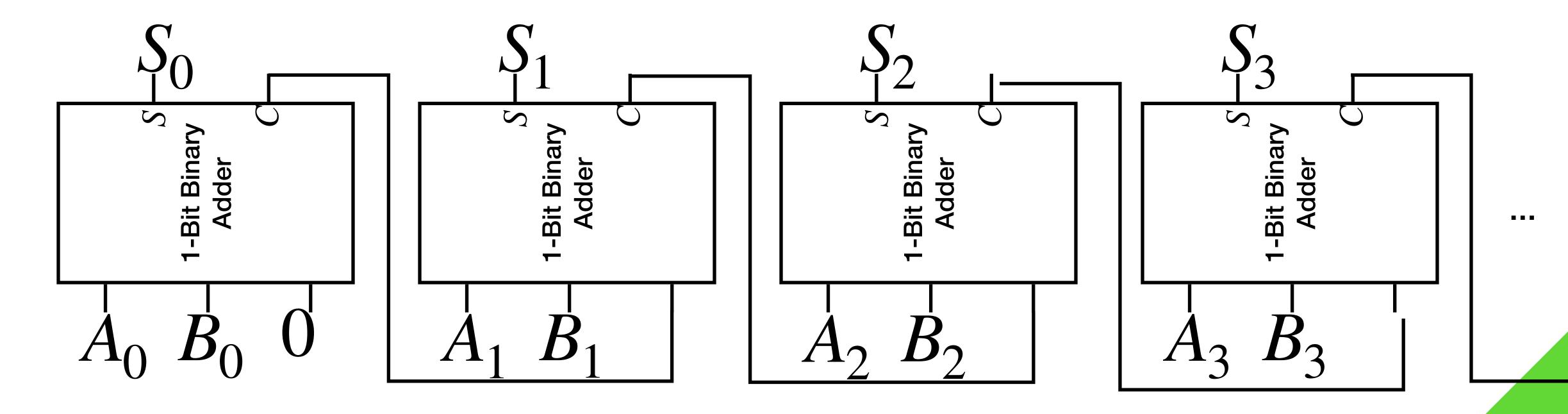

### n-bit Full Adder

O Silon

### n-bit Full Adder

Ripple Carry Adder

OSIION

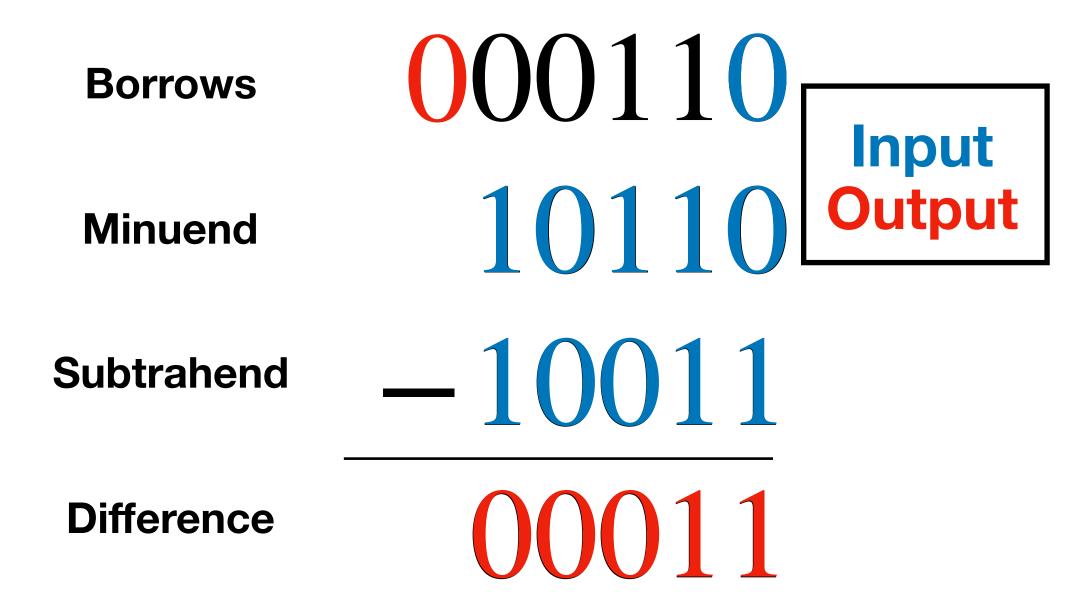

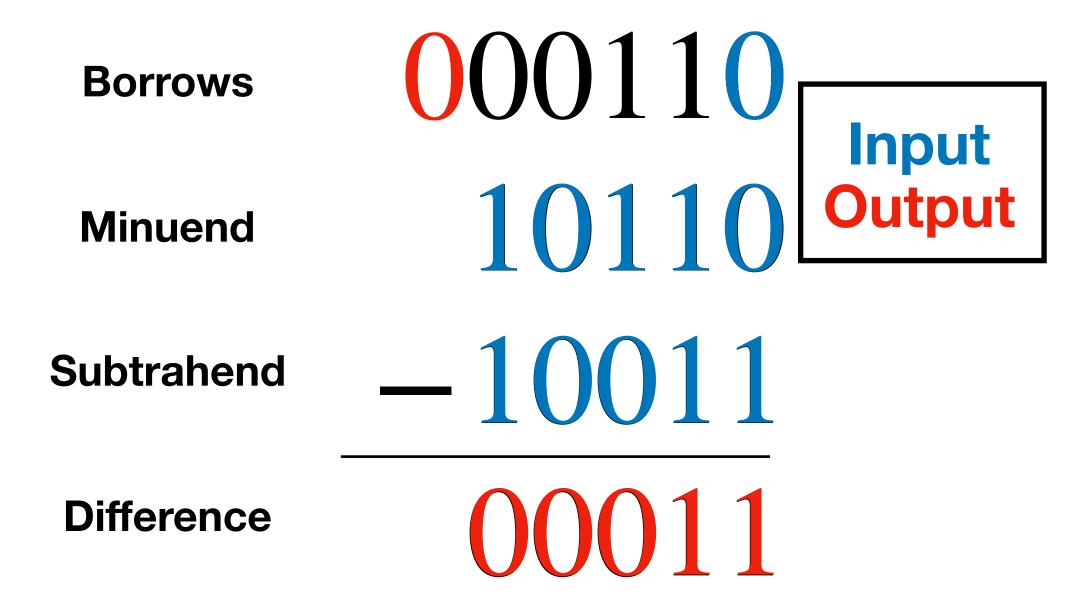

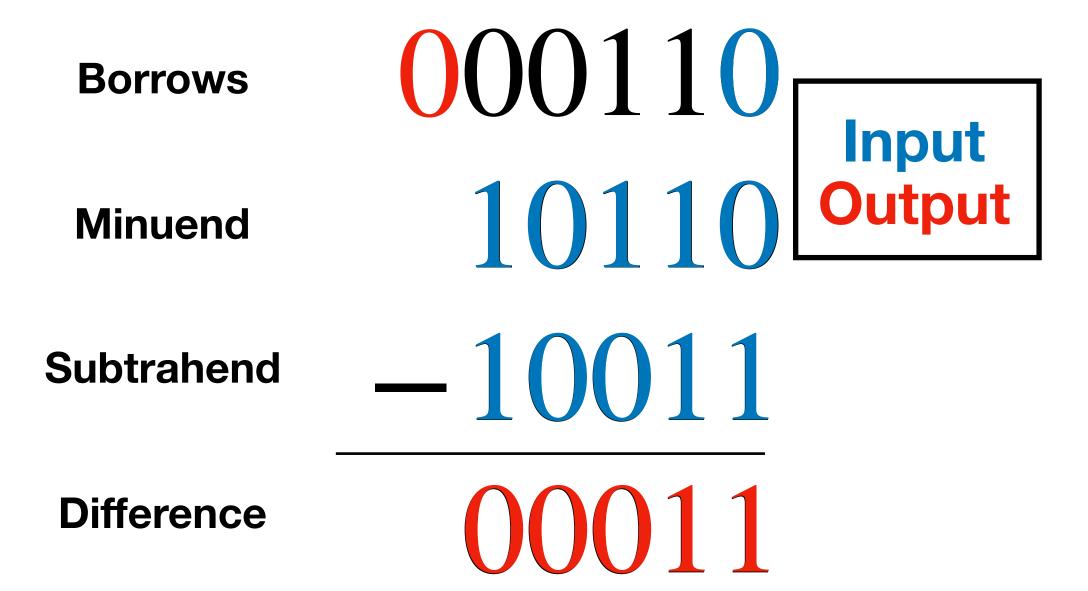

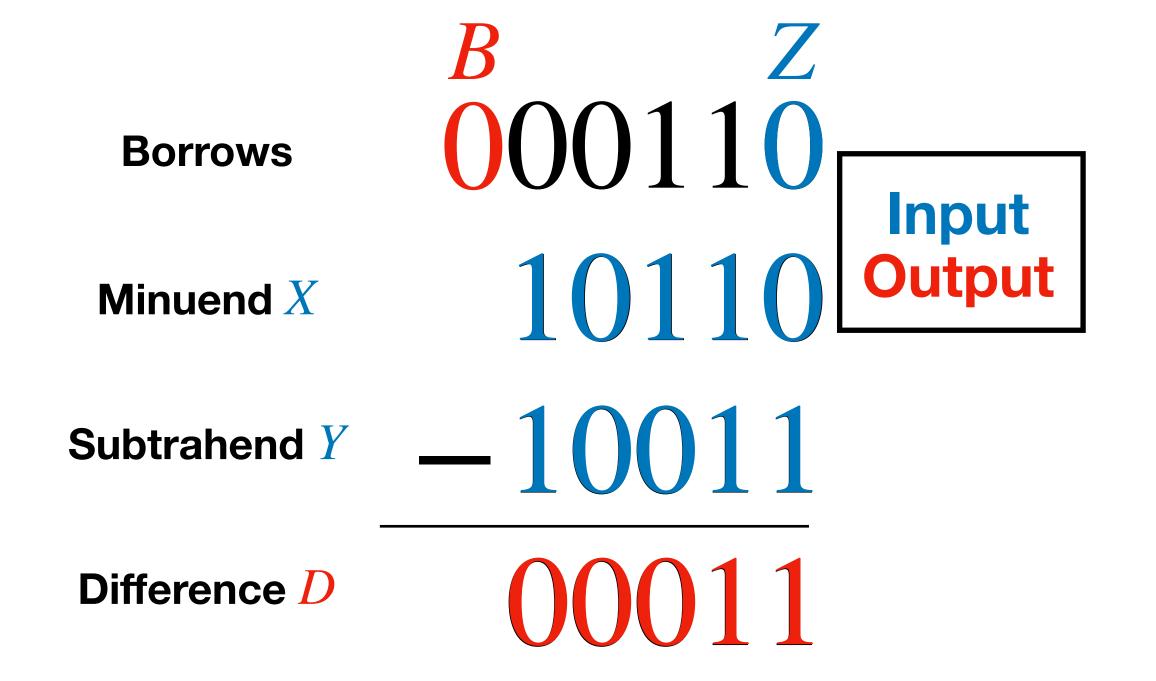

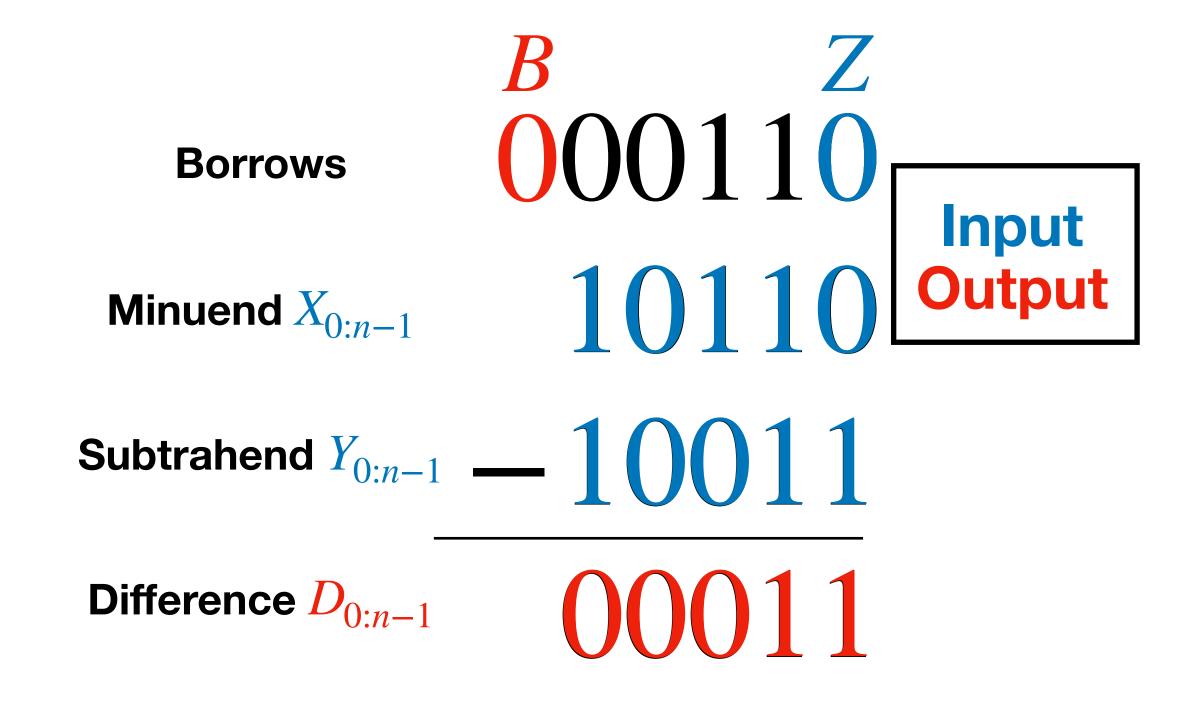

Input: Minuend and Subtrahend Previous borrow

Output: Last borrow, difference

**Borrows**

Minuend

10110

**Subtrahend**

Difference

Input: Minuend and Subtrahend Previous borrow

Output: Last borrow, difference

**Borrows** 10110 Minuend **Subtrahend**

Difference

Input: Minuend and Subtrahend Previous borrow

| Borrows    | 10             |

|------------|----------------|

| Minuend    | 10110          |

| Subtrahend | <b>—</b> 10011 |

| Difference | 1              |

Input: Minuend and Subtrahend Previous borrow

| Borrows    | 110            |

|------------|----------------|

| Minuend    | 10110          |

| Subtrahend | <b>—</b> 10011 |

| Difference | 11             |

### Unsigned Binary Subtraction Subtraction

Input: Minuend and Subtrahend Previous borrow

| Borrows    | 0110           |

|------------|----------------|

| Minuend    | 10110          |

| Subtrahend | <b>-</b> 10011 |

| Difference | 011            |

Input: Minuend and Subtrahend Previous borrow

| Borrows    | 00110          |

|------------|----------------|

| Minuend    | 10110          |

| Subtrahend | <b>—</b> 10011 |

| Difference | 0011           |

Input: Minuend and Subtrahend Previous borrow

| Borrows    | 000110         |

|------------|----------------|

| Minuend    | 10110          |

| Subtrahend | <b>—</b> 10011 |

| Difference | 00011          |

Input: Minuend and Subtrahend Previous borrow

Input: Minuend and Subtrahend Previous borrow

Output: Last borrow, difference

This method works when the Minuend is greater than the Subtrahend!

### Unsigned Binary Subtraction Subtraction Output Description Output Description Description

$$X > Y, F = X - Y$$

We learned to perform subtraction, by subtracting the smaller number from the greater number

Input: Minuend and Subtrahend Previous borrow

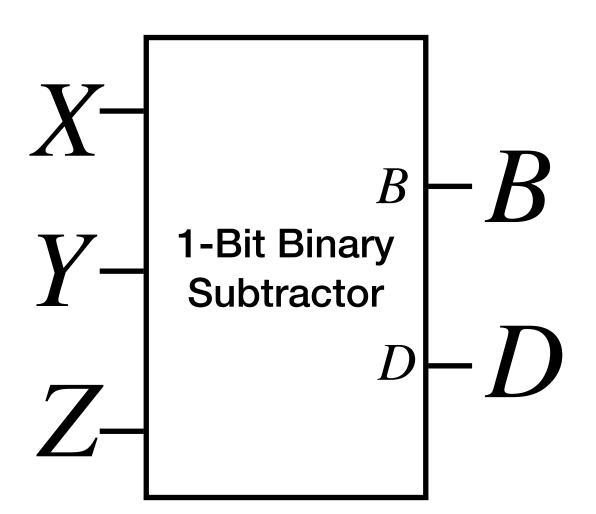

## Unsigned 1-bit Binary Subtraction

**Borrows**

B Z

1 0

Minuend X

• Input: Minuend X and Subtrahend YPrevious borrow Z

Subtrahend Y

\_1

• Output: Last borrow B, difference D

Difference D

Input Output

Court

P1 Subtraction

## Unsigned 1-bit Binary Subtraction

- Input: Minuend X and Subtrahend YPrevious borrow Z

- Output: Last borrow B, difference D

|                     | BZ |                               |

|---------------------|----|-------------------------------|

| Borrows             | 10 | Innut                         |

| Minuend X           |    | <b>Input</b><br><b>Output</b> |

| Subtrahend <i>Y</i> | 1  |                               |

| Difference D        | 1  |                               |

| X | Y | Z | В | D |

|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 | 1 |

| 0 | 1 | 0 | 1 | 1 |

| 0 | 1 | 1 | 1 | 0 |

| 1 | 0 | 0 | 0 | 1 |

| 1 | 0 | 1 | 0 | 0 |

| 1 | 1 | 0 | 0 | 0 |

| 1 | 1 | 1 | 1 | 1 |

## Unsigned 1-bit Binary Subtraction

- Implementation using 3-to-8 Decoder

- $B = \sum m(1,2,3,7)$

- $D = \sum m(1,2,4,7)$

P1 Subtraction

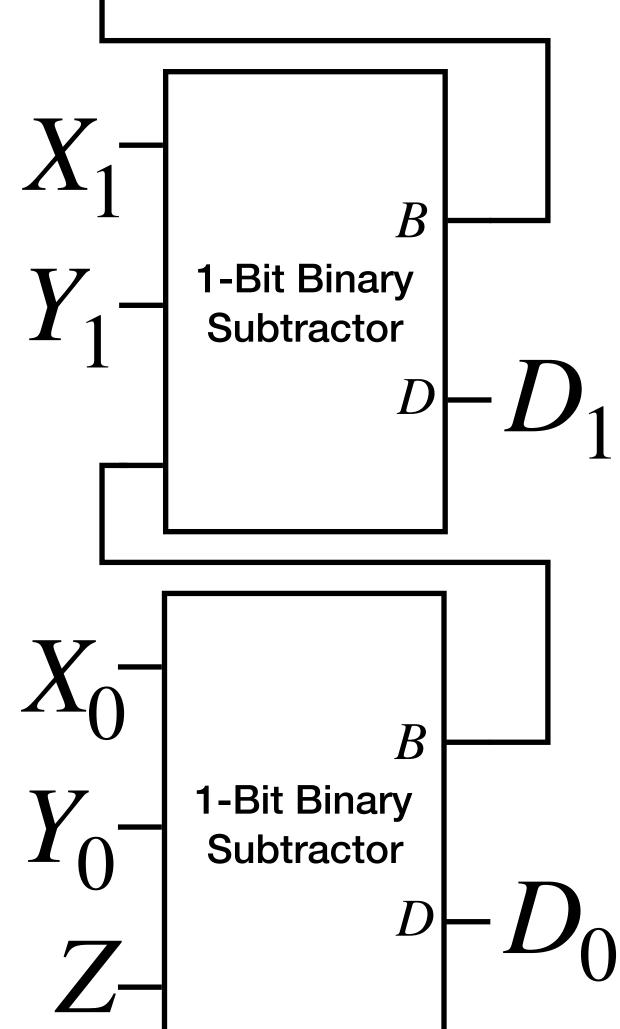

## Unsigned Binary Subtraction

Technology

• 1 bit Unsigned Subtractor

- Input: Minuend and Subtrahend Previous borrow

- Output: Last borrow, difference

Color

Technology

• 1 bit Unsigned Subtractor

**P1**

Subtraction

Color

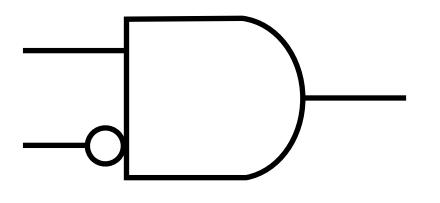

### Hardware Description Language

VHDL (VHSIC-HDL): Very High Speed Integrated Circuit Hardware Description Language

### What is HDL

- Designing complex circuits using logic circuit diagrams is inefficient

- Hardware Description Language

- Like programming language, describes hardware structures and behaviours

- More efficient

- Common languages

- Verilog

- VHDL

Concept.

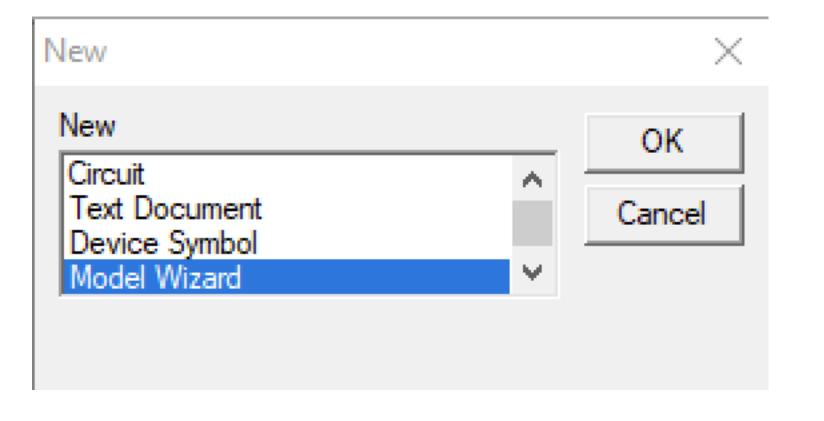

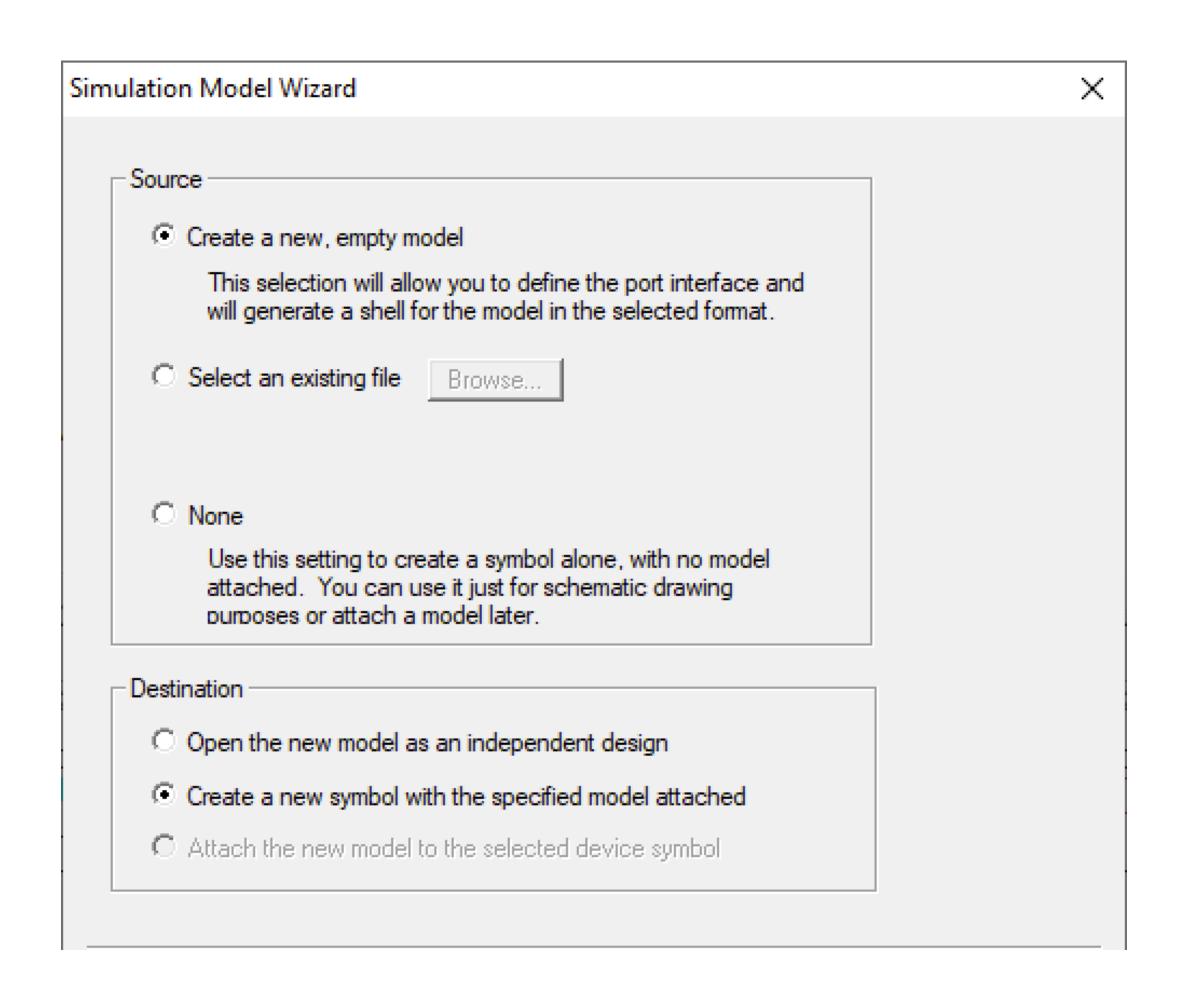

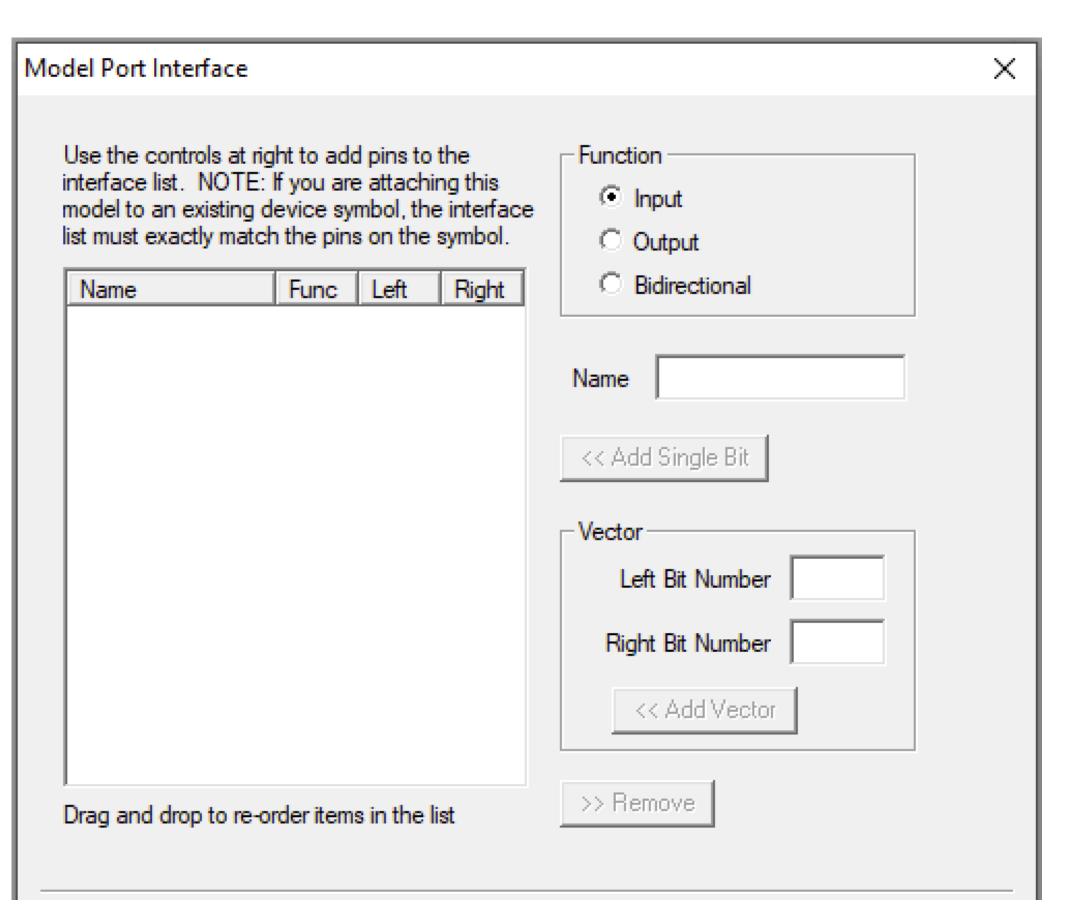

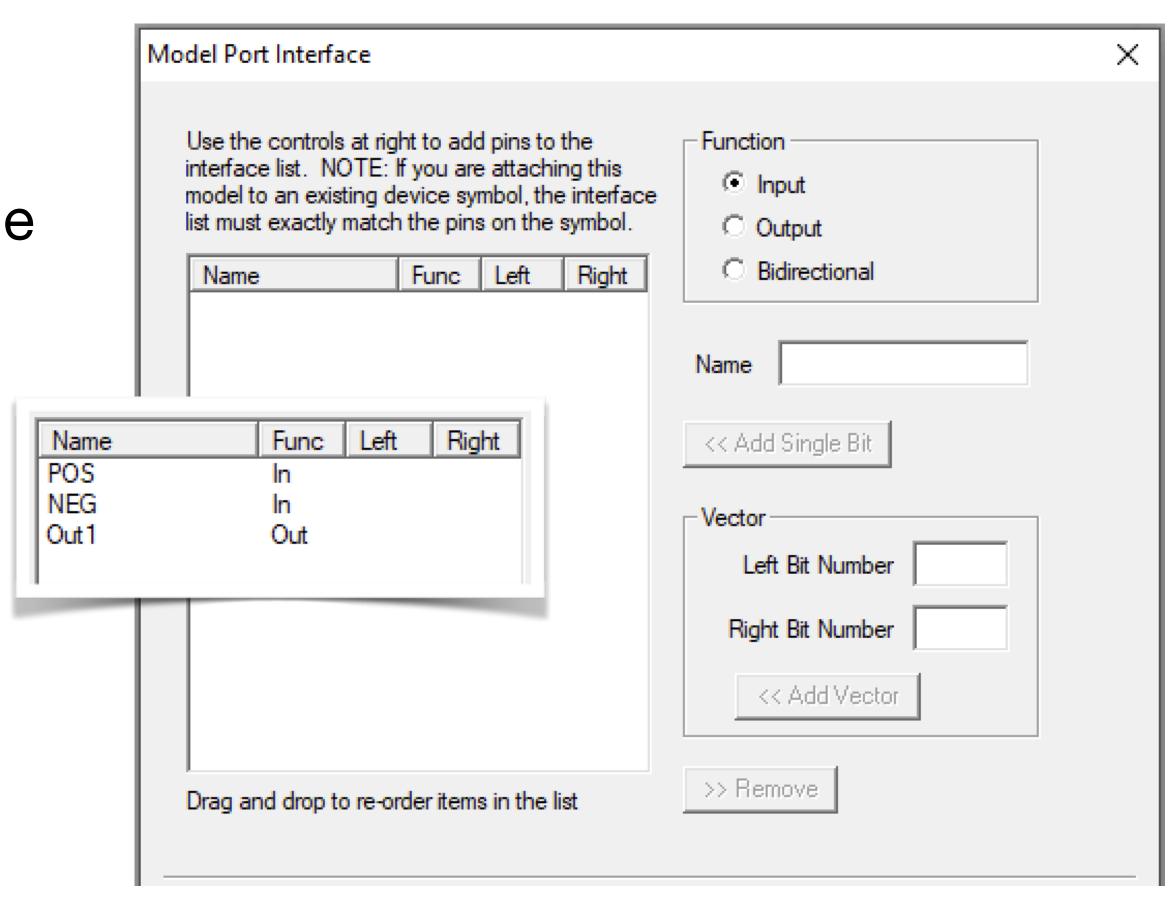

| Model Info                                              |                                                                                        | × |

|---------------------------------------------------------|----------------------------------------------------------------------------------------|---|

| Select the desired model type  Structural Circuit  VHDL | Create a VHDL language file which can be used to describe the function of this device. |   |

| Enter a name for the new model                          | AND1INV                                                                                |   |

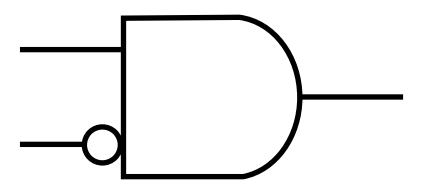

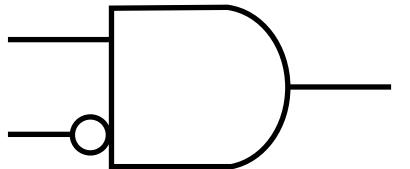

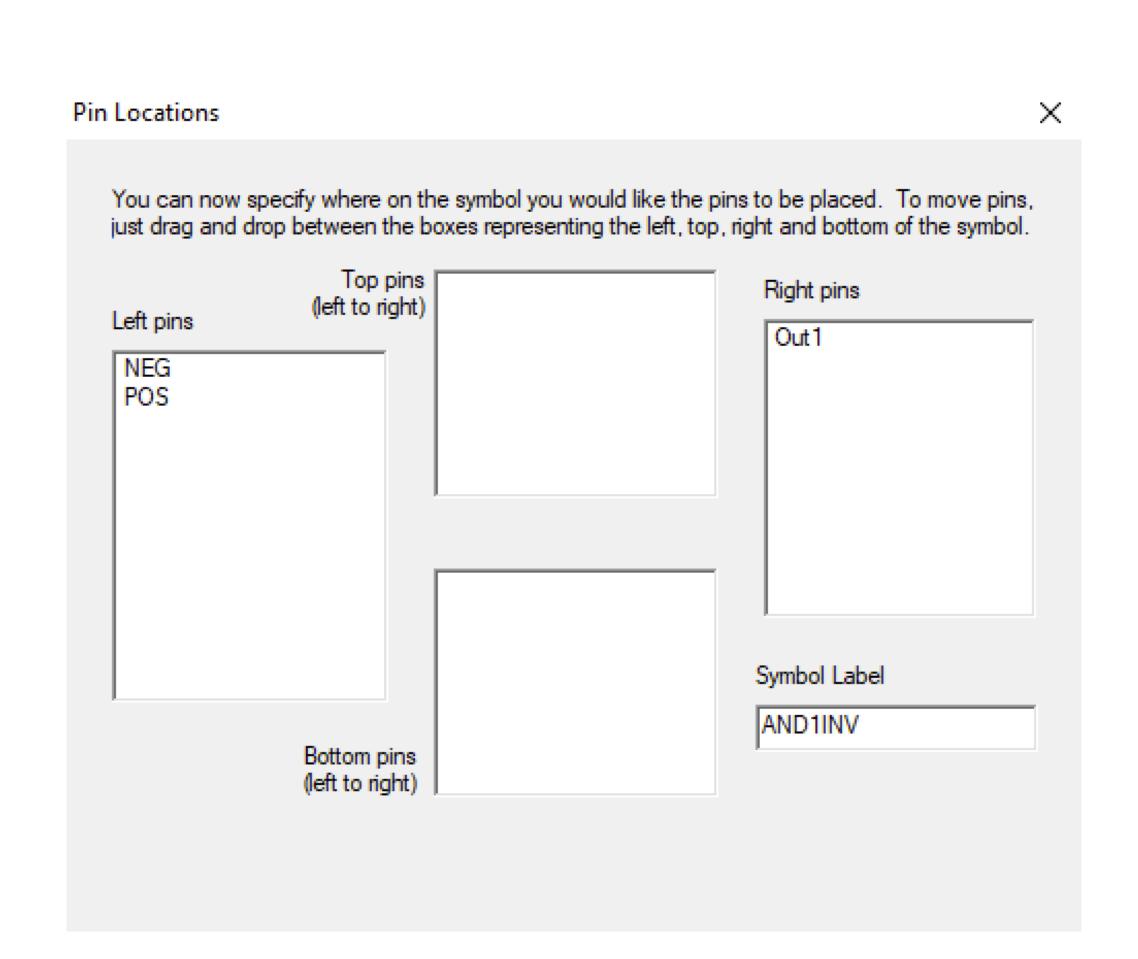

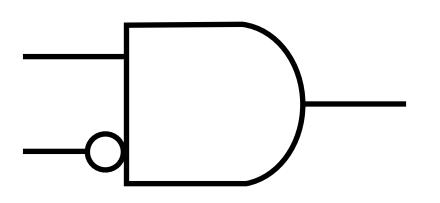

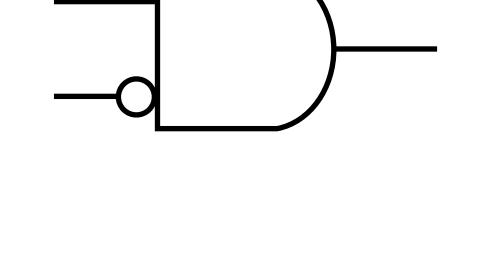

This is where you define all inputs and outputs

Input: POS

Input: NEG

Output: Out1

This is where you define all inputs and outputs

Input: POS

Input: NEG

Output: Out1

4. The programme will ask you for Pin Location assignment. Just click Next.

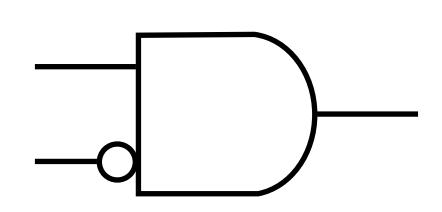

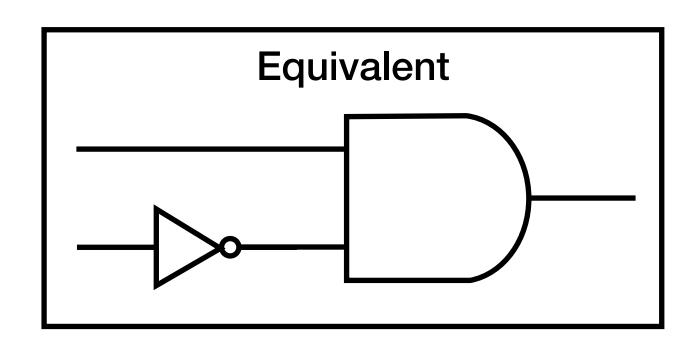

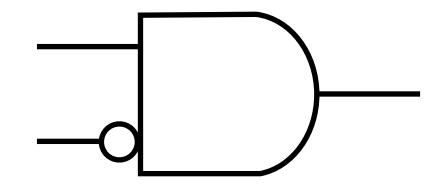

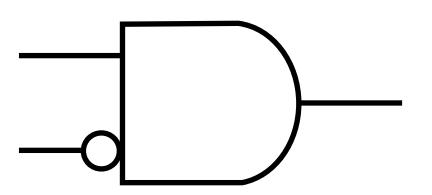

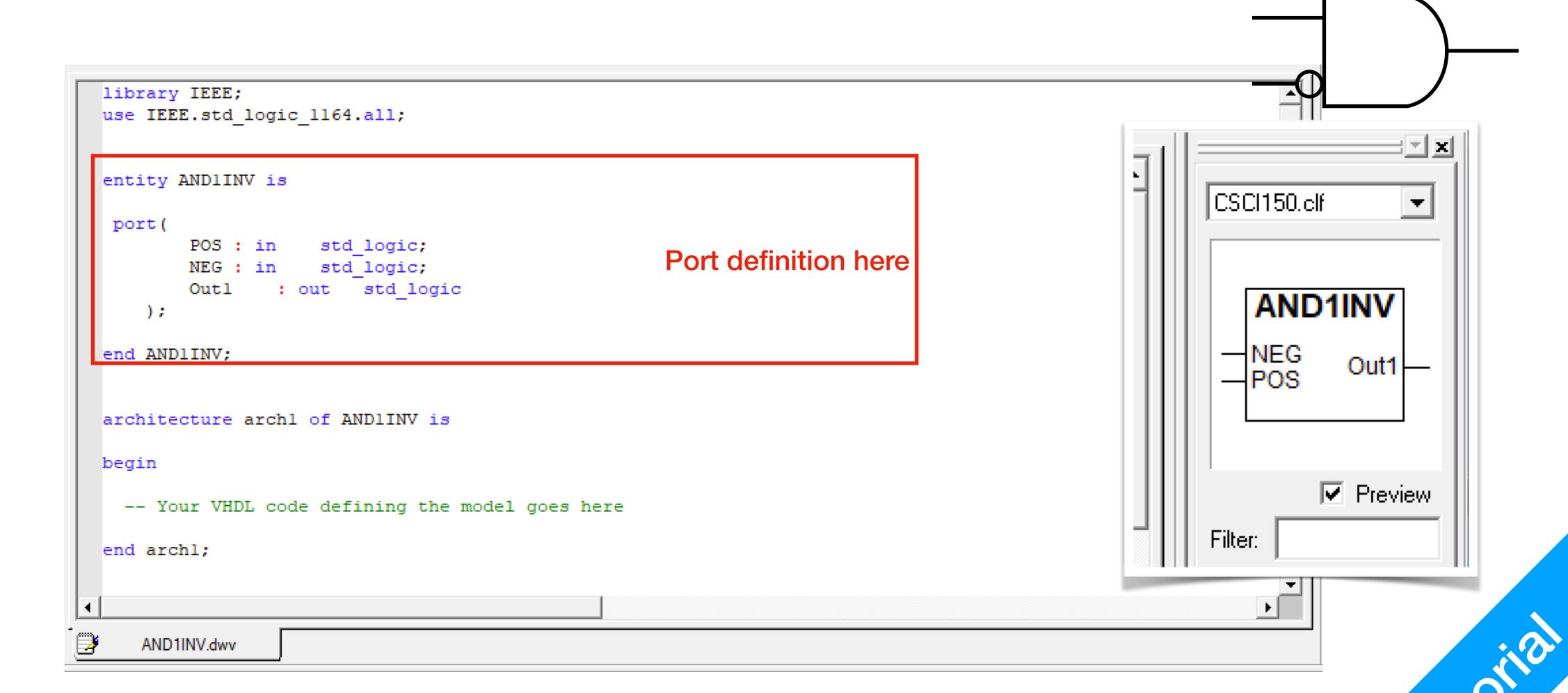

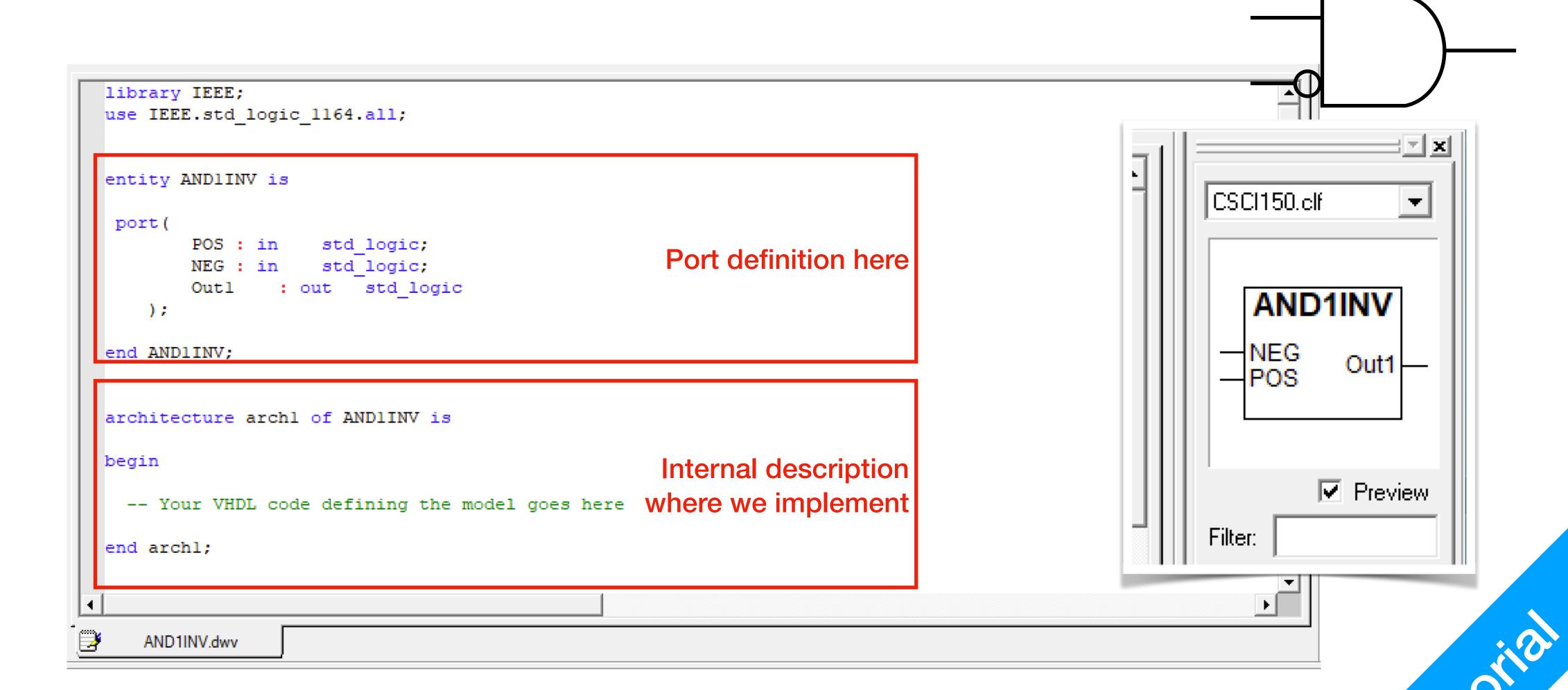

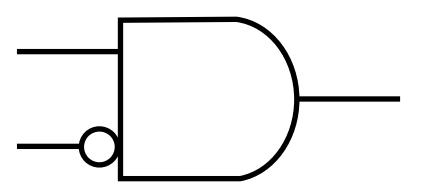

```

library IEEE;

use IEEE.std_logic_l164.all;

entity ANDLINV is

CSCI150.clf

port (

POS : in std_logic;

NEG: in std logic;

Outl : out std logic

AND1INV

);

⊢NEG

end ANDlINV;

Out1

architecture archl of ANDLINV is

begin

✓ Preview

-- Your VHDL code defining the model goes here

Filter:

end archl;

AND1INV.dwv

```

```

library IEEE;

use IEEE.std_logic_l164.all;

entity ANDIINV is

port (

std logic;

std logic;

NEG : in

: out std logic

);

end AND1INV;

architecture archl of ANDLINV is

begin

OUT1 <= POS AND NOT NEG AFTER 1NS;

end archl;

AND1INV.dwv

```

```

library IEEE;

use IEEE.std_logic_l164.all;

entity ANDLINV is

port (

std logic;

NEG : in

std logic;

: out std logic

);

end ANDLINV;

architecture archl of ANDLINV is

begin

OUT1 <= POS AND NOT NEG AFTER 1NS;

end archl;

AND1INV.dwv

```

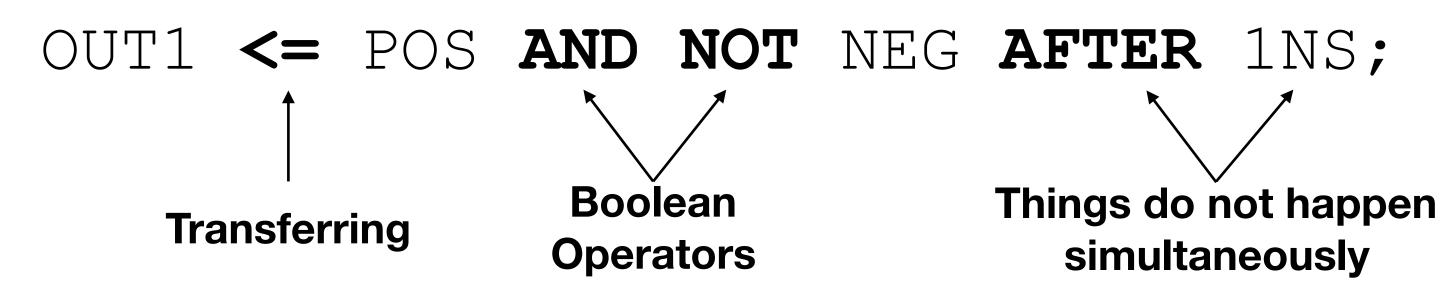

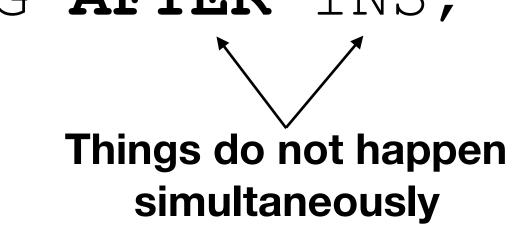

```

OUT1 <= POS AND NOT NEG AFTER 1NS;

Things do not happen

Boolean

Transferring

simultaneously

Operators

```

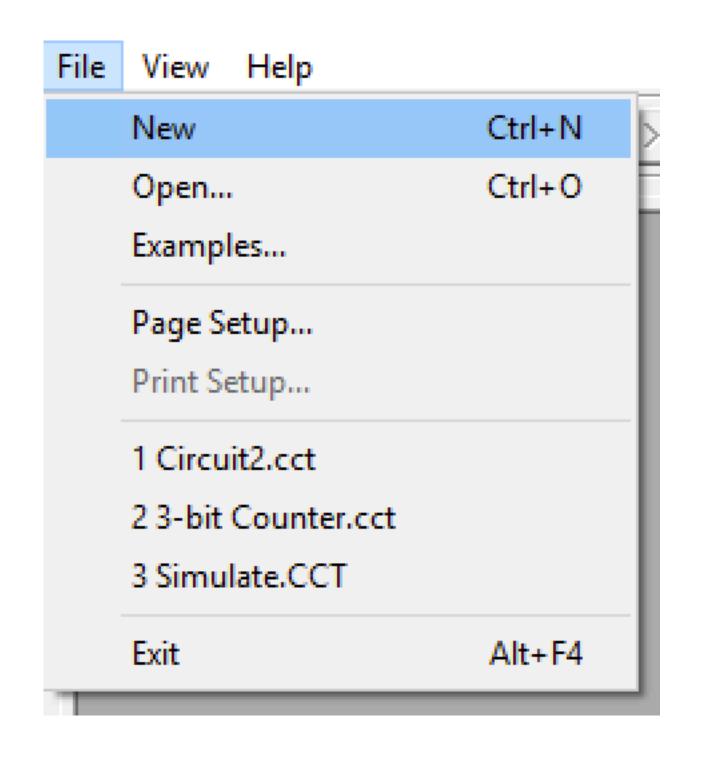

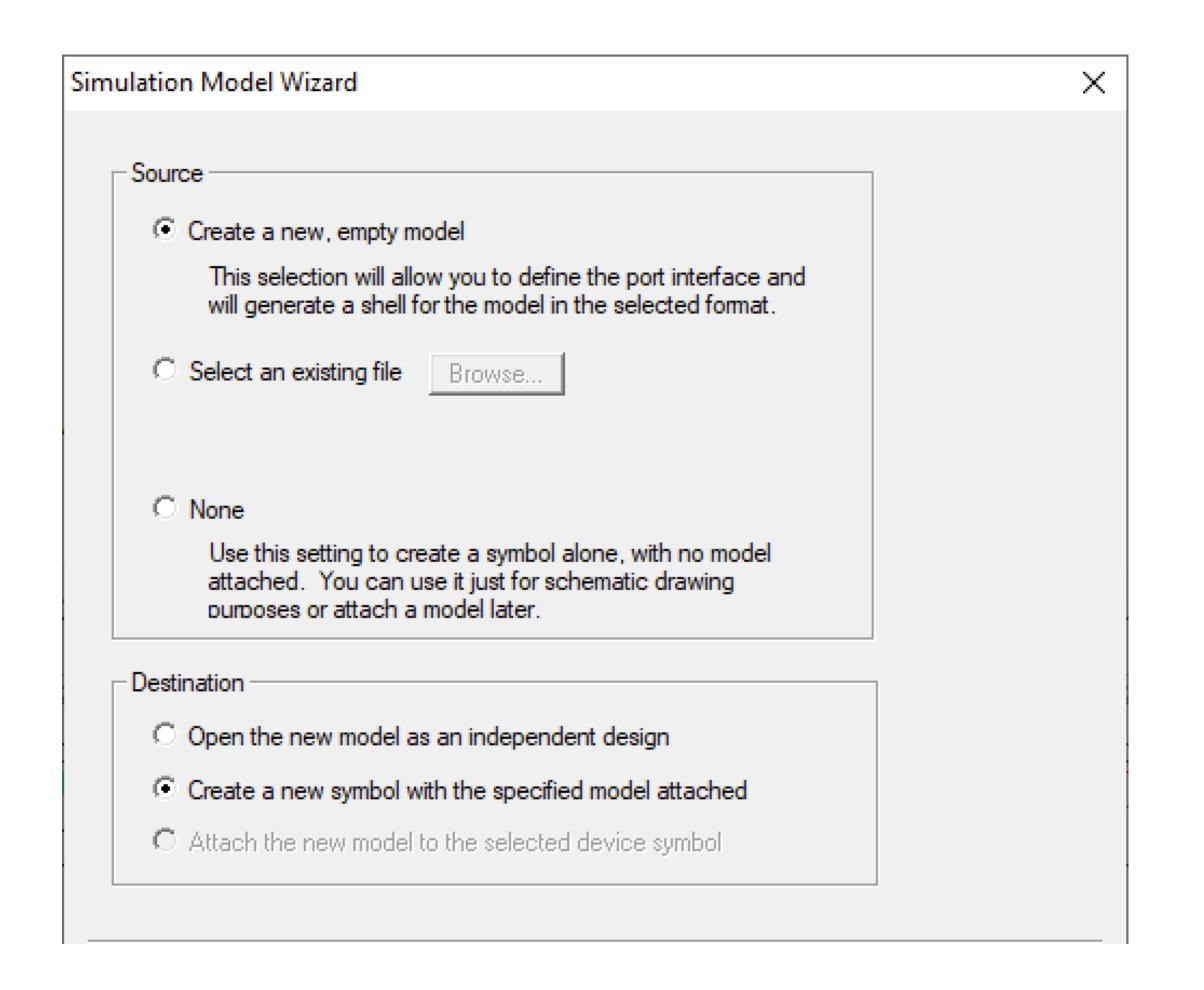

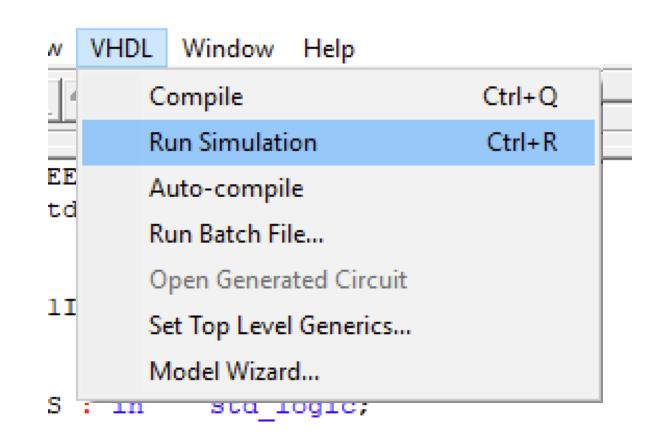

```

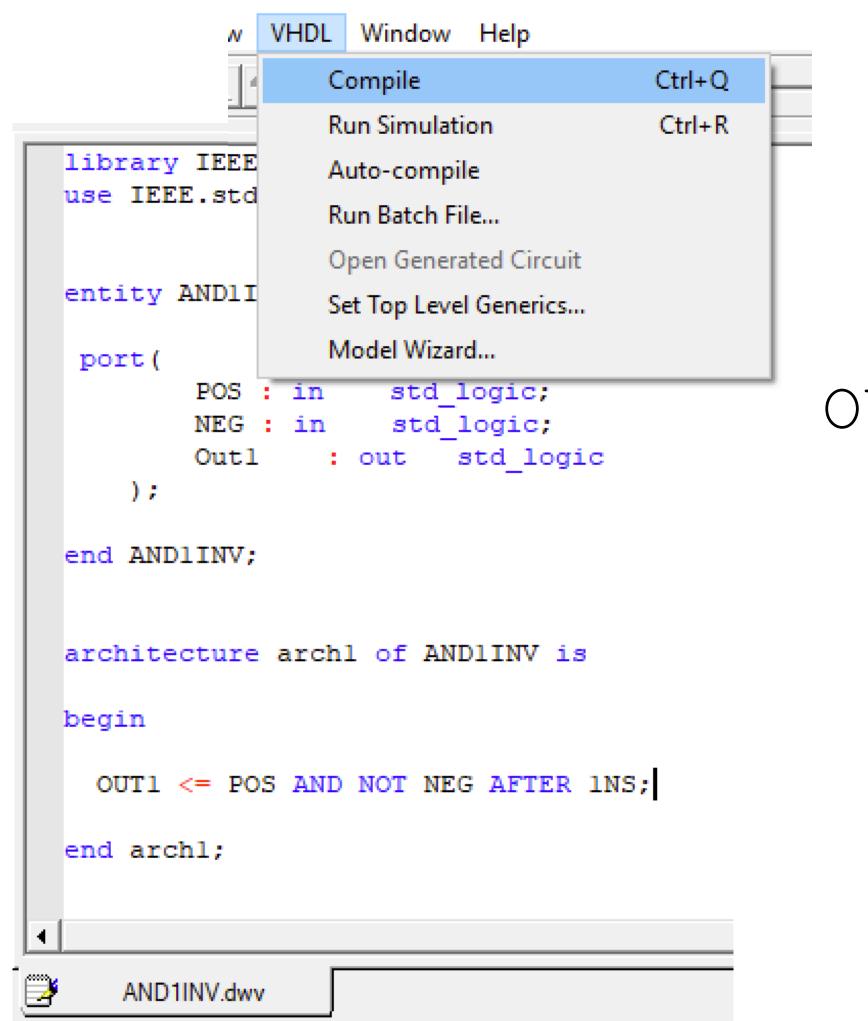

VHDL Window Help

Compile

Ctrl+Q

Run Simulation

Ctrl+R

library IEEE

Auto-compile

use IEEE.std

Run Batch File...

Open Generated Circuit

entity AND1I

Set Top Level Generics...

Model Wizard...

port (

POS : in

std logic;

std logic;

NEG : in

: out

std logic

Outl

);

end ANDLINV;

architecture archl of ANDLINV is

begin

OUT1 <= POS AND NOT NEG AFTER 1NS;

end archl;

AND1INV.dwv

```

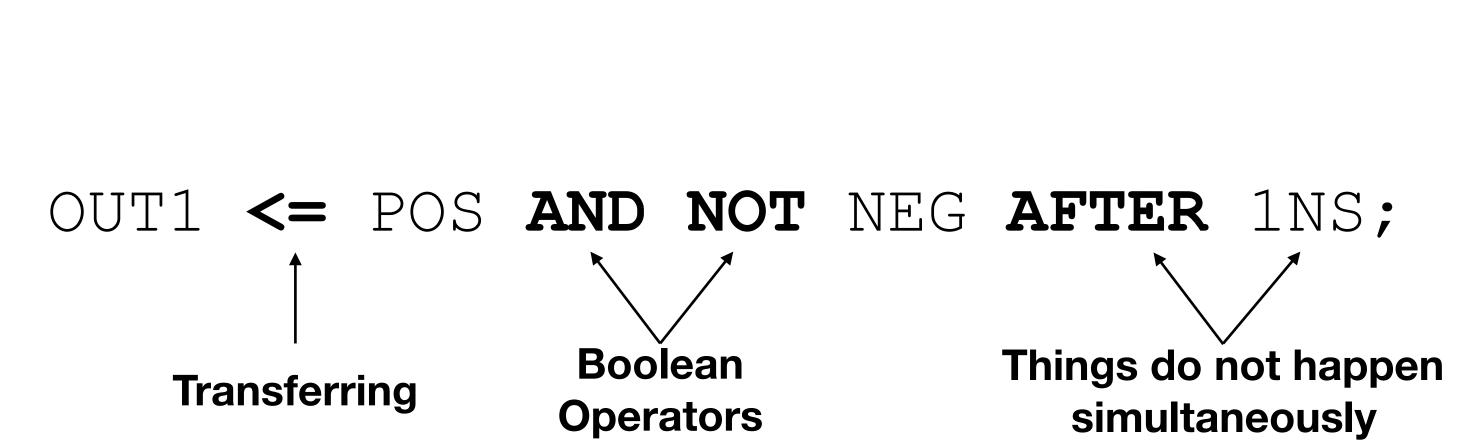

```

OUT1 <= POS AND NOT NEG AFTER 1NS;

Boolean

Transferring

Operators

```

P2 VHDL

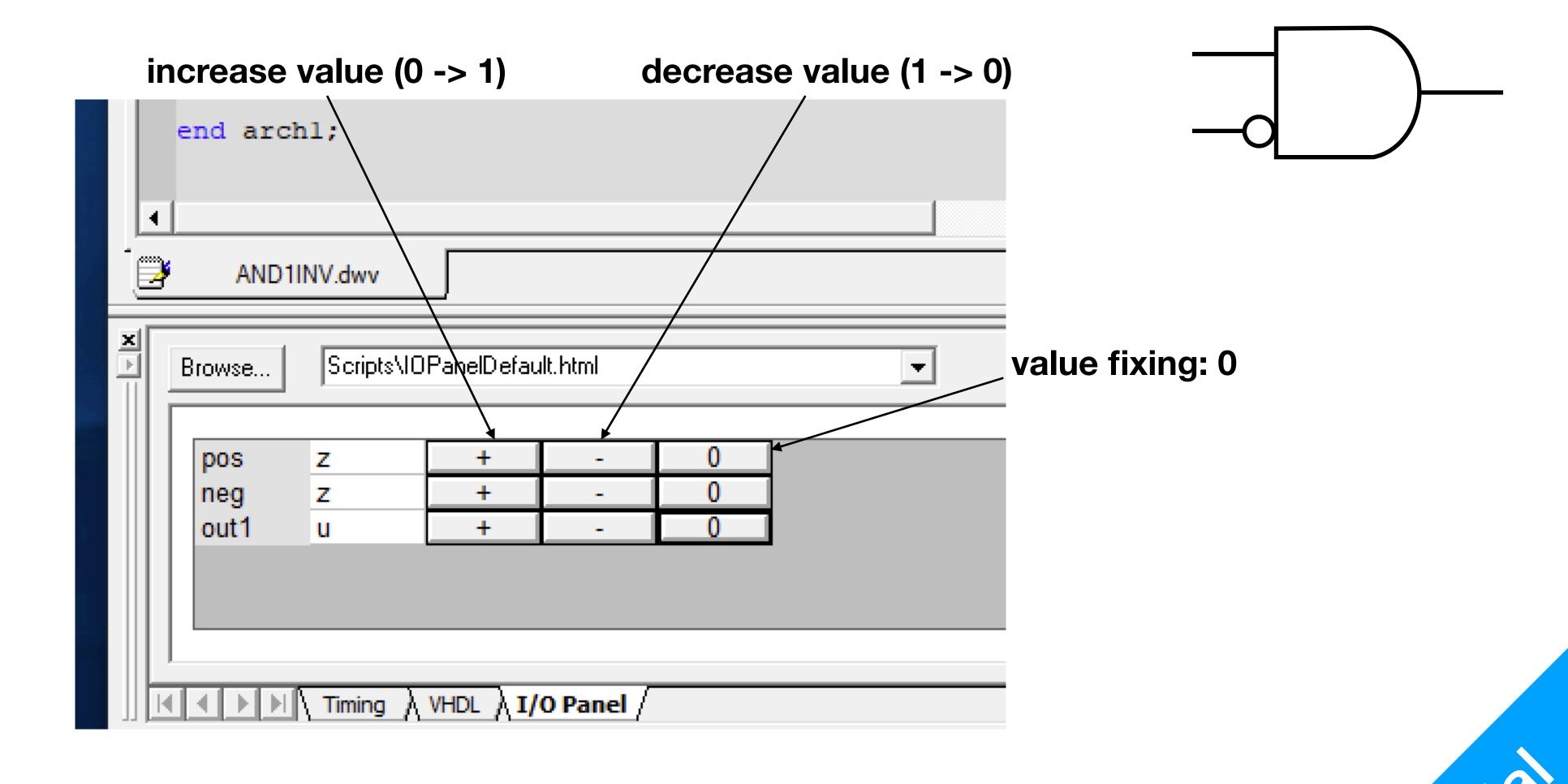

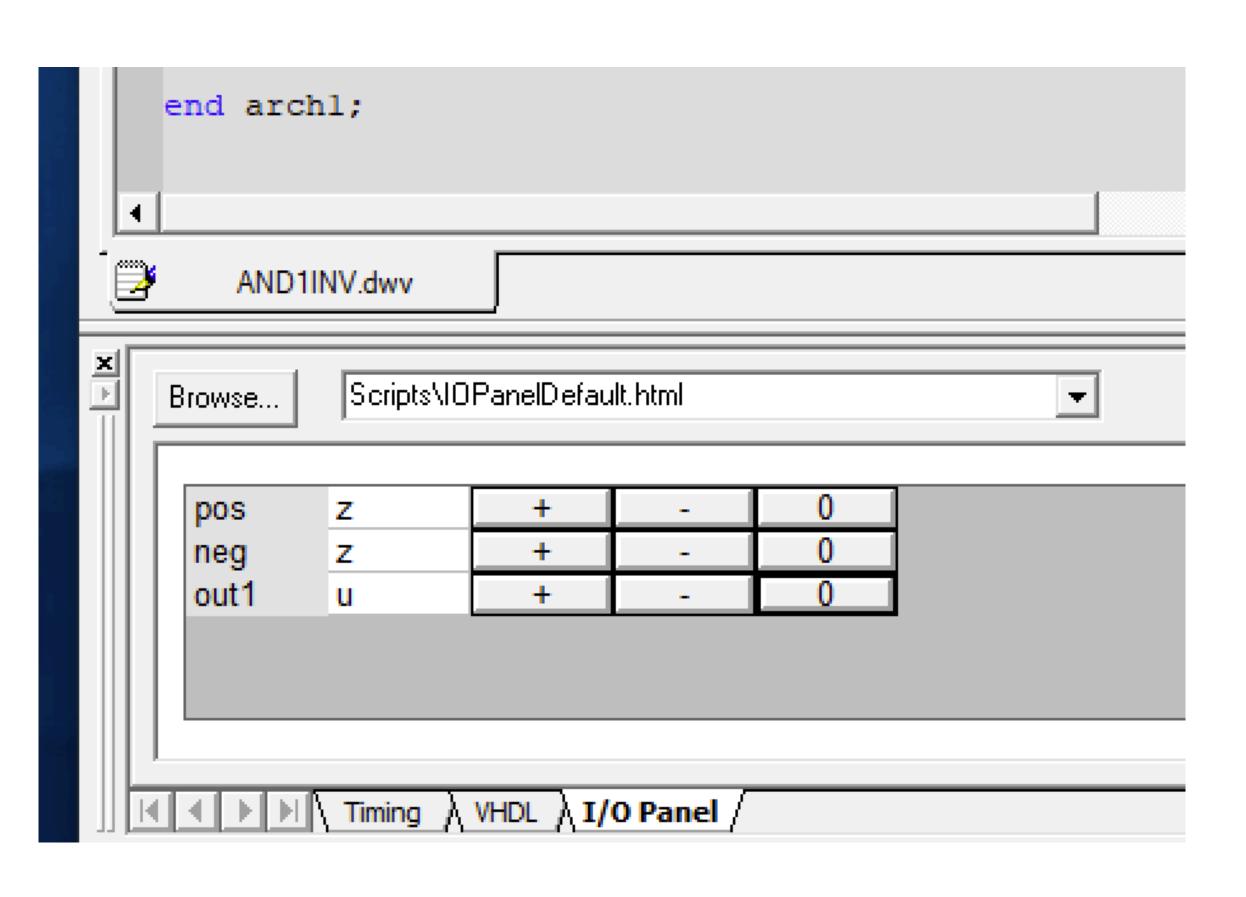

### Run Simulation

### Run Simulation

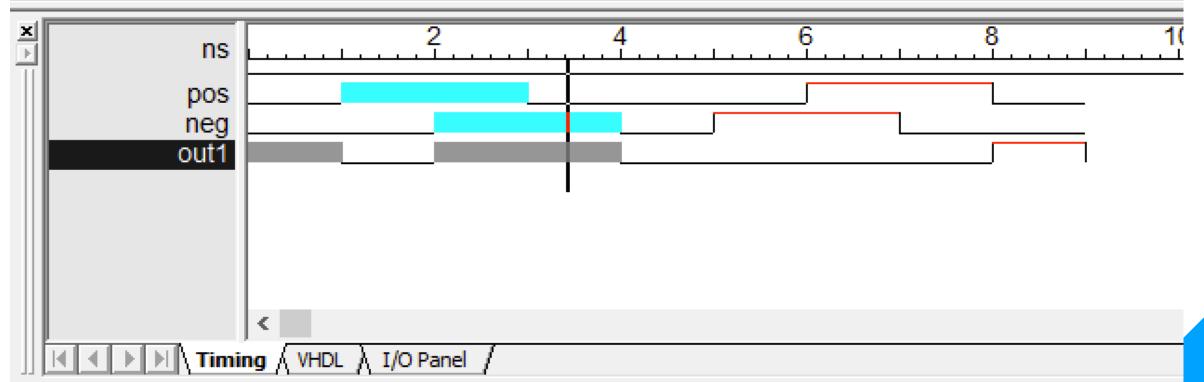

7. Play with the buttons in the I/O panel

P2 VHDL

### Run Simulation

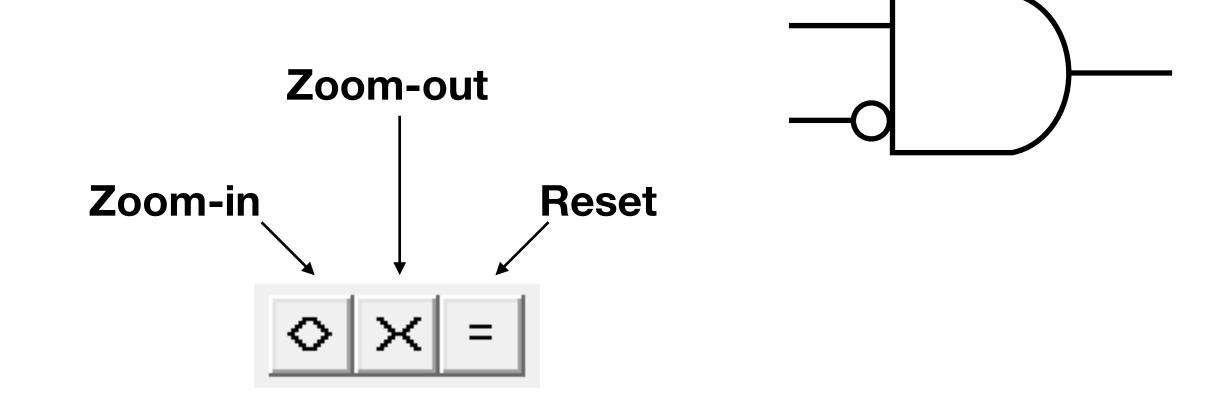

8. Changes are reflected in the Timing Diagram. Use Zoom panel to Zoom In and Out

### Exe1: 1-bit Half Adder

- Create a new component in VHDL called HalfAdder1

- Input: X, Y

- Output: S, C

- Don't use AFTER

### Exe1: 1-bit Half Adder

architecture arch1 of HalfAdder is

begin

$$S \le X XOR Y$$

;

$$C \ll X AND Y;$$

end arch1;