### CSCI 150 Introduction to Digital and Computer System Design Lecture 2: Combinational Logical Circuits V

Jetic Gū 2020 Winter Semester (S1)

# 2 Types of Knowledge

### 2 Types of Knowledge **P0** XXXXXXX

- 1. I know this by heart!

- 2. Whatever, I can look it up when I need it.

- The rest of lecture 2 today.

- You need to know where to look at if you don't remember later!

Important Definitions, Number Systems and Arithmetics, Boolean Algebra

## Overview

- Focus: Boolean Algebra

- Architecture: Combinatory Logical Circuits

- Textbook v4: Ch2 2.8, 2.9. 2.10; v5: Ch2 2.6, 2.7

- Core Ideas:

- 1. Other Gate Types: XOR, NAND, NOR, Buffer, High-Impedance, Odd Function

- 2. Lecture 2 Review

# Boolean Algebra I-III

- AND, OR, NOT Operators and Gates

- Simple digital circuit implementation

- Algebraic manipulation using Binary Identities

- II. Standard Forms

- Minterm & Maxterm

- Sum of Products & Product of Sums

- III. Optimisation Using K-Map (For 2,3,4 Variables)

# Other Gate Types

Delay Propagation XOR, NAND, NOR, Buffer

| $\frac{\mathbf{P} \mathbf{P} \mathbf{P} \mathbf{P} \mathbf{P}}{\mathbf{P} \mathbf{P} P$ |   |   |

|-----------------------------------------------------------------------------------------|---|---|

| 0                                                                                       | 1 | 0 |

|                                                                                         |   |   |

| 1                                                                                       | 1 | 0 |

|                                                                                         |   |   |

|                                                                                         |   |   |

| 3                                                                                       | 4 | 5 |

| $\frac{\mathbf{Poiss}}{\mathbf{Poiss}} = X$ | <b>Y</b> ) |   |

|---------------------------------------------|------------|---|

| 0                                           | 1          | 0 |

| 1                                           | 1          | 0 |

|                                             |            |   |

|                                             | 1          |   |

| 3                                           | 4          | 5 |

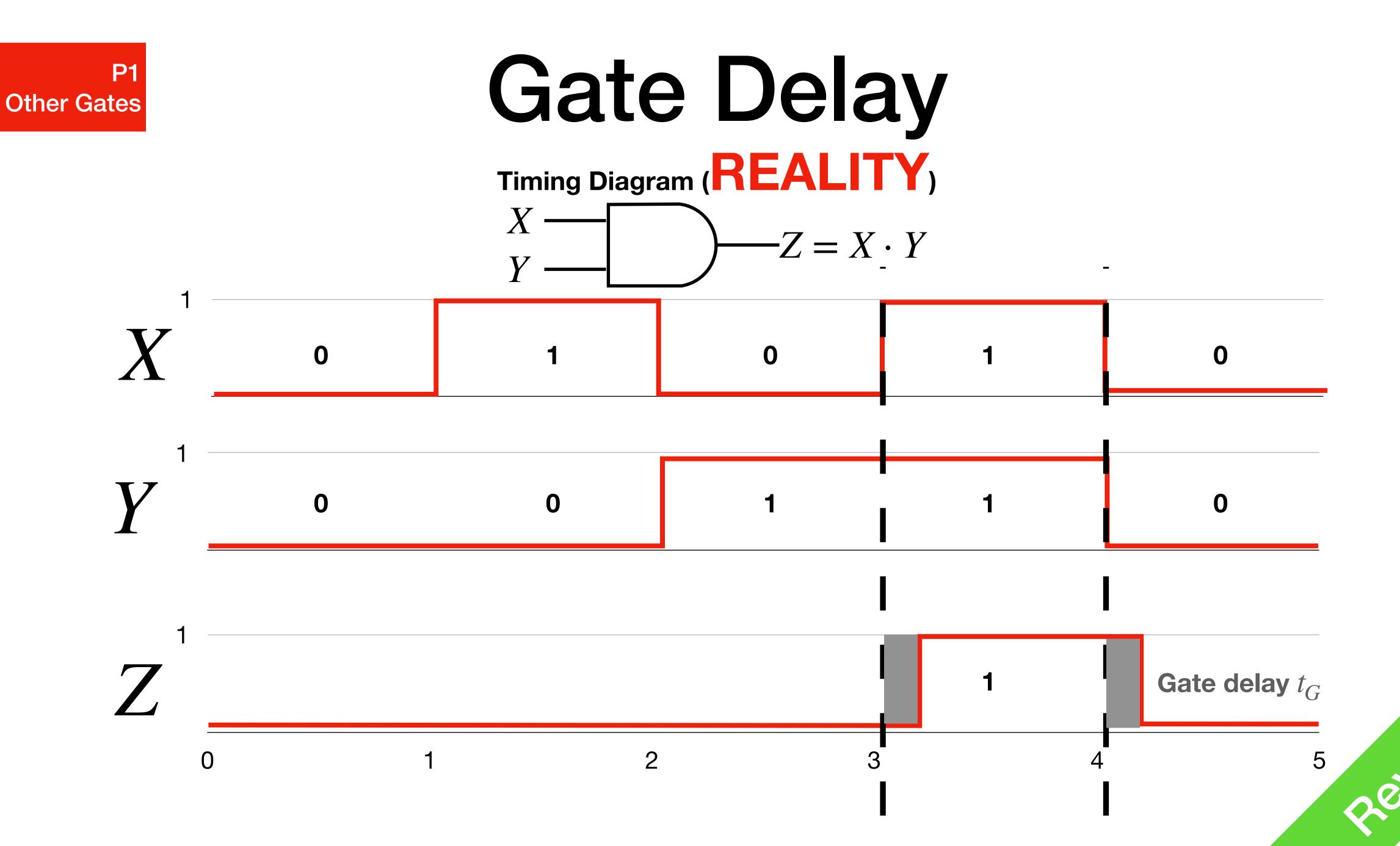

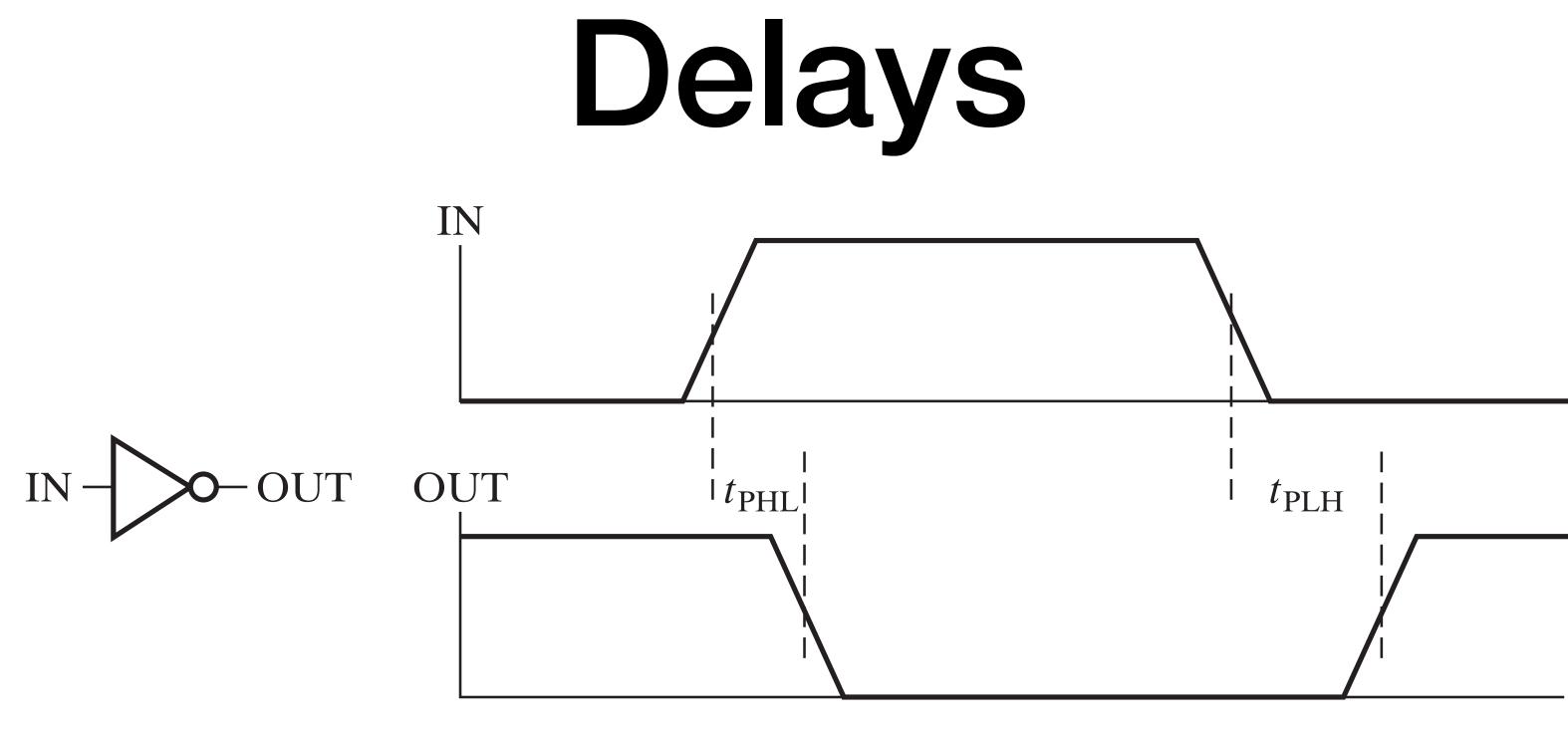

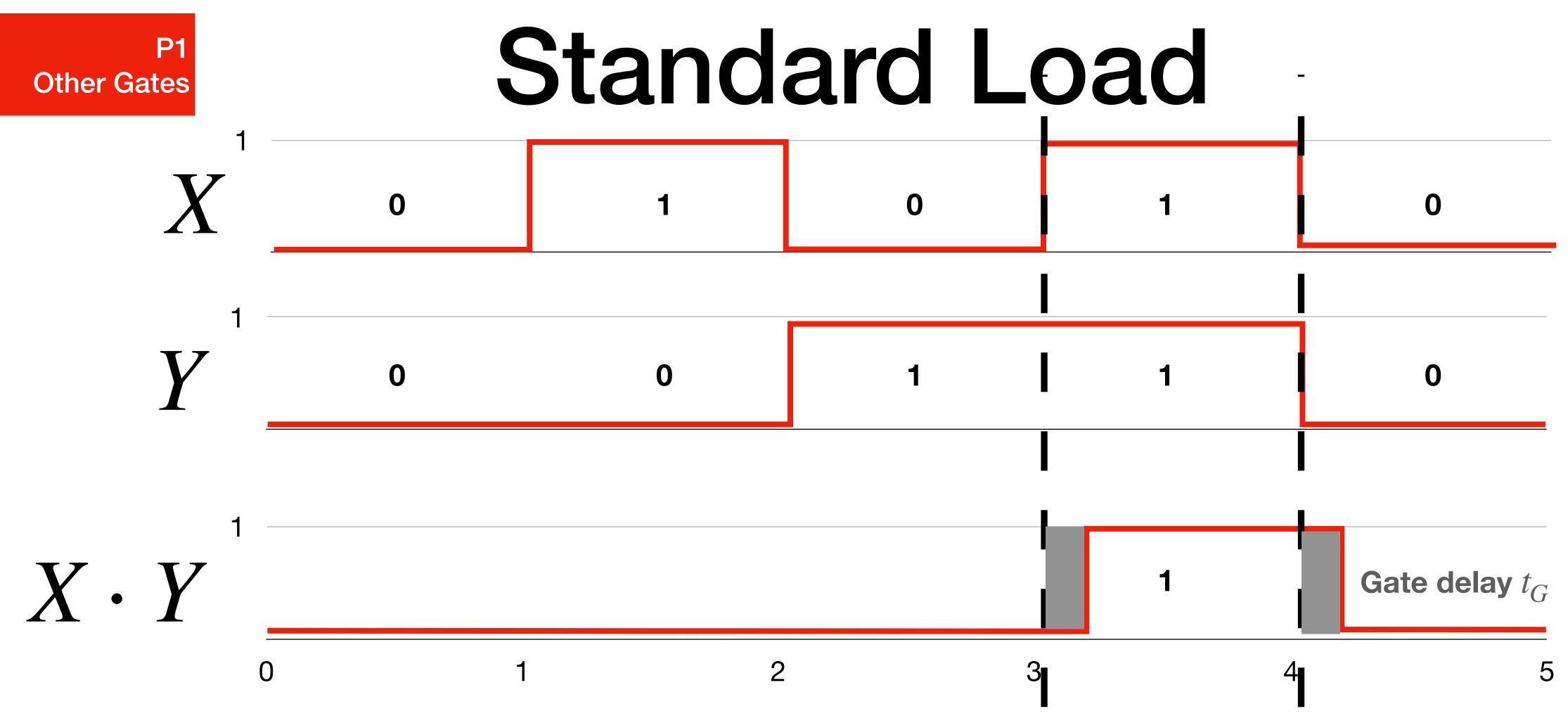

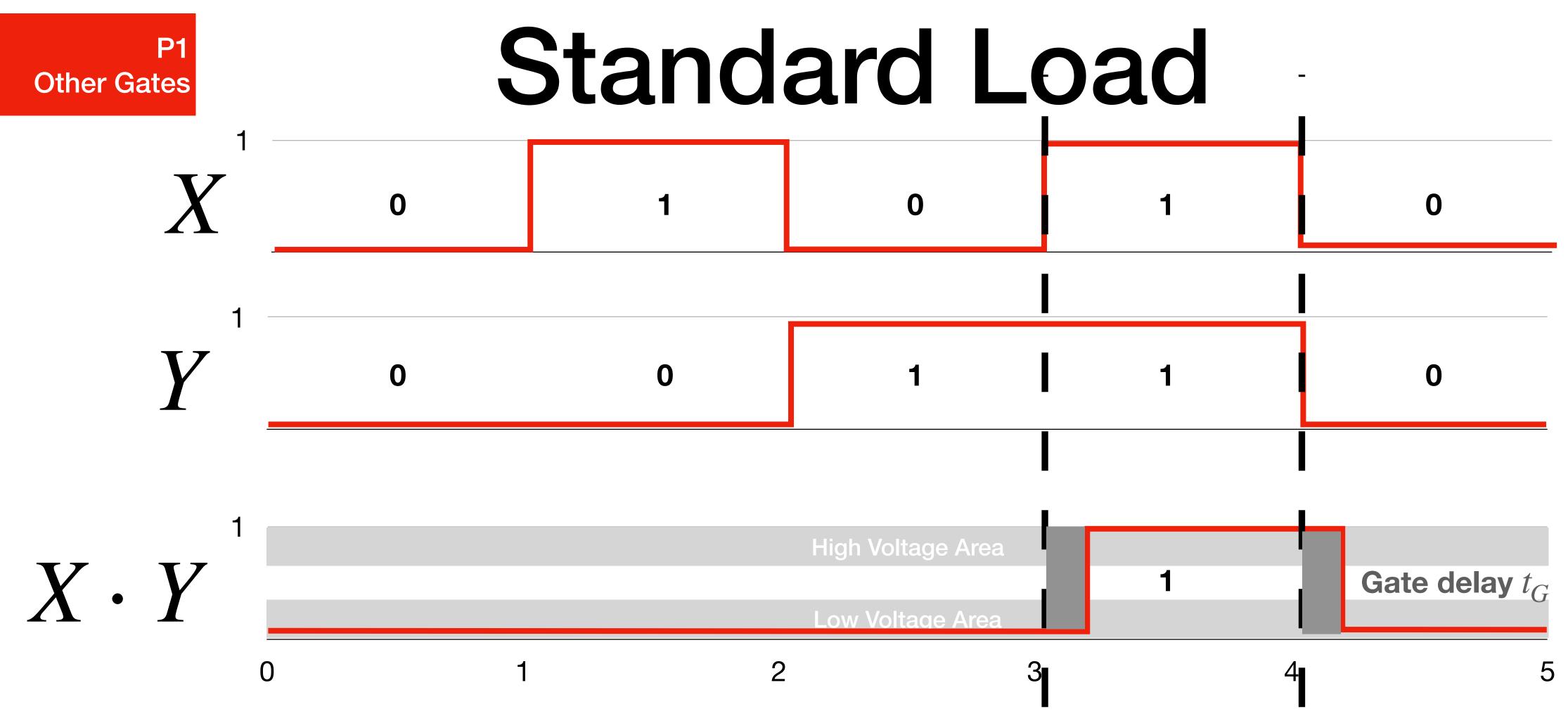

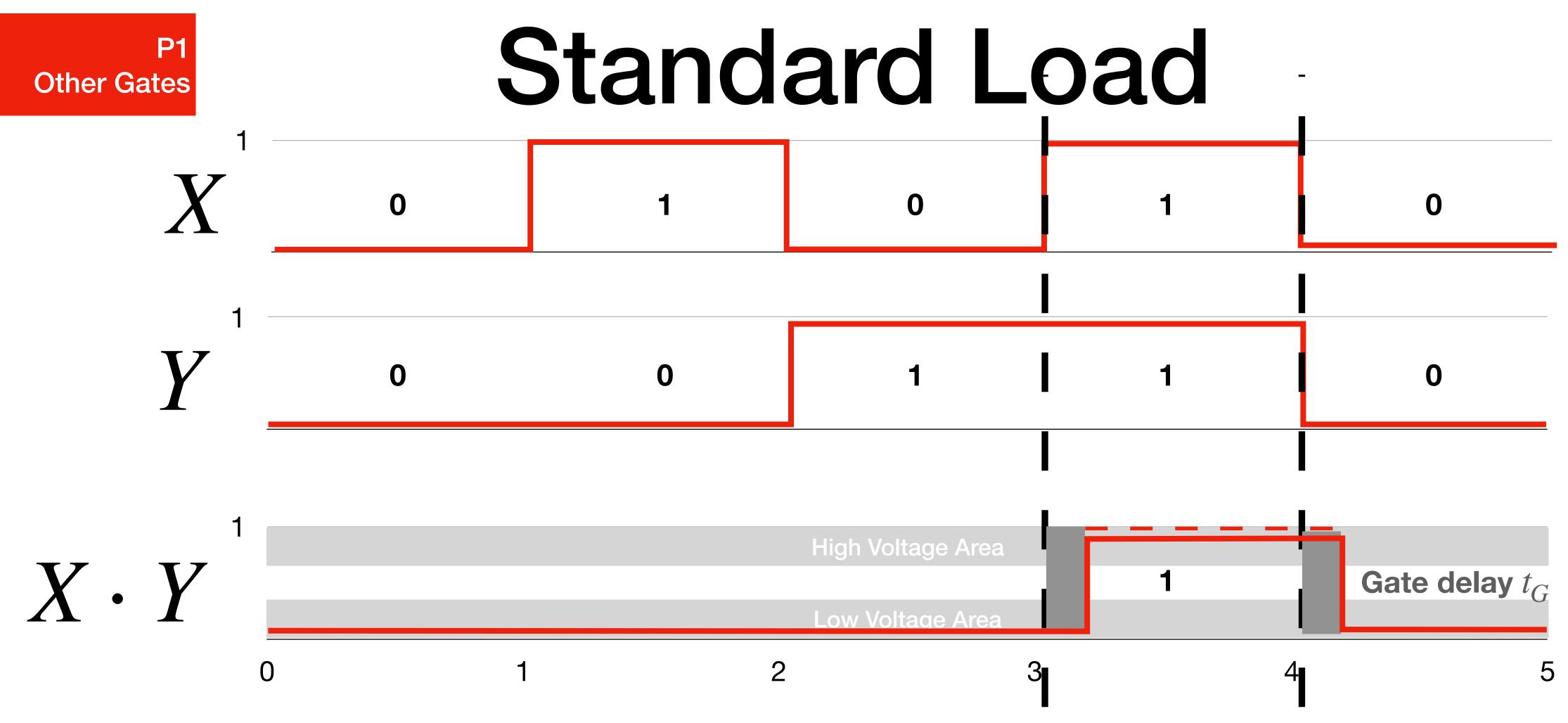

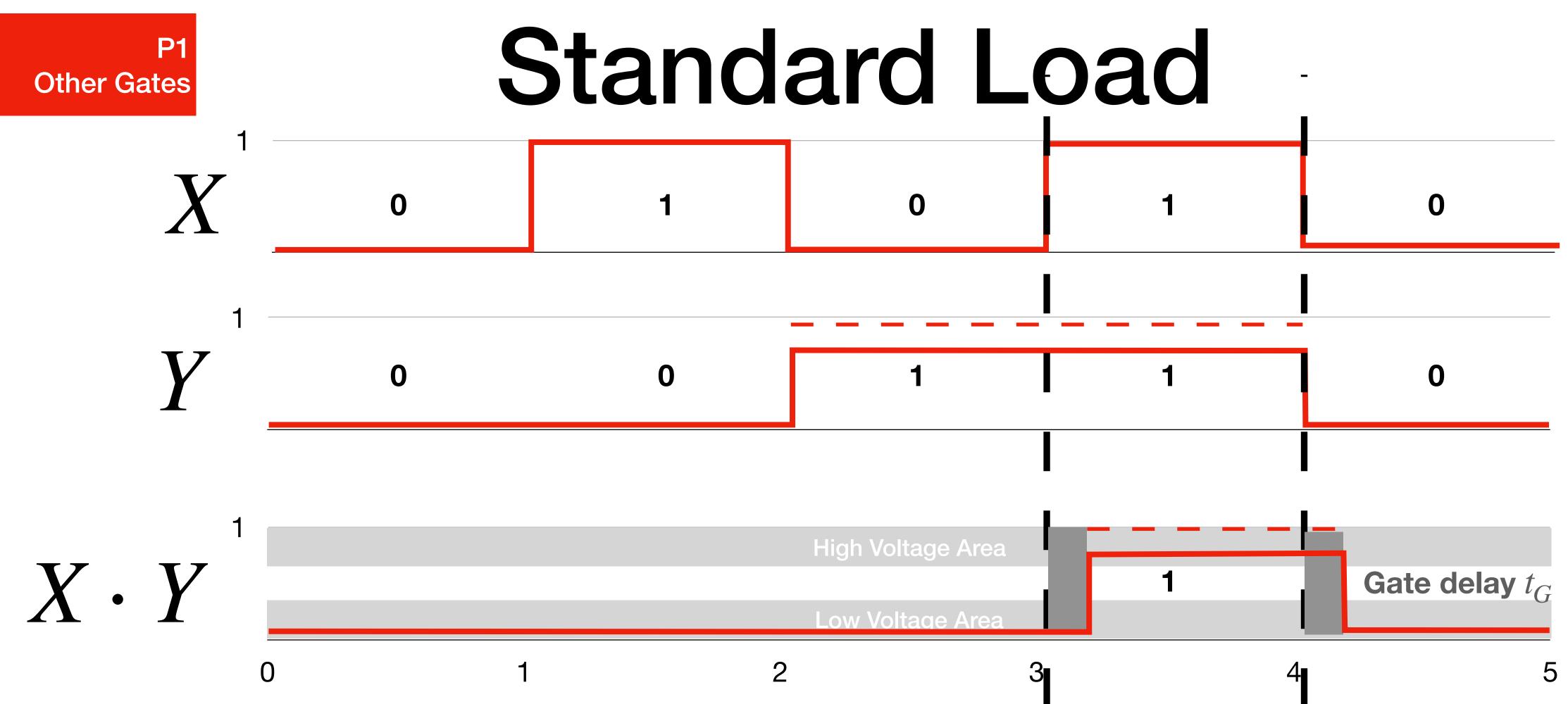

# Delays

- Gate Delay

- to output (of a Gate)

- Propagation Delay

- to output (of a Circuit)

### • The time required for a change in value of a signal to propagate from input

### • The time required for a change in value of a signal to propagate from input

•  $t_{pd}$ : Propagation Delay: longest time for propagating from input to output

**P1**

**Other Gates**

•  $t_{PHL}$ : Hight2Low propagation time;  $t_{PLH}$ : Low2High propagation time;

$t_{\rm pd} = \max\left(t_{\rm PHL}, t_{\rm PLH}\right)$

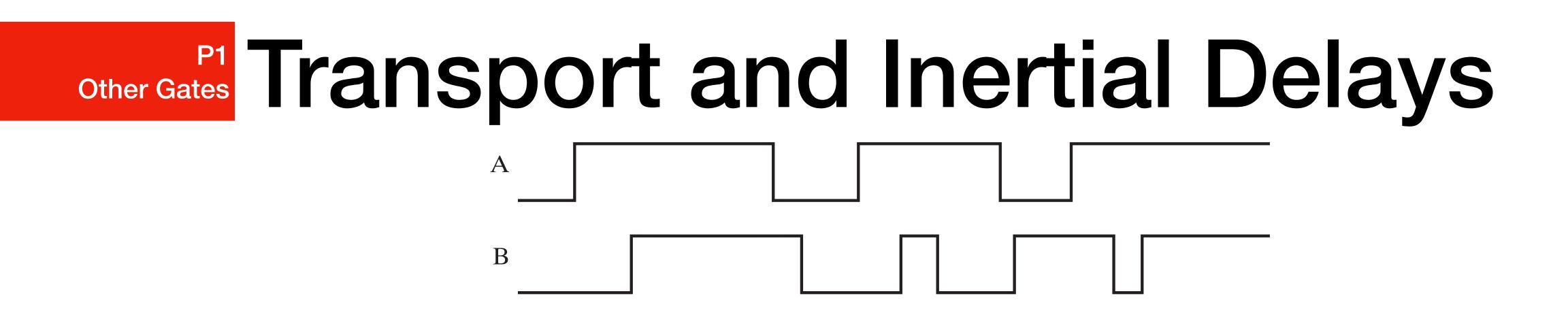

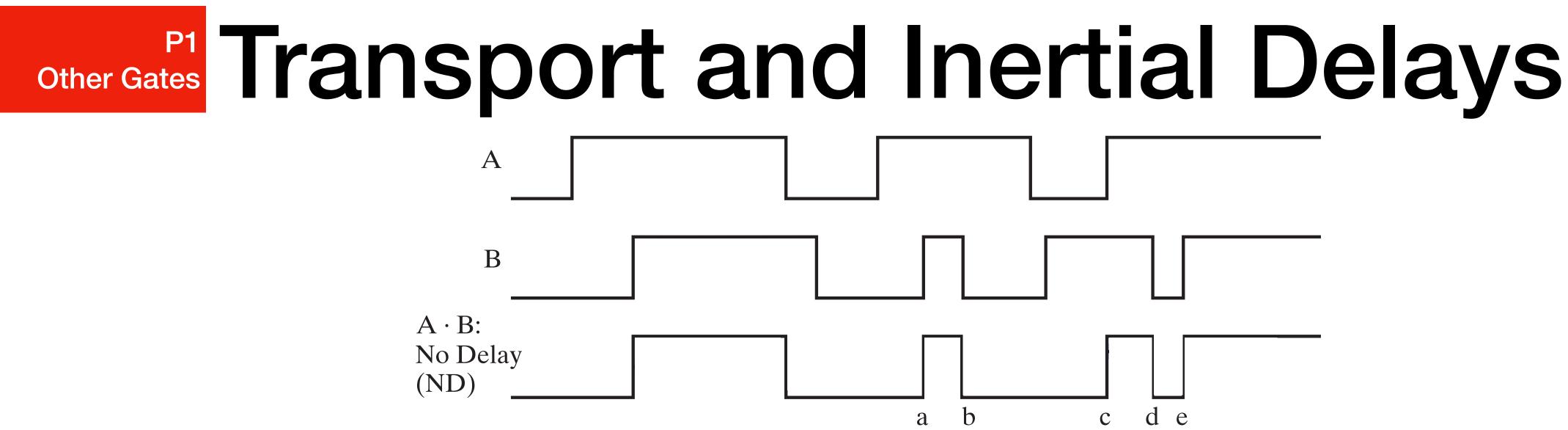

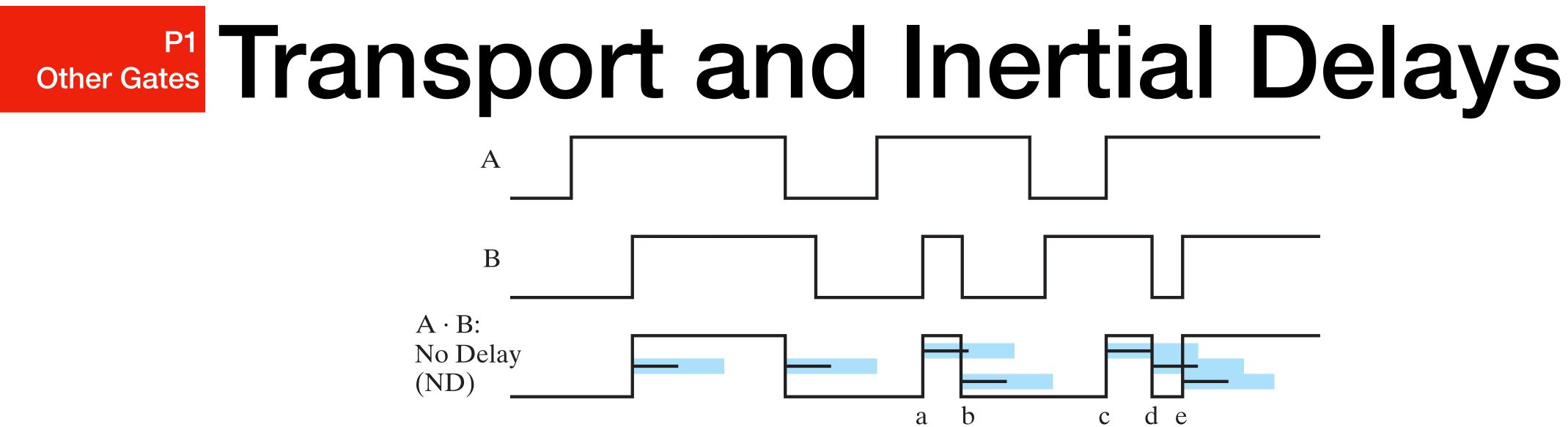

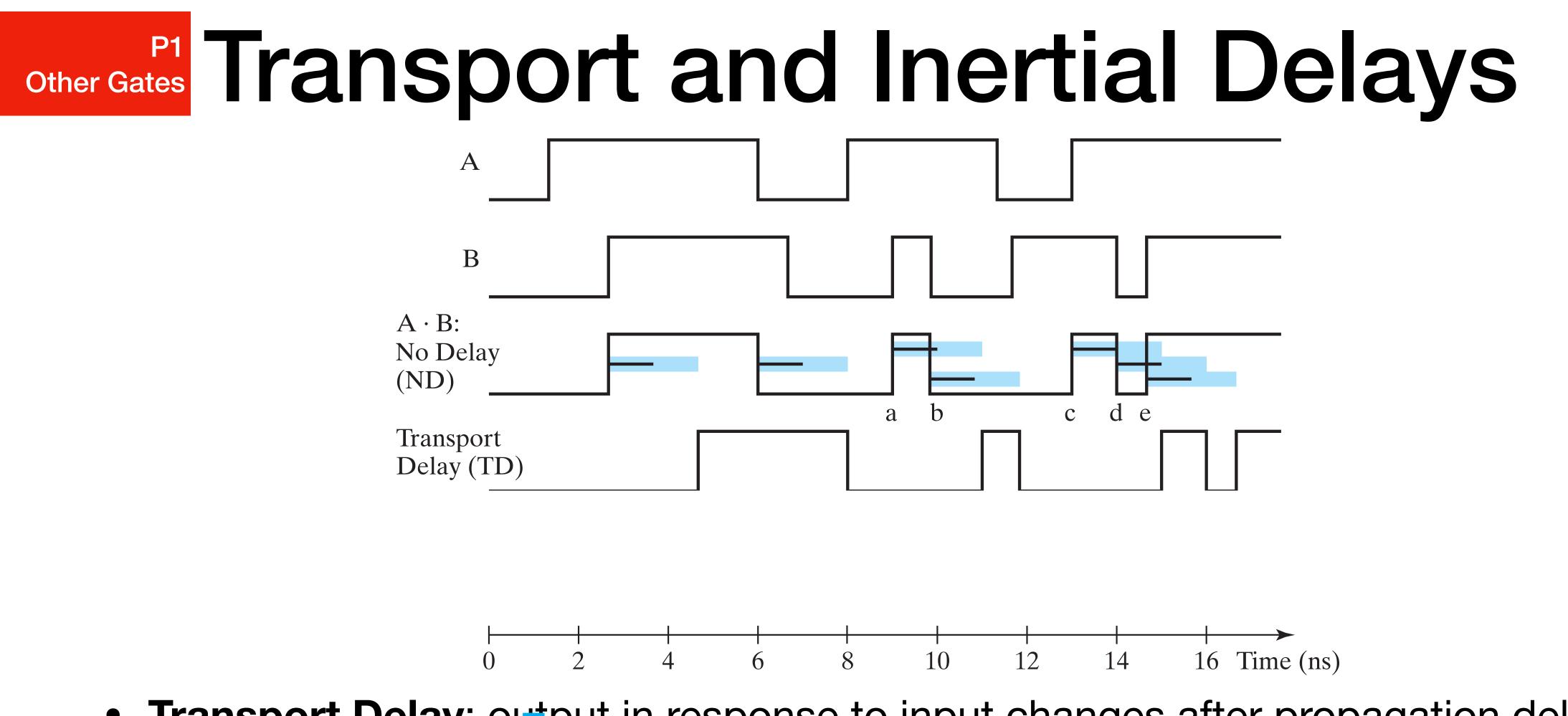

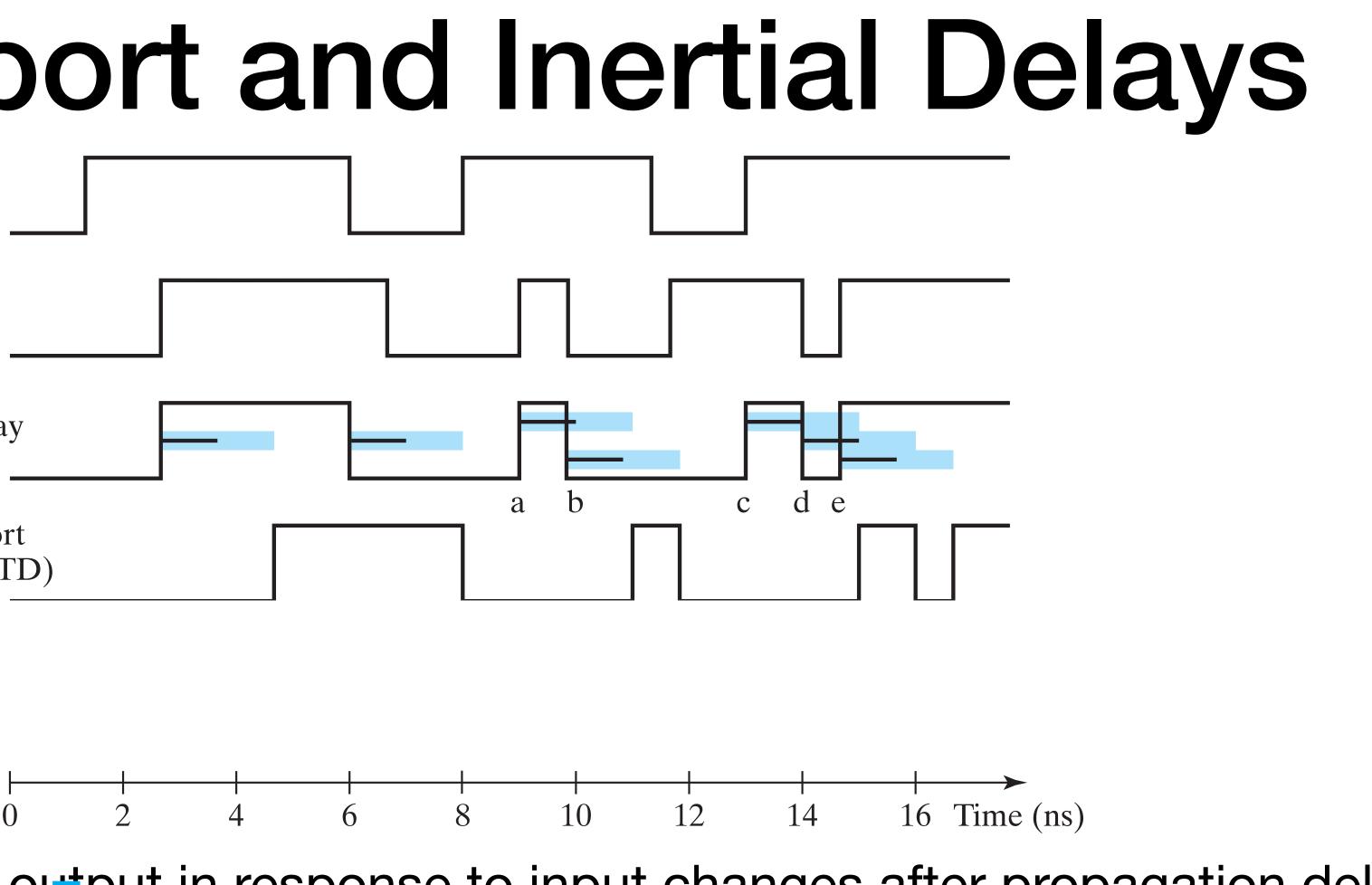

• **Transport Delay**: output in response to input changes after propagation delay

Transport Delay: output in response to input changes after propagation delay

• Inertial Delay: if a value changes twice in a short time (rejection time), ignore

# Other Gates P1 Delay

# Other Gates P1 Parameters of Gate Delay

• Fan-in number of inputs of a logic gate

# Other Gates P1 Delay

- Fan-in number of inputs of a logic gate

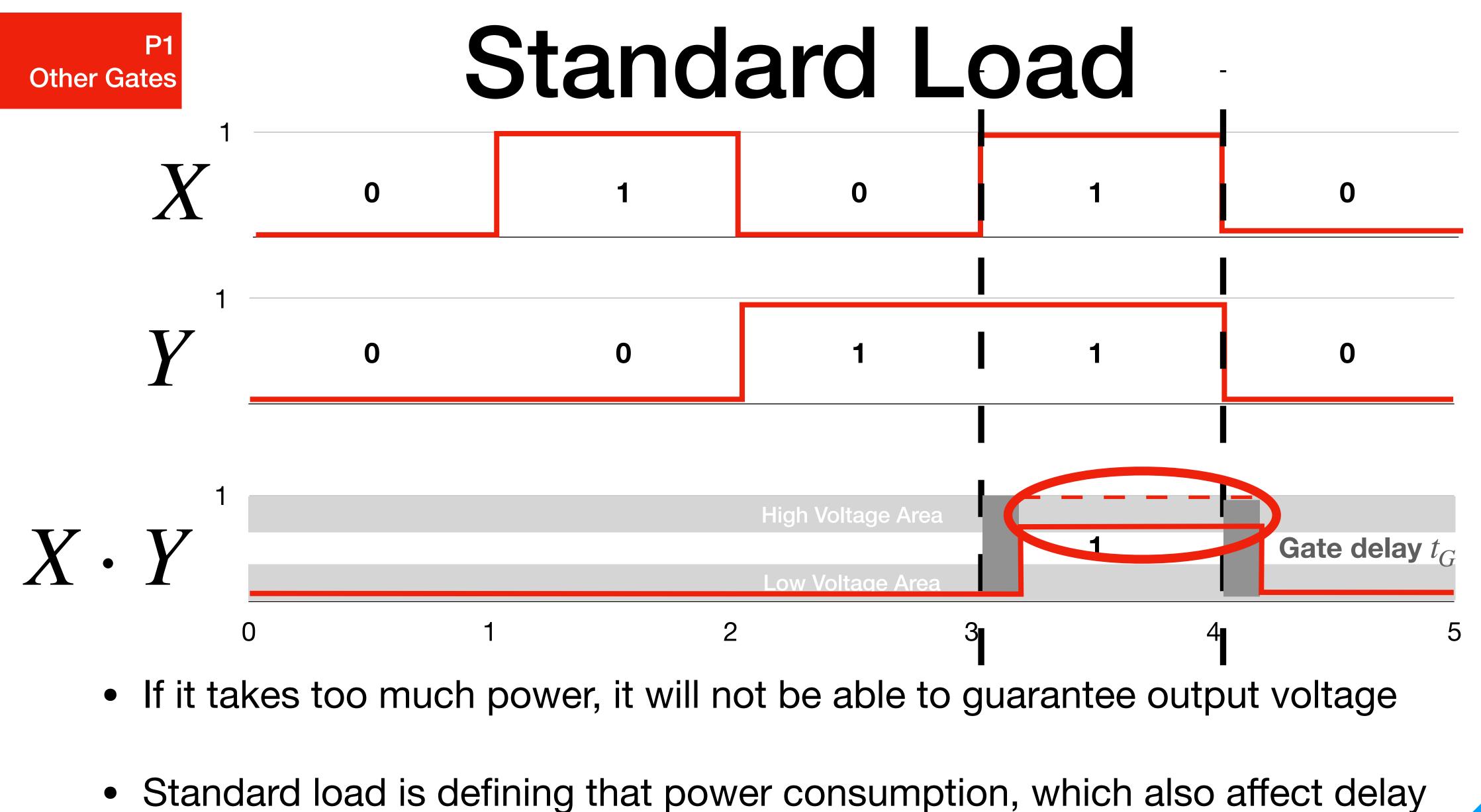

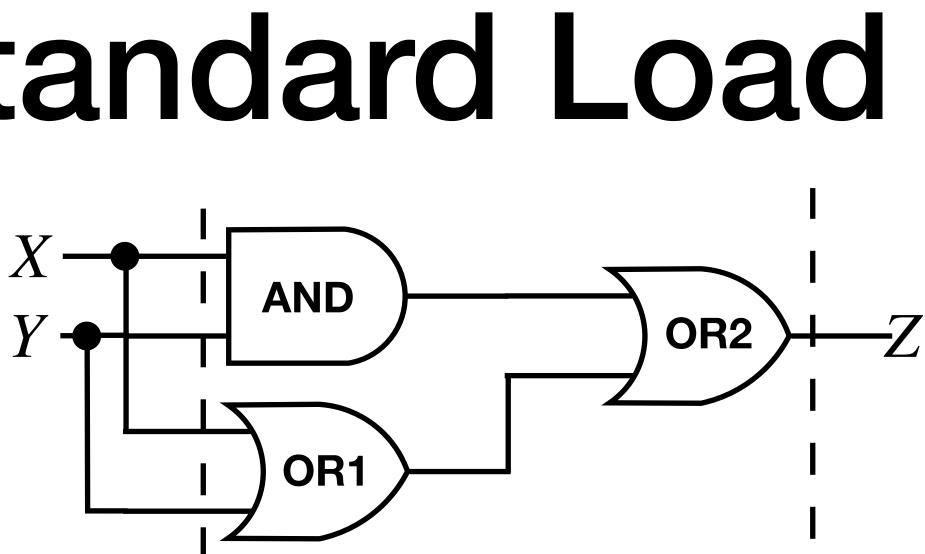

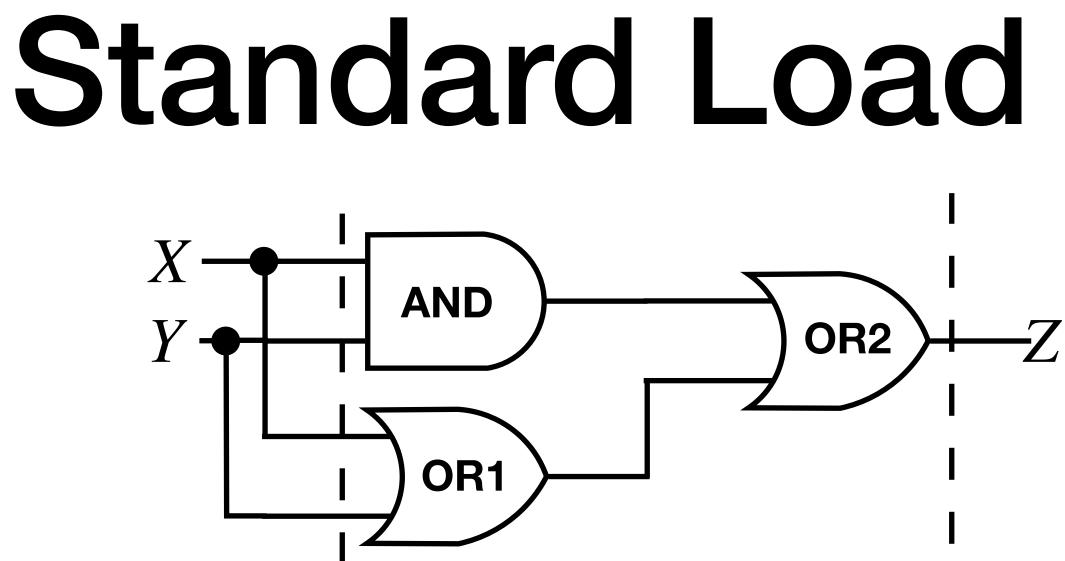

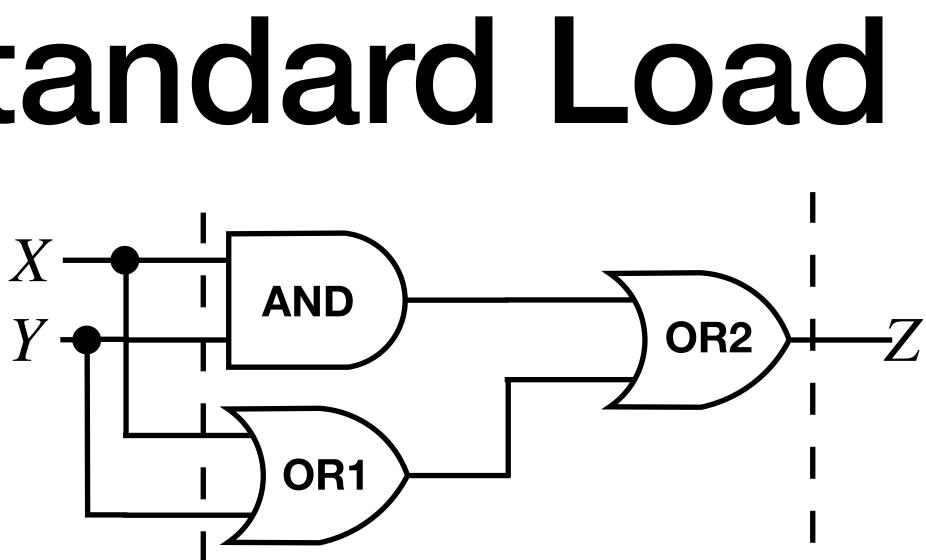

- Fan-out (standard load) in the guaranteed range is called the standard load or fan-out

number of gates that each logic gate can drive while providing voltage levels

Digital circuits are driven by power, each component also takes power

Digital circuits are driven by power, each component also takes power

• Digital circuits are driven by power, each component also takes power

• Changes in input voltage can also affect output voltage

**P1**

**Other Gates**

- OR Gate: 0.8 SL; AND Gate: 1.00 SL;

- Delay for AND:  $t_{pd} = 0.07 + 0.021 \times \sum InputSL$

- Delay for OR:  $t_{pd} = 0.05 + 0.02 \times \sum InputSL$

**P1**

**Other Gates**

- Estimation for OR2 • OR Gate: 0.8 SL; AND Gate: 1.00 SL;  $t_{pd} = 0.05 + 0.02 \times (0.8 + 1.00) = 0.086$ ns

- Delay for AND:  $t_{pd} = 0.07 + 0.021 \times \sum InputSL$

- Delay for OR:  $t_{pd} = 0.05 + 0.02 \times \sum InputSL$

- Precise estimation is very hard, since we lack a lot of these information

- We can ignore this computation, but you should know roughly

# Other Gates

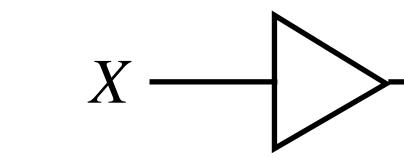

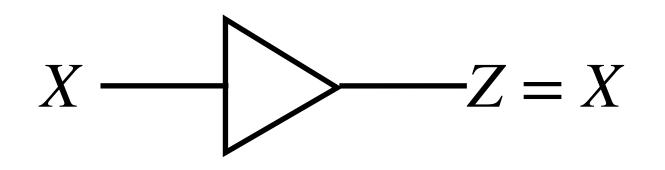

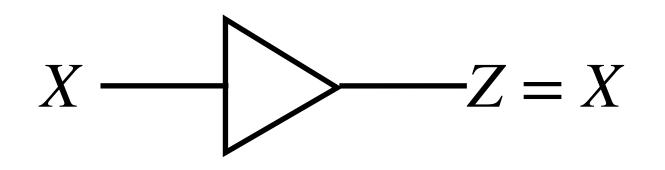

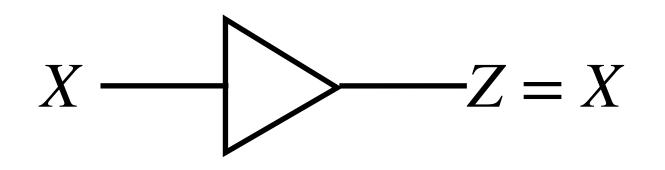

Buffer

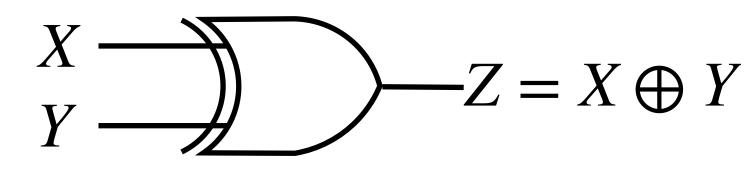

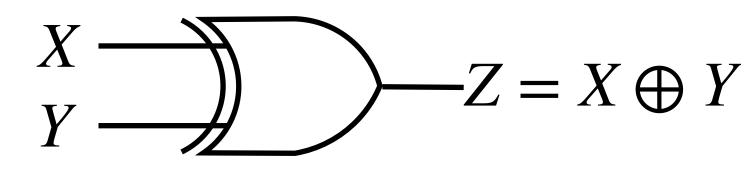

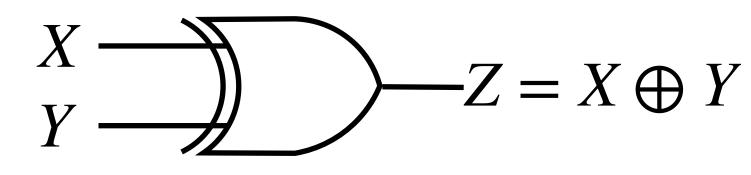

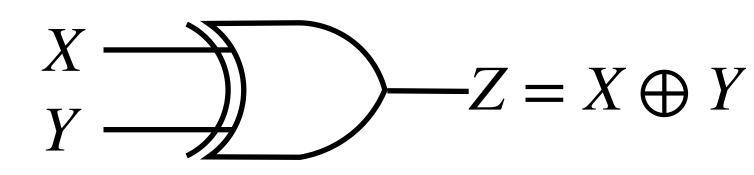

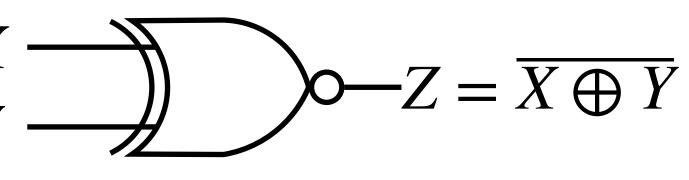

$-Z = X \oplus Y$

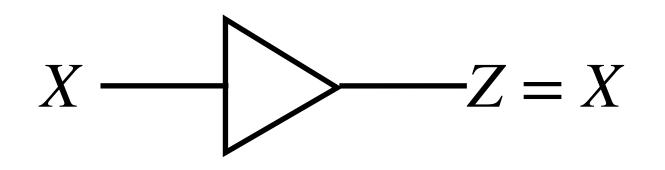

-Z = X

**-**Z

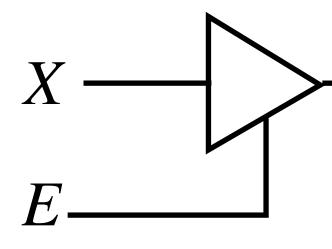

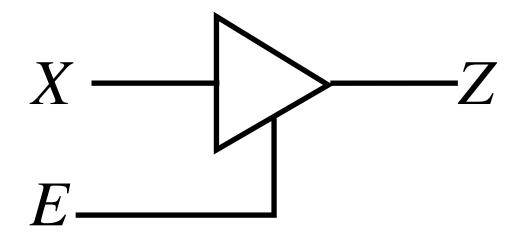

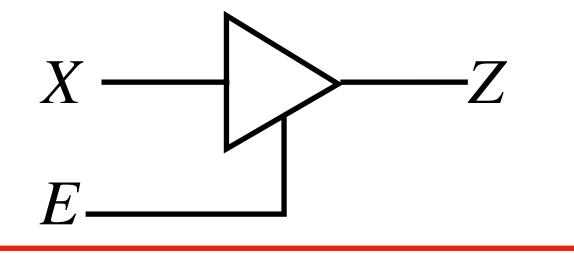

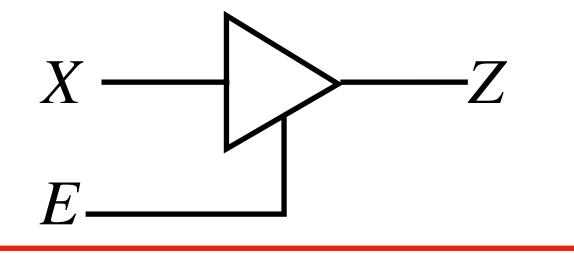

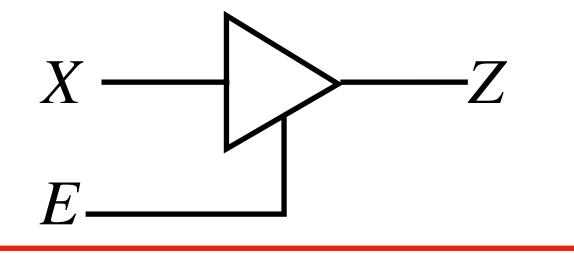

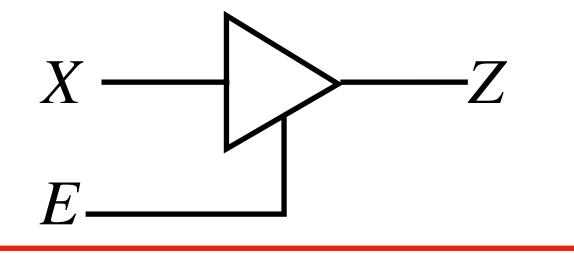

**3-State Buffer**

## Buffer

- Has delay

- Increases output Voltage e.g.: input 0.8 V, output 1.0 V

## **3-State Buffer**

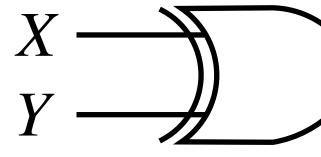

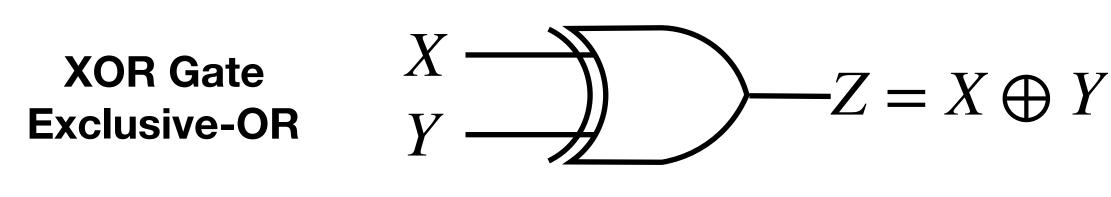

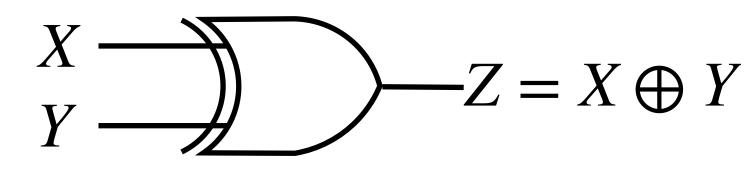

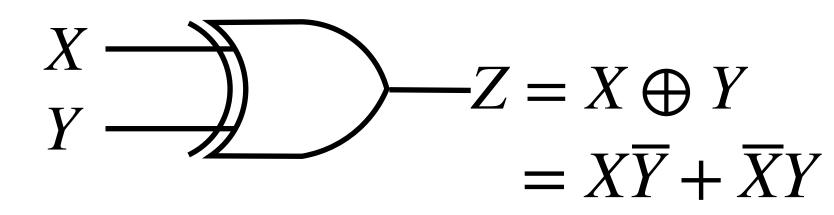

### XOR Gate Exclusive-OR

Buffer

**3-State Buffer**

- Has delay

- Increases output Voltage

e.g.: input 0.8 V, output 1.0 V

- When E = 0, outputs no electricity (Open circuit/Hi-Z/High Impedance)

## **3-State Buffer**

### XOR Gate Exclusive-OR

Buffer

**3-State Buffer**

• Has delay

- Increases output Voltage

e.g.: input 0.8 V, output 1.0 V

- When E = 0, outputs no electricity (Open circuit/Hi-Z/High Impedance)

## **3-State Buffer**

### XOR Gate Exclusive-OR

Buffer

**3-State Buffer**

• Has delay

- Increases output Voltage

e.g.: input 0.8 V, output 1.0 V

- When E = 0, outputs no electricity (Open circuit/Hi-Z/High Impedance)

# **3-State Buffer**

### XOR Gate Exclusive-OR

Buffer

**3-State Buffer**

3-State Buffer Truth Table

| E | X | Z    |

|---|---|------|

| 0 | 0 | Hi-Z |

| 0 | 1 | Hi-Z |

| 1 | 0 | 0    |

| 1 | 1 | 1    |

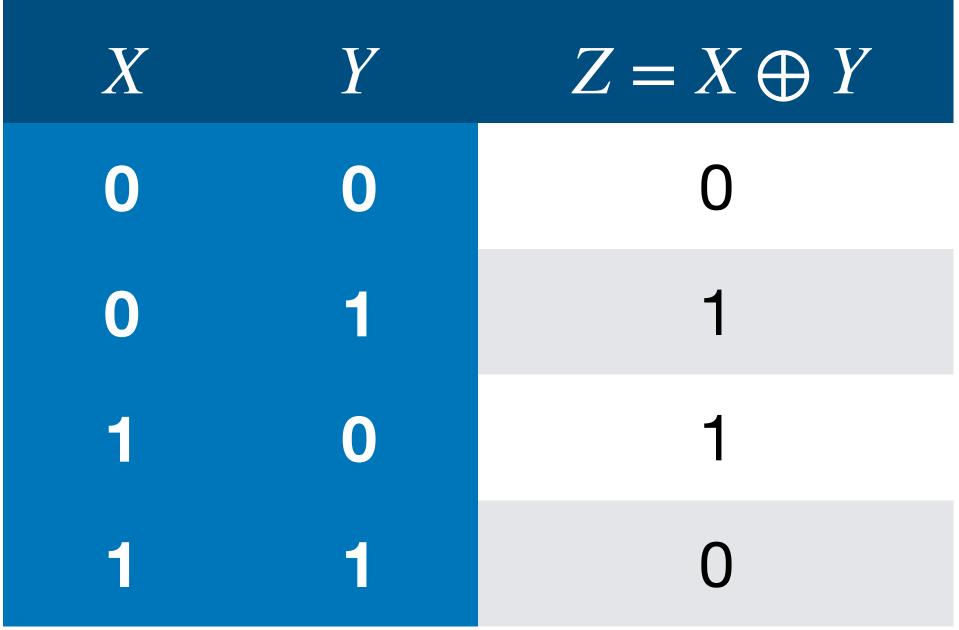

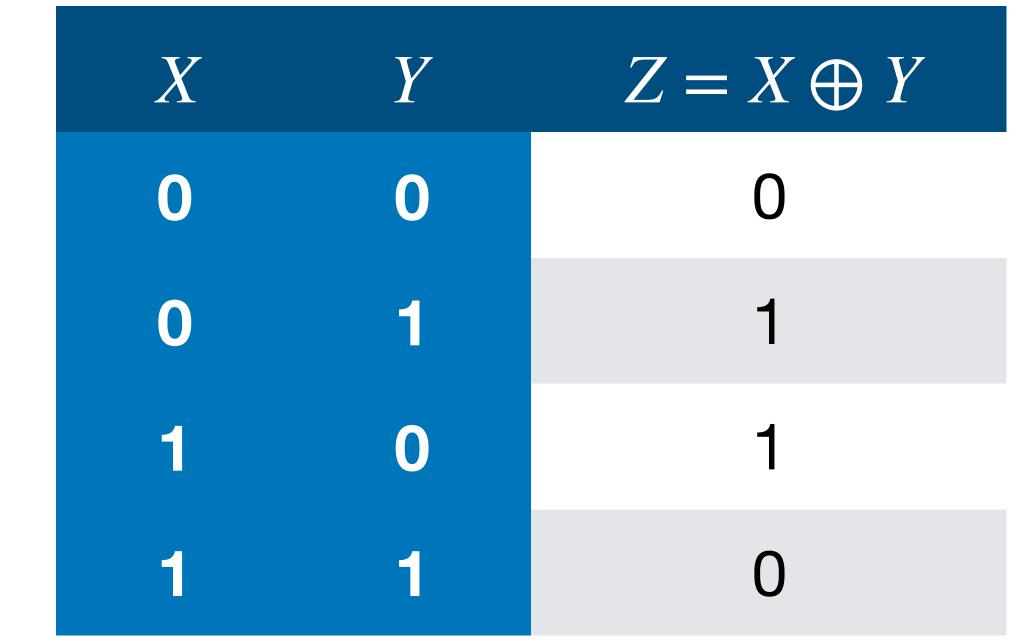

# XOR Gate

### XOR Truth Table

# XOR Gate

### XOR Gate Exclusive-OR

XOR Truth Table

- $X \oplus 0 = X$

- $X \oplus X = X$

- $X \oplus \overline{Y} = \overline{X \oplus Y}$

# XOR Gate

- $X \oplus 1 = \overline{X}$

- $X \oplus \overline{X} = 1$

- $\overline{X} \oplus Y = \overline{X \oplus Y}$

### Odd and Even Functions **P1 Other Gates**

- Odd Functions

- Outputs 1 if the number of 1s in the input is an Odd number

- 2 variables: XOR

- Even Functions

- Outputs 1 if the **number of 1s** in the input is an **Even** number

- 2 variables: XNOR

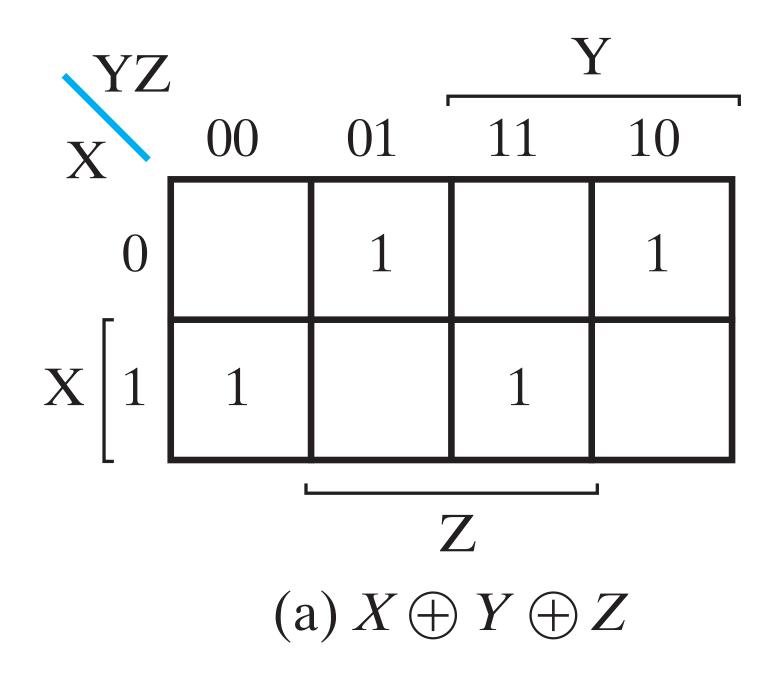

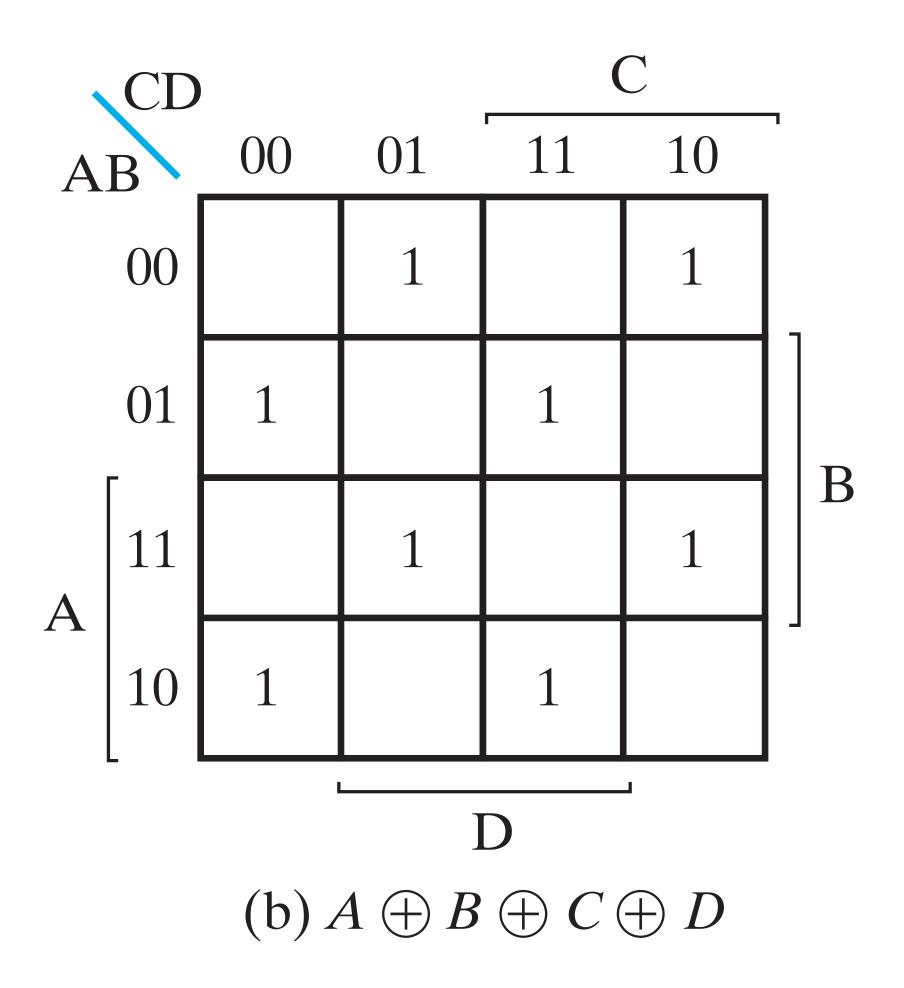

# Odd Function K-Map

P1 Other Gates

### (b) $A \oplus B \oplus C \oplus D$ Odd Function Boolean Expressions

P1 Other Gates

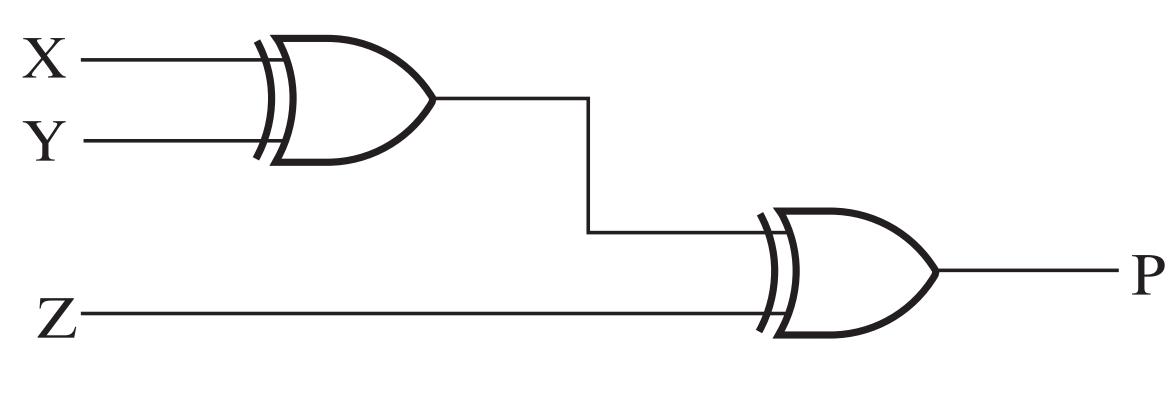

### (a) $P = X \oplus Y \oplus Z$

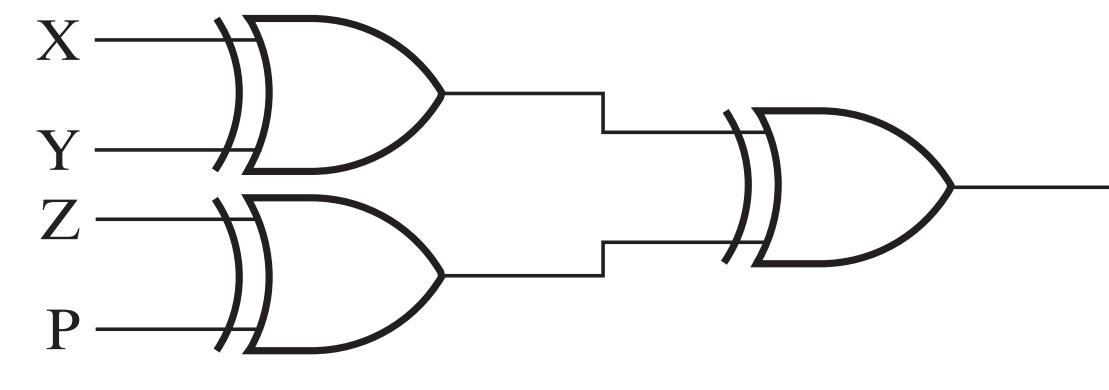

(b)  $C = X \oplus Y \oplus Z \oplus P$

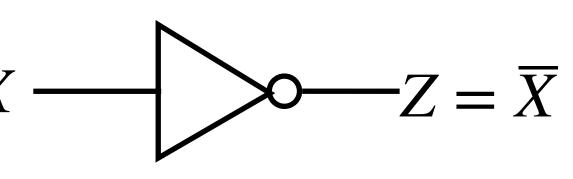

NOT Gate X —

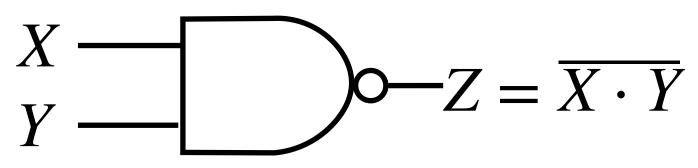

NAND Gate

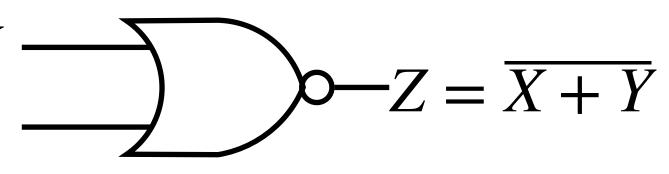

**NOR Gate**

X

**XNOR Gate**

X  $oldsymbol{V}$

**P1 Other Gates**

## N-Gates

• Delay: Remember the Definitions!

- Delay: Remember the Definitions!

- Gate Delay and Propagation Delay

- Delay: Remember the Definitions!

- Gate Delay and Propagation Delay

- Transport and Inertial Delays

- Delay: Remember the Definitions!

- Gate Delay and Propagation Delay

- Transport and Inertial Delays

- Standard Load

- Delay: Remember the Definitions!

- Gate Delay and Propagation Delay

- Transport and Inertial Delays

- Standard Load

- Other Gates: Remember the Definitions!

- Delay: Remember the Definitions!

- Gate Delay and Propagation Delay

- Transport and Inertial Delays

- Standard Load

- Other Gates: Remember the Definitions!

- XOR, Buffer, 3-State, NAND, NOR