# CSCI 150 Introduction to Digital and Computer System Design Lecture 5: Registers V

Jetic Gū

### Overview

- Focus: Fundamentals of Complex Digital Circuit Design

- Architecture: von Neumann

- Textbook v4: Ch7 7.6, 7.7; v5: Ch6 6.6, 6.7

- Core Ideas:

- 1. Register-Cell Design

- 2. Counter

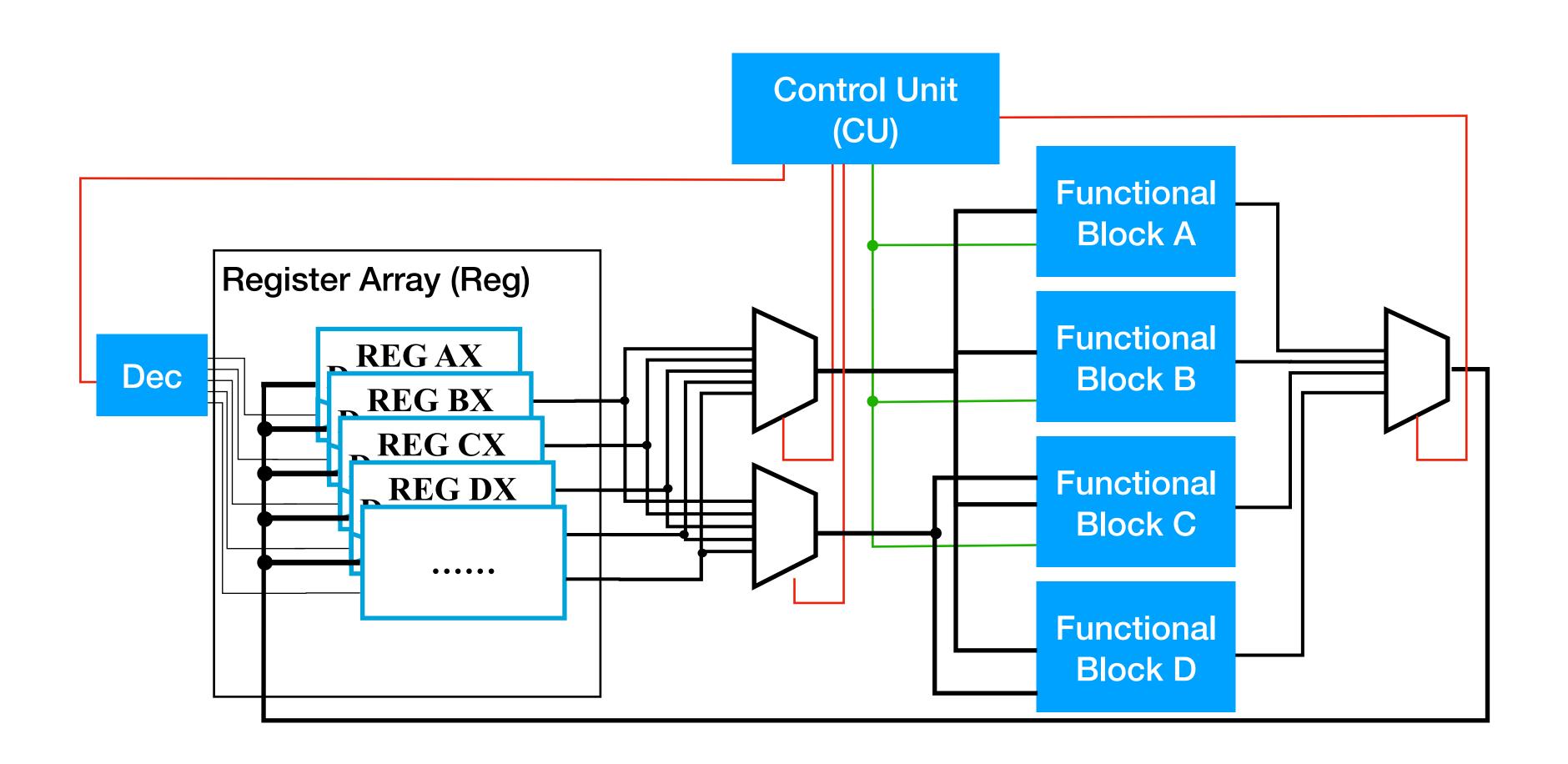

### Example Datapath Architecture

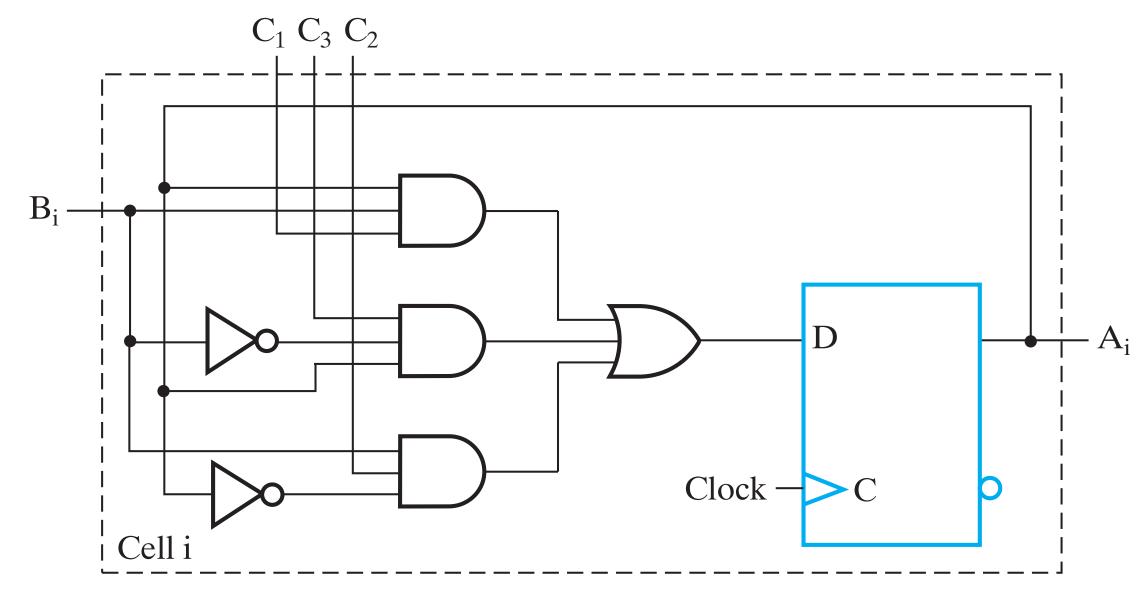

### Register Cell Design

One register for AND, OR, XOR

### 1. Specification

- Input: n-bit A, n-bit B

- Mode:  $M_{

m AND}$ ,  $M_{

m OR}$ ,  $M_{

m XOR}$ , only one of these can be 1. If all 0s preserve current value

- Output: n-bit output back to input register A ( $D_A$ )

- If  $M_{\mathrm{AND}} = 1$ ,  $D_A = A \cdot B$

- If  $M_{OR} = 1$ ,  $D_A = A + B$

- If  $M_{\text{XOR}} = 1$ ,  $D_A = A \oplus B$

- If  $M_{\rm AND} + M_{\rm OR} + M_{\rm XOR} = 0$ ,  $D_A = A$

P1 Register Cell

### 2. Formulation3. State Assignment

| Next A State (D <sub>A</sub> ) |                        |             |             |              |              |              |              |

|--------------------------------|------------------------|-------------|-------------|--------------|--------------|--------------|--------------|

| Present A State                | AND=0<br>XOR=0<br>OR=0 | OR=1<br>B=0 | OR=1<br>B=1 | AND=1<br>B=0 | AND=1<br>B=1 | XOR=1<br>B=0 | XOR=1<br>B=1 |

| 0                              | 0                      | 0           | 1           | 0            | 0            | 0            | 1            |

| 1                              | 1                      | 1           | 1           | 0            | 1            | 1            | 0            |

P1 Register Cell

### 4. Flip-Flop Input Equation5. Output Equation

$$D_{A} = M_{\text{AND}} \cdot (AB)$$

$$+ M_{\text{OR}} \cdot (A + B)$$

$$+ M_{\text{XOR}} \cdot (A\overline{B} + \overline{A}B)$$

$$+ \overline{M_{\text{OR}}} \cdot \overline{M_{\text{AND}}} \cdot \overline{M_{\text{XOR}}} \cdot A$$

### 6. Optimisation

$$\begin{split} D_{A} &= M_{\text{AND}} \cdot (AB) \\ &+ M_{\text{OR}} \cdot (A+B) \\ &+ M_{\text{XOR}} \cdot (A\overline{B} + \overline{A}B) \\ &+ \overline{M_{\text{OR}}} \cdot \overline{M_{\text{AND}}} \cdot \overline{M_{\text{XOR}}} \cdot A \end{split}$$

$$= M_{\text{AND}} \cdot \Sigma_{m}(3) \\ &+ M_{\text{OR}} \cdot \Sigma_{m}(1,2,3) \\ &+ M_{\text{XOR}} \cdot \Sigma_{m}(1,2) \\ &+ \overline{M_{\text{OR}}} \cdot \overline{M_{\text{AND}}} \cdot \overline{M_{\text{XOR}}} \cdot A \\ &+ \overline{M_{\text{OR}}} \cdot \overline{M_{\text{AND}}} \cdot \overline{M_{\text{XOR}}} \cdot \Sigma_{m}(2,3) \end{split}$$

### 6. Optimisation

• For every bit [0,n-1]

$$\begin{split} D_{A} &= M_{\text{AND}} \cdot (AB) \\ &+ M_{\text{OR}} \cdot (A+B) \\ &+ M_{\text{OR}} \cdot \Sigma_{m}(1,2,3) \\ &+ M_{\text{XOR}} \cdot (A\overline{B} + \overline{A}B) \\ &+ \overline{M}_{\text{OR}} \cdot \overline{M}_{\text{AND}} \cdot \overline{M}_{\text{XOR}} \cdot A \\ &+ \overline{M}_{\text{OR}} \cdot \overline{M}_{\text{AND}} \cdot \overline{M}_{\text{XOR}} \cdot \overline{M}_{\text{AND}} \cdot \overline{M}_{\text{XOR}} \cdot \Sigma_{m}(2,3) \\ &= m_{3}(M_{\text{AND}} + M_{\text{OR}} + \overline{M}_{\text{OR}} \cdot \overline{M}_{\text{AND}} \cdot \overline{M}_{\text{XOR}}) \\ &+ m_{2}(M_{\text{OR}} + M_{\text{XOR}} + \overline{M}_{\text{OR}} \cdot \overline{M}_{\text{AMD}} \cdot \overline{M}_{\text{XOR}}) \\ &+ m_{1}(M_{\text{OR}} + M_{\text{XOR}}) \end{split}$$

Siling

### 6. Optimisation

$$\begin{split} D_{A} &= M_{\text{AND}} \cdot (AB) \\ &+ M_{\text{OR}} \cdot (A+B) \\ &+ M_{\text{XOR}} \cdot (A\overline{B} + \overline{A}B) \\ &+ \overline{M_{\text{OR}}} \cdot \overline{M_{\text{AND}}} \cdot \overline{M_{\text{XOR}}} \cdot A \end{split}$$

$$= M_{\text{AND}} \cdot \Sigma_{m}(3) \\ &+ M_{\text{OR}} \cdot \Sigma_{m}(1,2,3) \\ &+ M_{\text{XOR}} \cdot \Sigma_{m}(1,2) \\ &+ \overline{M_{\text{OR}}} \cdot \overline{M_{\text{AND}}} \cdot \overline{M_{\text{XOR}}} \cdot A \\ &+ \overline{M_{\text{OR}}} \cdot \overline{M_{\text{AND}}} \cdot \overline{M_{\text{XOR}}} \cdot \Sigma_{m}(2,3) \end{split}$$

$$= m_3(M_{\text{AND}} + M_{\text{OR}} + \overline{M_{\text{XOR}}})$$

$$+ m_2(M_{\text{OR}} + M_{\text{XOR}} + \overline{M_{\text{AND}}})$$

$$+ m_1(M_{\text{OR}} + M_{\text{XOR}})$$

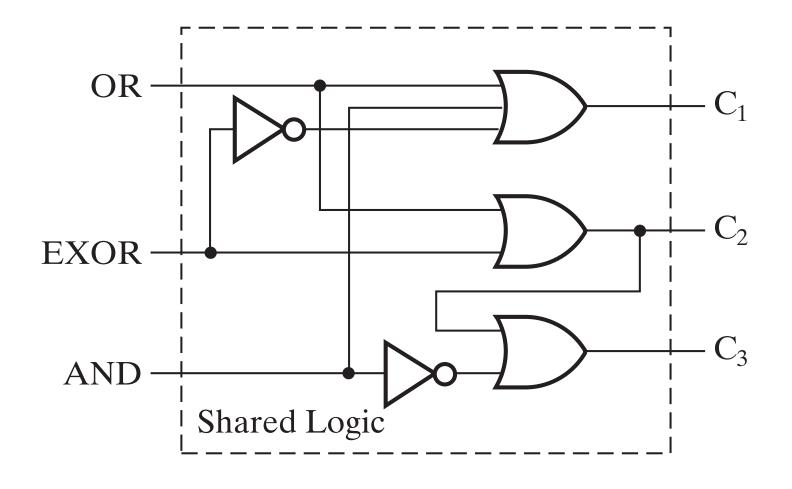

### 7. Technology Mapping

### Register Cells

- Register Cells are specific register designed to perform certain computation

- What we just did was for AND, OR, XOR

- Register Cell for AND, OR, XOR, and NOT

- Register Cell for AND, OR, XOR, NOT, and Shifts

- etc.

## Counter Functional Blocks

Ripple Counter; Synchronous Binary Counter; BCD Counter

### Counter

- Register Cells for counting

- Reset: set counter to 0

- Every CLK tick: add 1 to the register

- 1. Ripple Counter

- 2. Synchronous Counters

- 3. BCD Counter

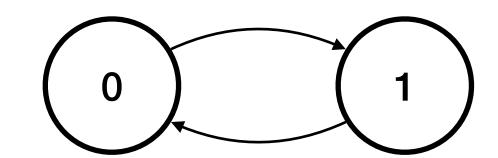

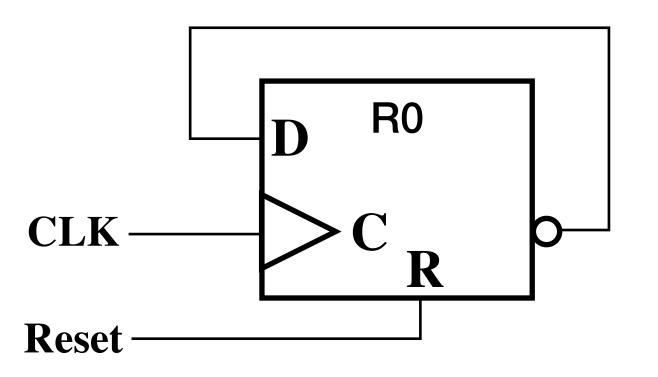

### Ripple Counter

- 1-bit Counter

- What is the behaviour of the circuit on the right?

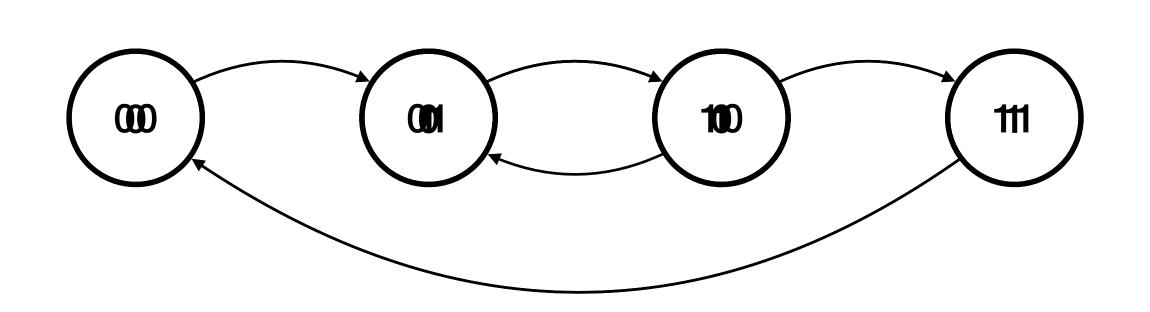

### Ripple Counter

- 2-bit Counter

- What is the behaviour of the circuit on the right?

Color

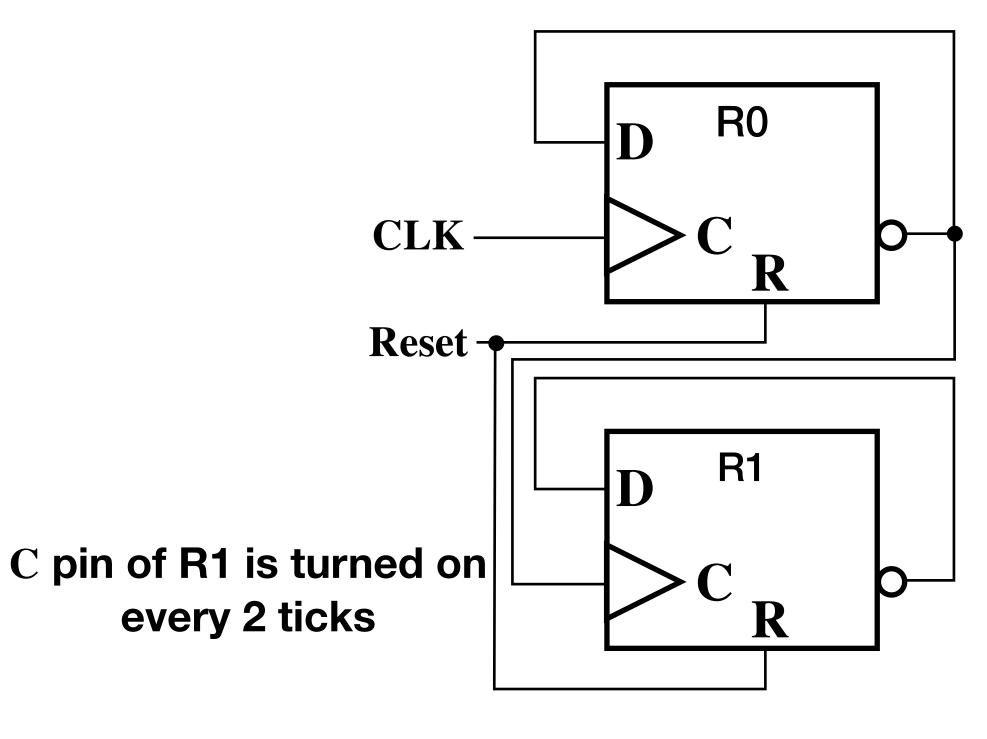

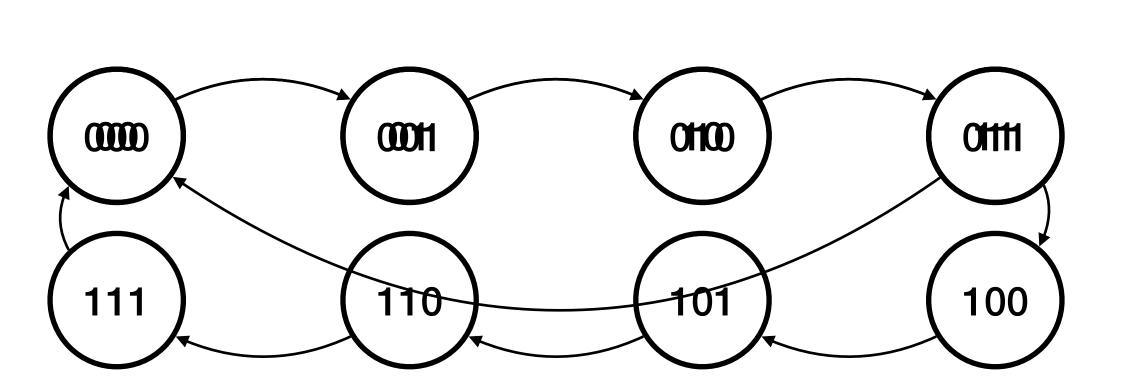

### Ripple Counter

What is the behaviour of the circuit on the right?

C pin of R1 is turned on every 2 ticks

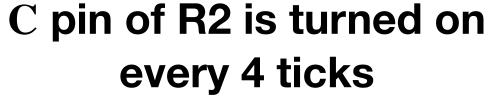

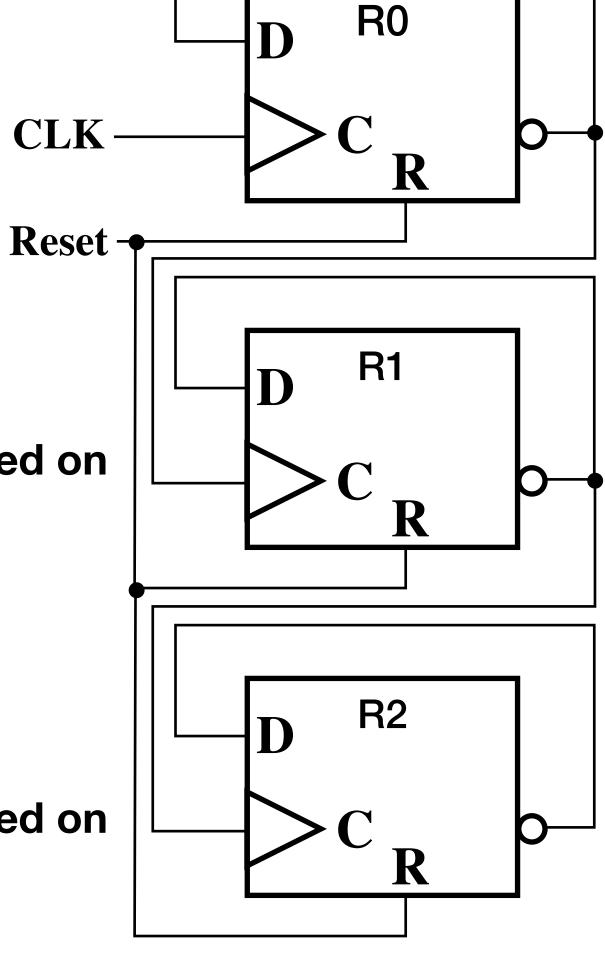

### Ripple Counter CLK

C pin of R1 is turned on every 2 ticks

• 4-bit Counter

What is the behaviour of the circuit on the right?

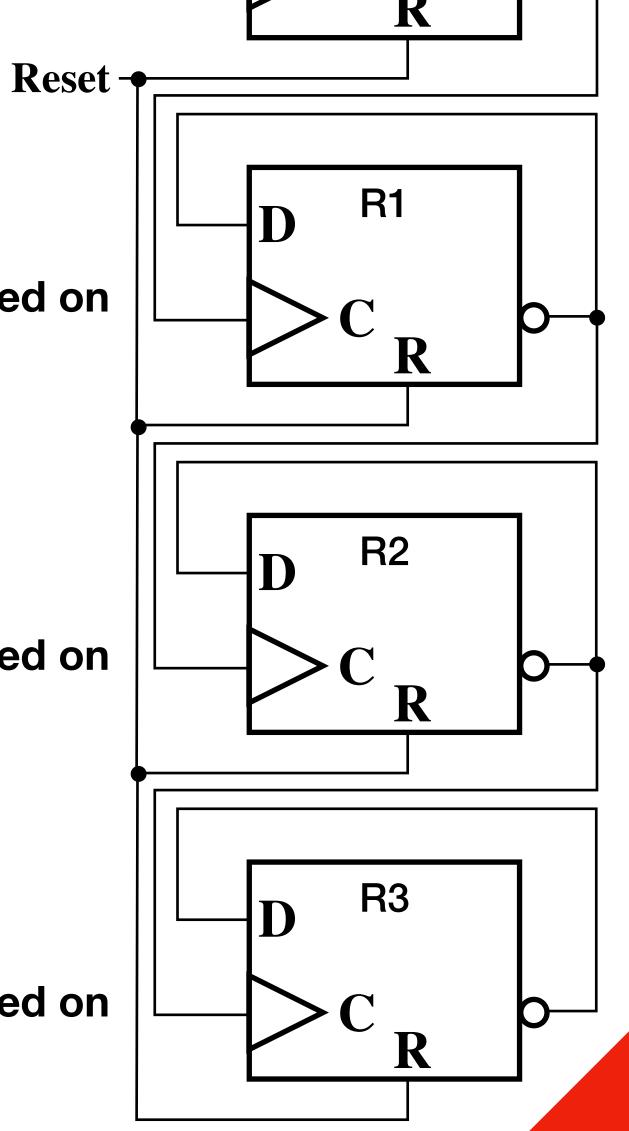

C pin of R2 is turned on every 4 ticks

C pin of R3 is turned on every 8 ticks

R0

### Synchronous Binary Counter

| Upward Counting Sequence |       |                | <b>Downward Counting Sequence</b> |       |       |                |         |

|--------------------------|-------|----------------|-----------------------------------|-------|-------|----------------|---------|

| $Q_3$                    | $Q_2$ | Q <sub>1</sub> | $Q_0$                             | $Q_3$ | $Q_2$ | Q <sub>1</sub> | $Q_{0}$ |

| 0                        | 0     | 0              | 0                                 | 1     | 1     | 1              | 1       |

| 0                        | 0     | 0              | 1                                 | 1     | 1     | 1              | 0       |

| 0                        | 0     | 1              | 0                                 | 1     | 1     | 0              | 1       |

| 0                        | 0     | 1              | 1                                 | 1     | 1     | 0              | 0       |

| 0                        | 1     | 0              | 0                                 | 1     | 0     | 1              | 1       |

| 0                        | 1     | 0              | 1                                 | 1     | 0     | 1              | 0       |

| 0                        | 1     | 1              | 0                                 | 1     | 0     | 0              | 1       |

| 0                        | 1     | 1              | 1                                 | 1     | 0     | 0              | 0       |

| 1                        | 0     | 0              | 0                                 | 0     | 1     | 1              | 1       |

| 1                        | 0     | 0              | 1                                 | 0     | 1     | 1              | 0       |

| 1                        | 0     | 1              | 0                                 | 0     | 1     | 0              | 1       |

| 1                        | 0     | 1              | 1                                 | 0     | 1     | 0              | 0       |

| 1                        | 1     | 0              | 0                                 | 0     | 0     | 1              | 1       |

| 1                        | 1     | 0              | 1                                 | 0     | 0     | 1              | 0       |

| 1                        | 1     | 1              | 0                                 | 0     | 0     | 0              | 1       |

| 1                        | 1     | 1              | 1                                 | 0     | 0     | 0              | 0       |

### Synchronous Binary Counter

| Upward Counting Sequence |          |          | Downward Counting Sequence |       |       |          |                     |

|--------------------------|----------|----------|----------------------------|-------|-------|----------|---------------------|

| $Q_3$                    | $Q_{_2}$ | $Q_{_1}$ | $\mathbf{Q}_{_{0}}$        | $Q_3$ | $Q_2$ | $Q_{_1}$ | $\mathbf{Q}_{_{0}}$ |

| 0                        | 0        | 0        | 0                          | 1     | 1     | 1        | 1                   |

| 0                        | 0        | 0        | 1                          | 1     | 1     | 1        | 0                   |

| 0                        | 0        | 1        | 0                          | 1     | 1     | 0        | 1                   |

| 0                        | 0        | 1        | 1                          | 1     | 1     | 0        | 0                   |

| 0                        | 1        | 0        | 0                          | 1     | 0     | 1        | 1                   |

| 0                        | 1        | 0        | 1                          | 1     | 0     | 1        | 0                   |

| 0                        | 1        | 1        | 0                          | 1     | 0     | 0        | 1                   |

| 0                        | 1        | 1        | 1                          | 1     | 0     | 0        | 0                   |

| 1                        | 0        | 0        | 0                          | 0     | 1     | 1        | 1                   |

| 1                        | 0        | 0        | 1                          | 0     | 1     | 1        | 0                   |

| 1                        | 0        | 1        | 0                          | 0     | 1     | 0        | 1                   |

| 1                        | 0        | 1        | 1                          | 0     | 1     | 0        | 0                   |

| 1                        | 1        | 0        | 0                          | 0     | 0     | 1        | 1                   |

| 1                        | 1        | 0        | 1                          | 0     | 0     | 1        | 0                   |

| 1                        | 1        | 1        | 0                          | 0     | 0     | 0        | 1                   |

| 1                        | 1        | 1        | 1                          | 0     | 0     | 0        | 0                   |

• Upward  $Q_i$  flips when

; Downward equals

### Synchronous Binary Counter

- Upward

- $D_{A0} = \overline{Q_0}$

- $D_{Ai} = Q_i \oplus (\Pi_{i < i}Q_i)$ , for all  $i \in [1, n-1]$

- Downward

- Take  $Q_i$  as output (using e.g. multiplexer), for all  $i \in [0, n-1]$

#### Exercise

- Implement 4-bit Ripple Counter in LogicWorks

- Implement 4-bit Synchronous Counter in LogicWorks

- Design 3 digit BCD counter using 4-bit binary counters

### Tutoria

Bus, Register Cells, Datapath