# CSCI 150 Introduction to Digital and Computer System Design Lecture 4: Sequential Circuit III

Jetic Gū

#### Overview

- Focus: Basic Information Retaining Blocks

- Architecture: Sequential Circuit

- Textbook v4: Ch5 5.3, 5.4; v5: Ch4 4.2 4.3

- Core Ideas:

- 1. Latches and Flip-Flops (with Direct Input)

- 2. Sequential Circuit Analysis

P0 Review

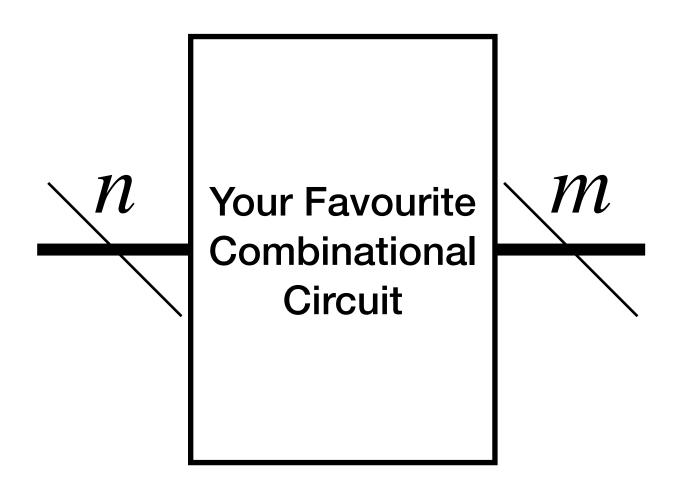

### Combinational Logic Circuit Design

- Design Principles

- Knows: fixed-Length input and output

- Knows: input/output mapping relations

- Optimisation: Minimise overall delay

P0 Review

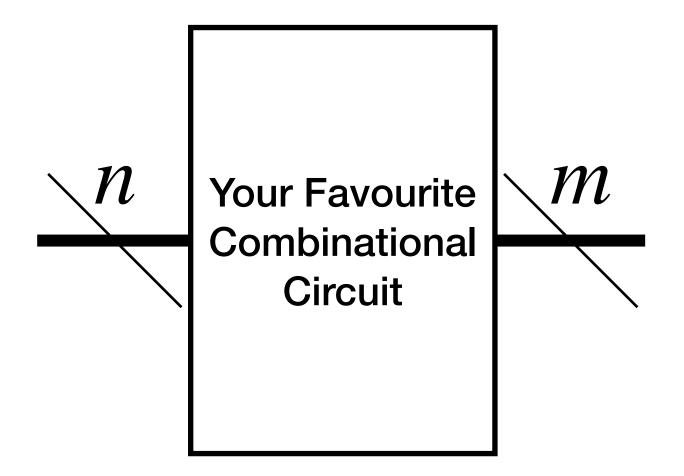

### Combinational Logic Circuit Design

- Cannot handle variable length input

- Cannot store information

- Cannot perform multi-step tasks

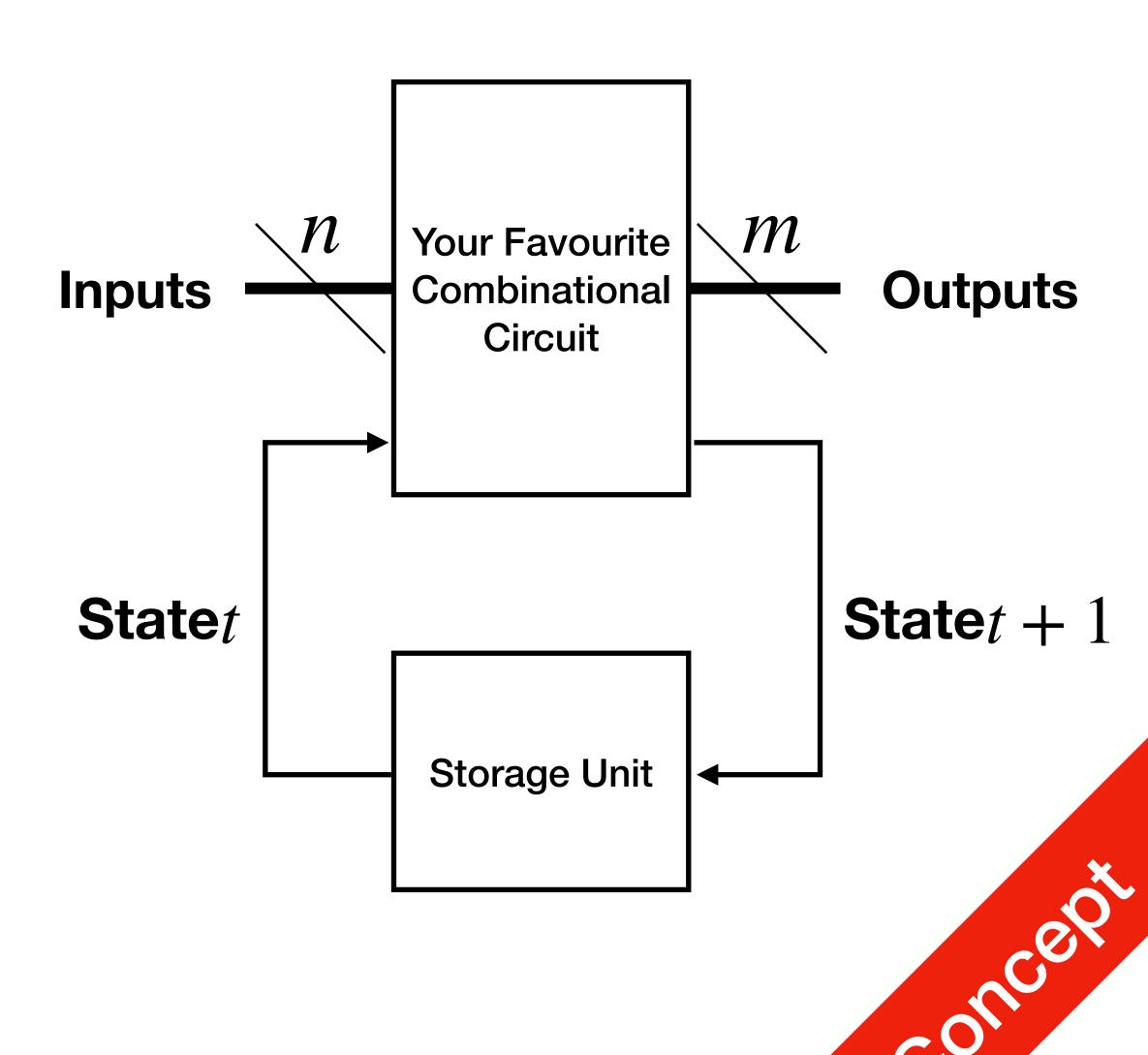

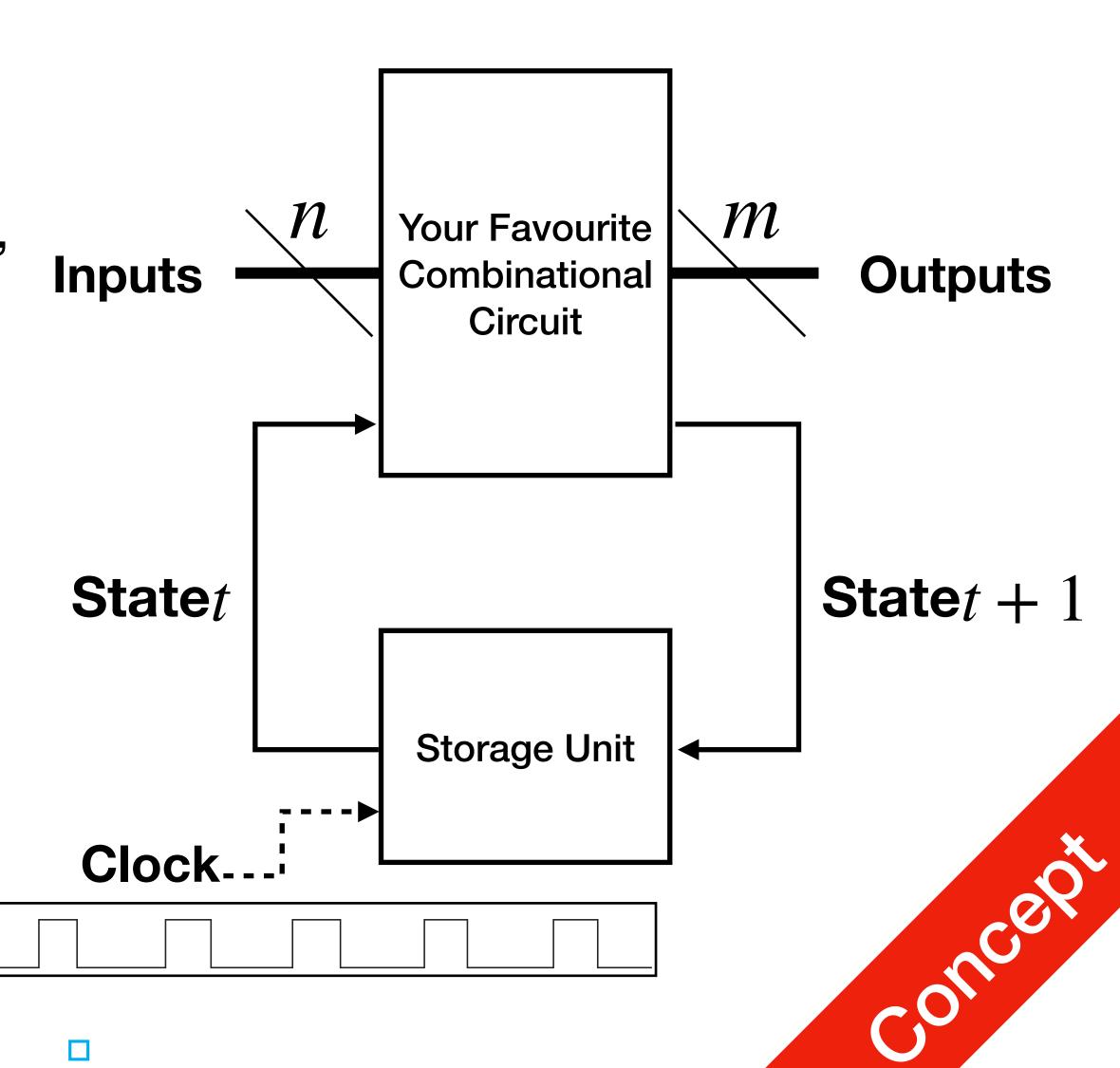

#### Definitions

- 1. Storage Elements circuits that can store binary information

- 2. **State** partial results, instructions, etc.

- 3. Synchronous Sequential Circuit

Signals arrive at discrete instants of time,

outputs at next time step

- 4. Asynchronous Sequential Circuit

Signals arrive at any instant of time,

outputs when ready

#### Definitions

- 3. Synchronous Sequential Circuit

Signals arrive at discrete instants of time,

outputs at next time step

- Has Clock

- 4. Asynchronous Sequential Circuit

Signals arrive at any instant of time,

outputs when ready

- May not have Clock

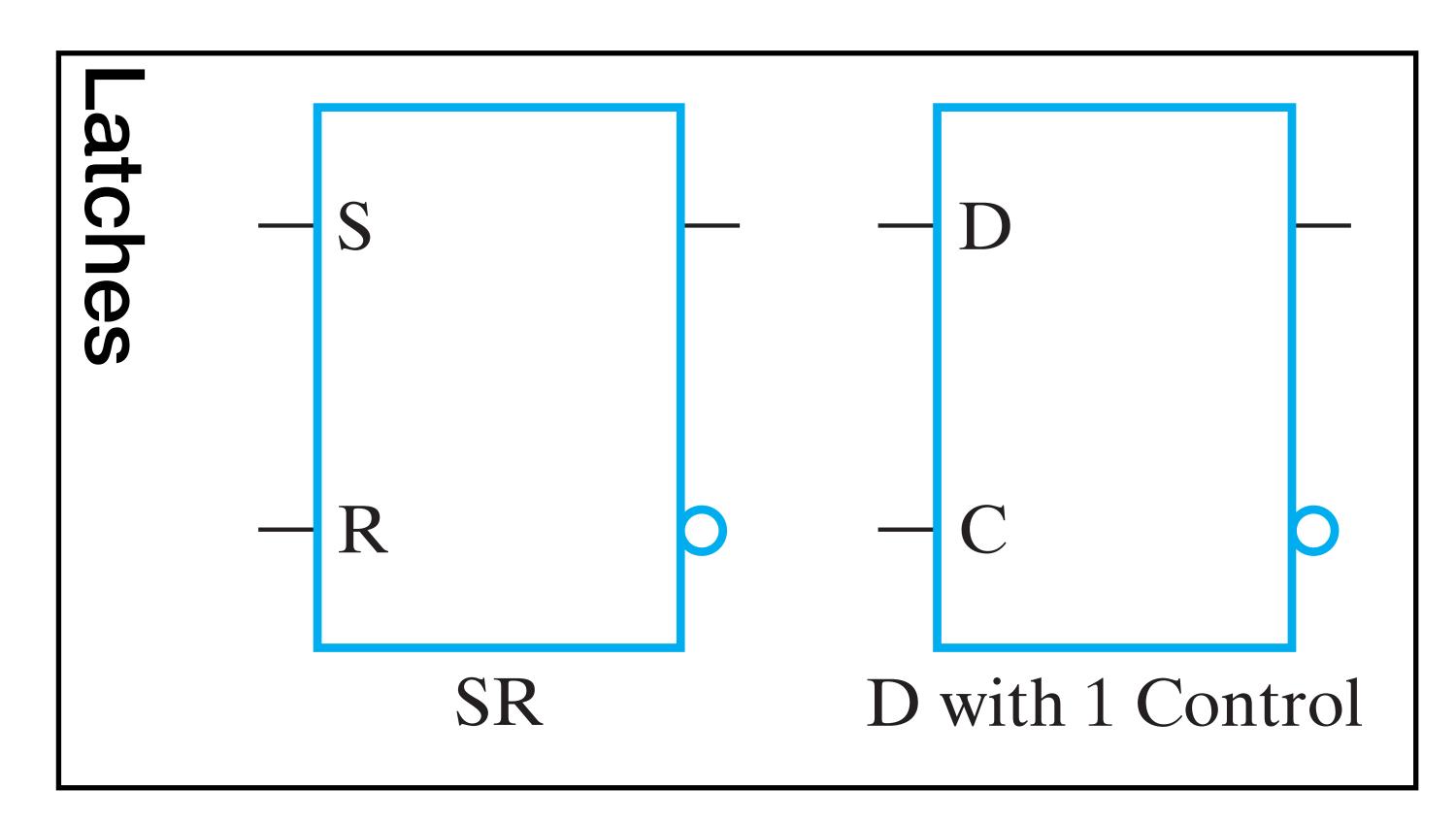

### Review: Latches and Flip-Flops

SR Latches, D Latches, D Flip-Flops

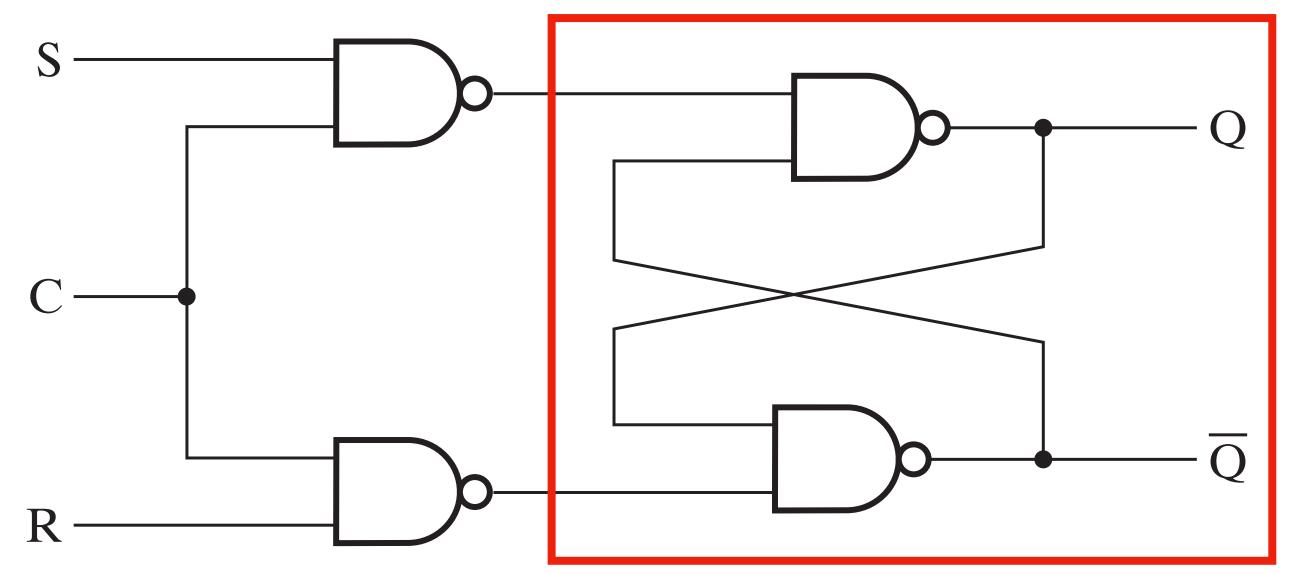

### SR Latch with Control Input

| C S R | Next state of Q    |

|-------|--------------------|

| 0 X X | No change          |

| 1 0 0 | No change          |

| 1 0 1 | Q = 0; Reset state |

| 1 1 0 | Q = 1; Set state   |

| 1 1 1 | Undefined          |

- Implemented using  $\overline{SR}$  latches

- C acts as an enabler; otherwise the entire circuit functions as an SR latch

P1 Flip-Flops

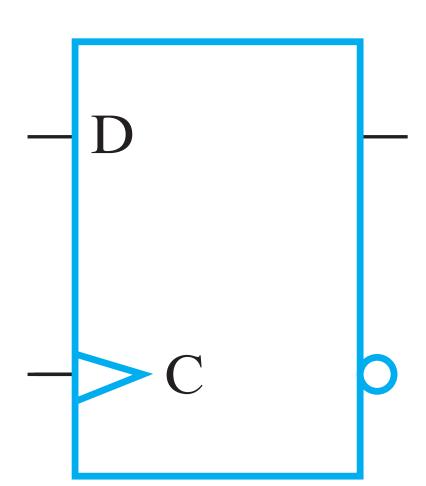

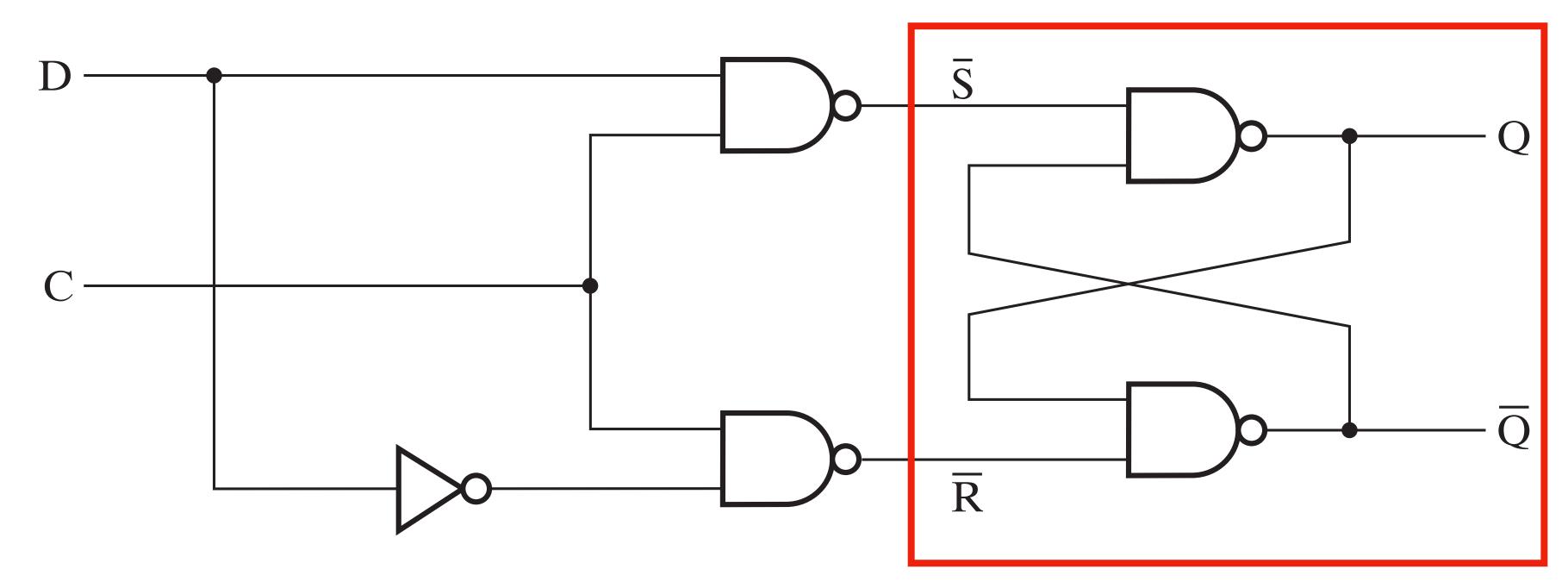

#### D Latch

| C | D | Next state of Q    |

|---|---|--------------------|

| 0 | X | No change          |

| 1 | 0 | Q = 0; Reset state |

| 1 | 1 | Q = 1; Set state   |

- Implemented using  $\overline{SR}$  latches

- C: Signals changes to the stored states; D the value to change to  $S\overline{R}$

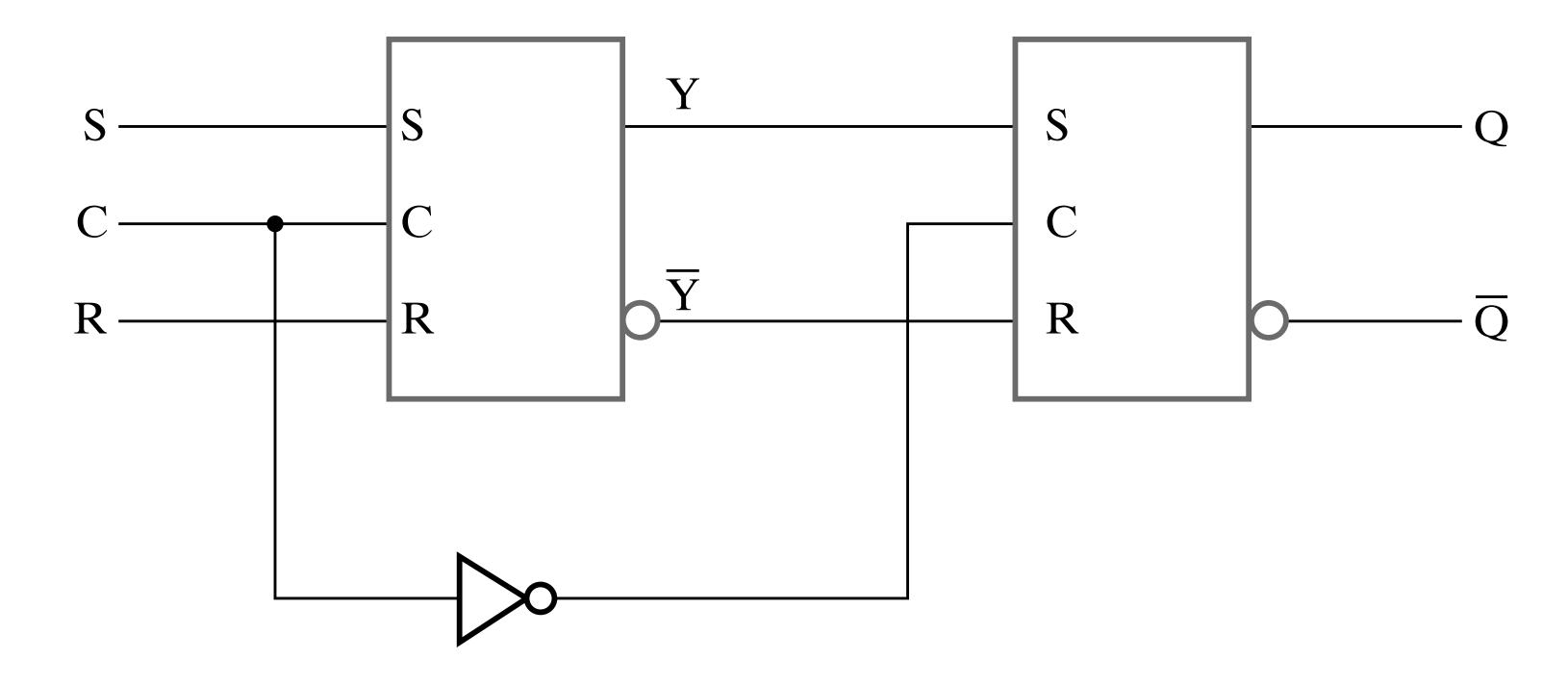

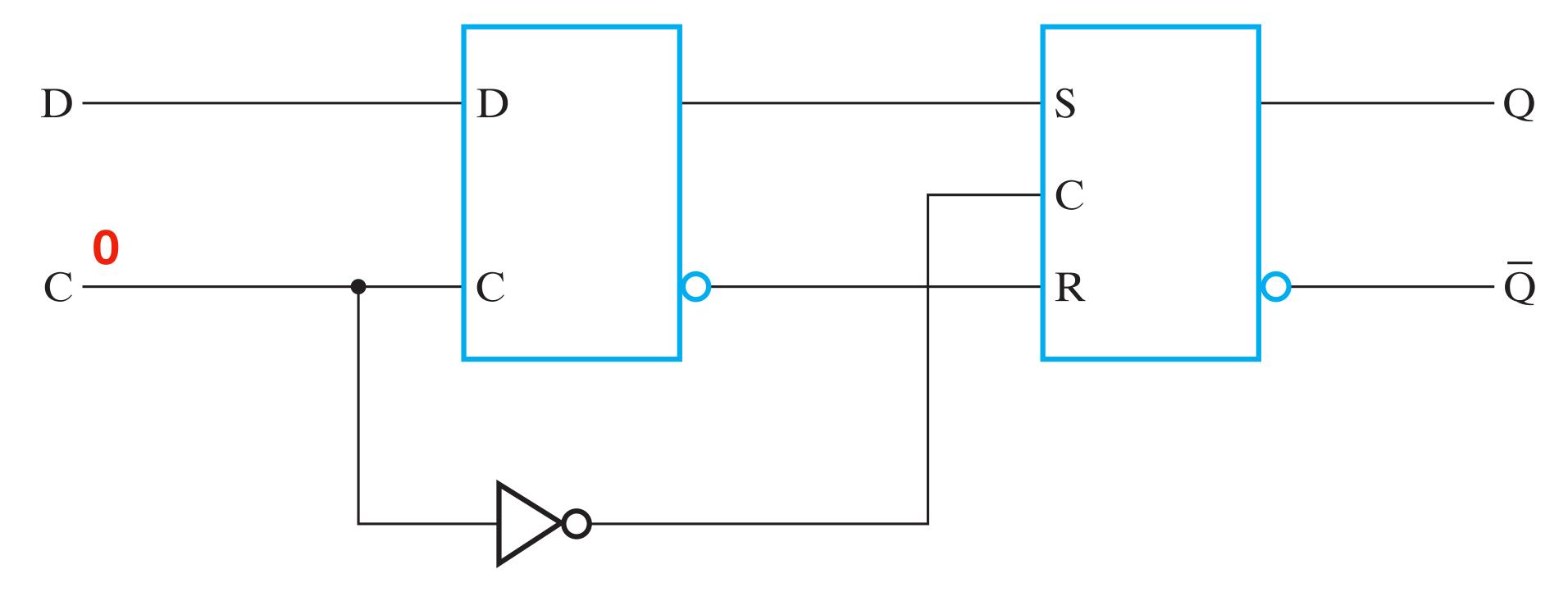

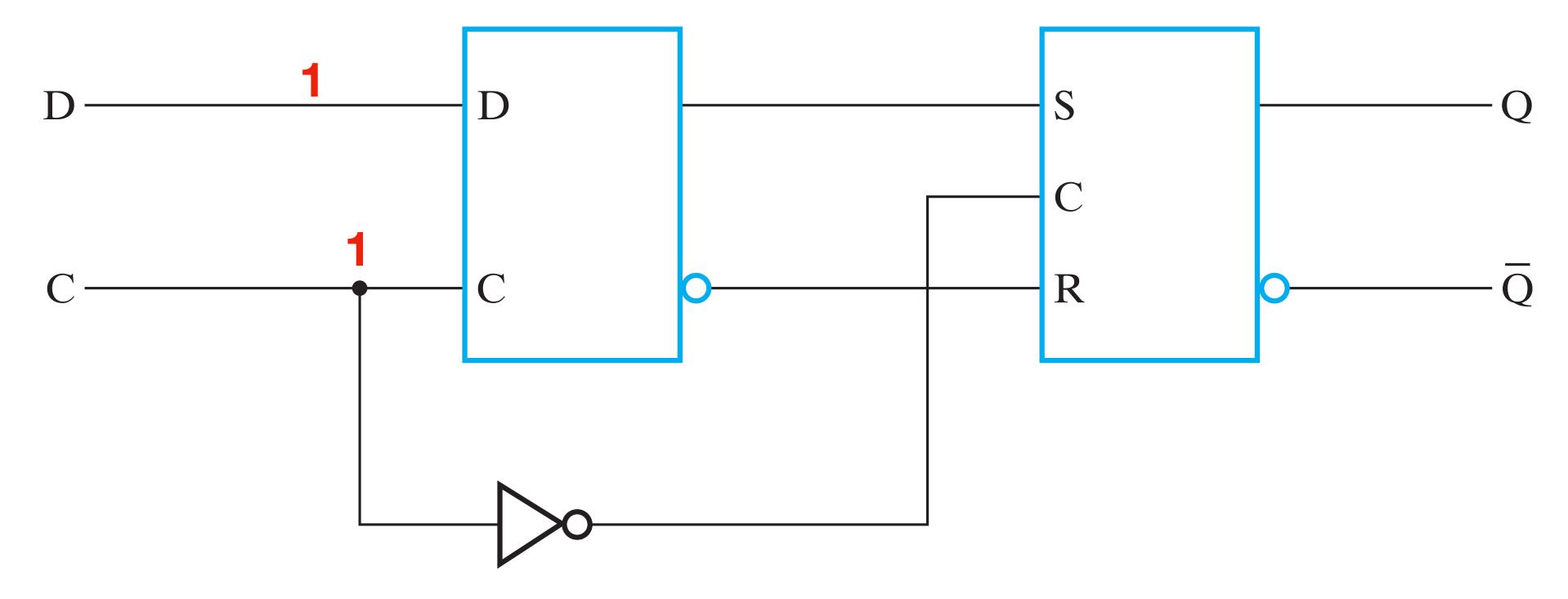

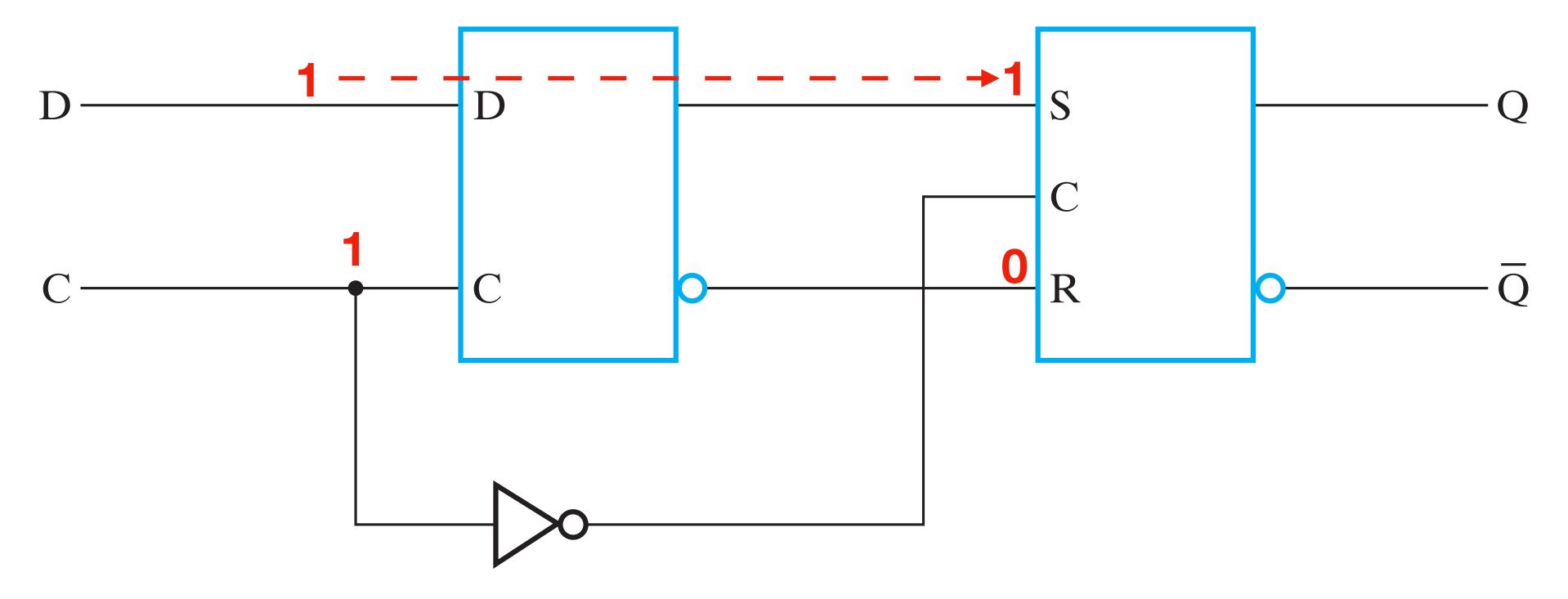

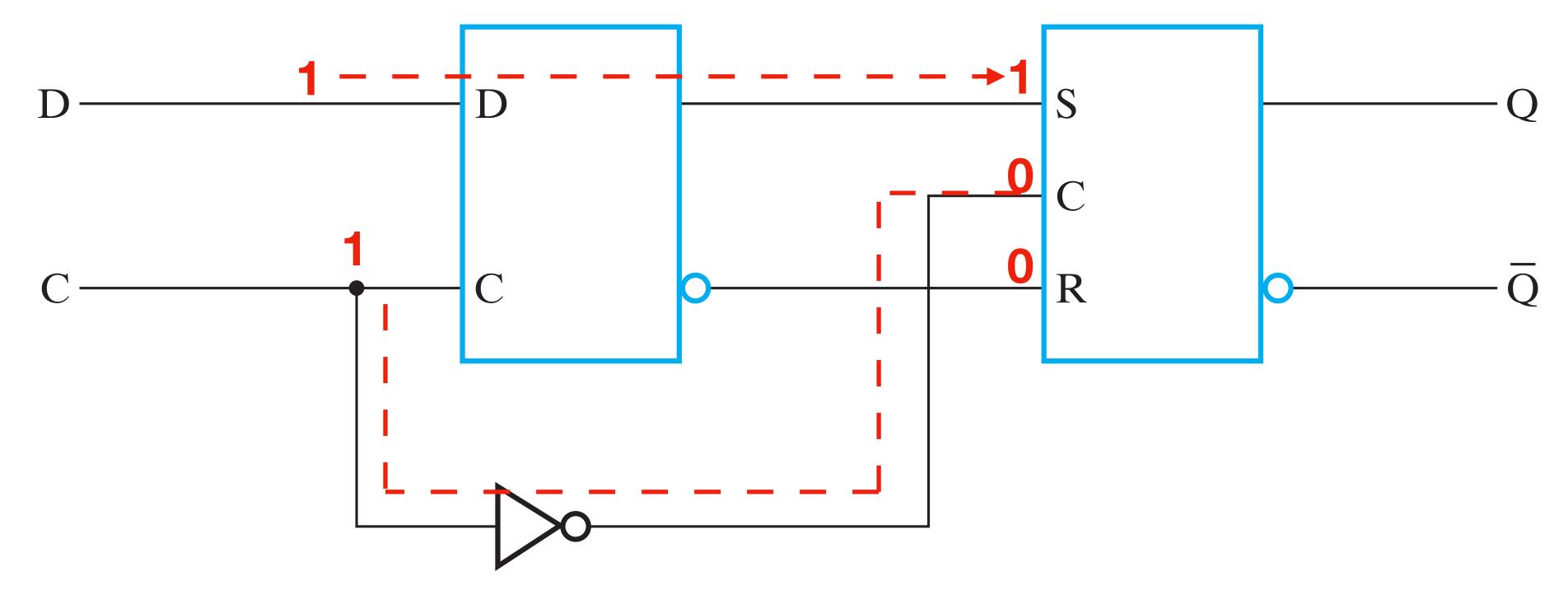

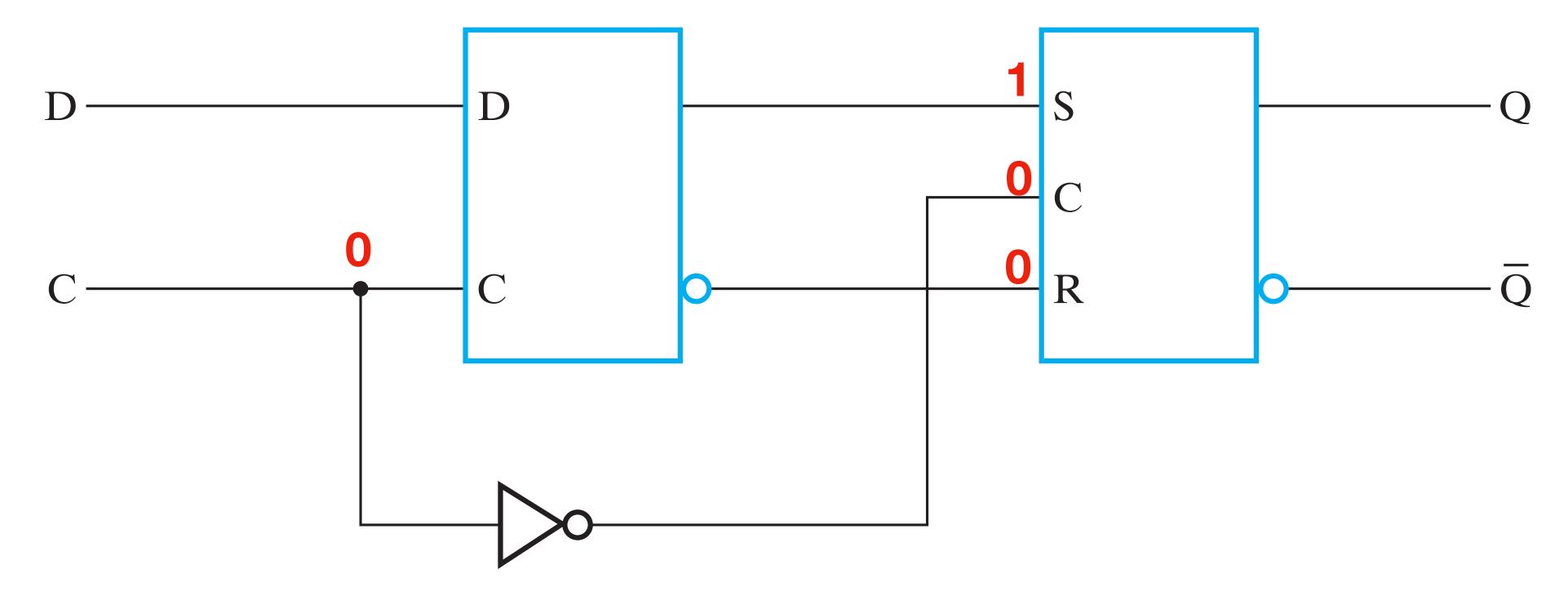

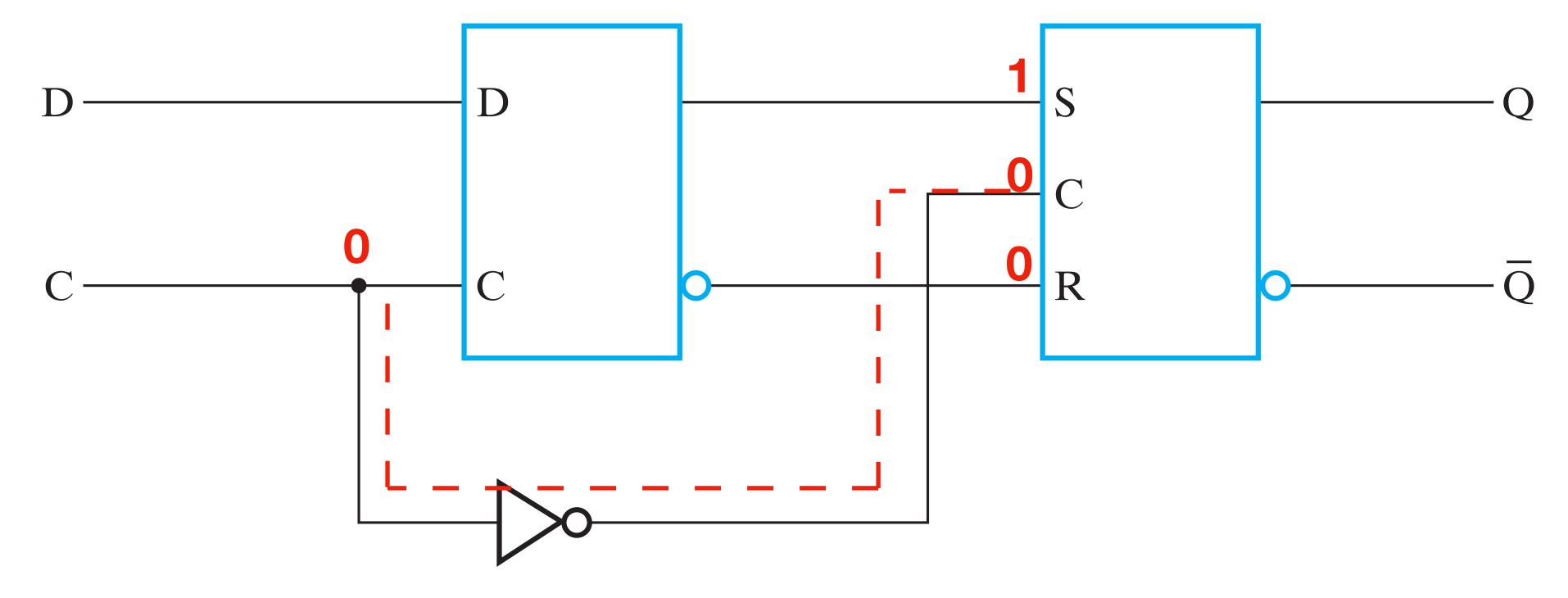

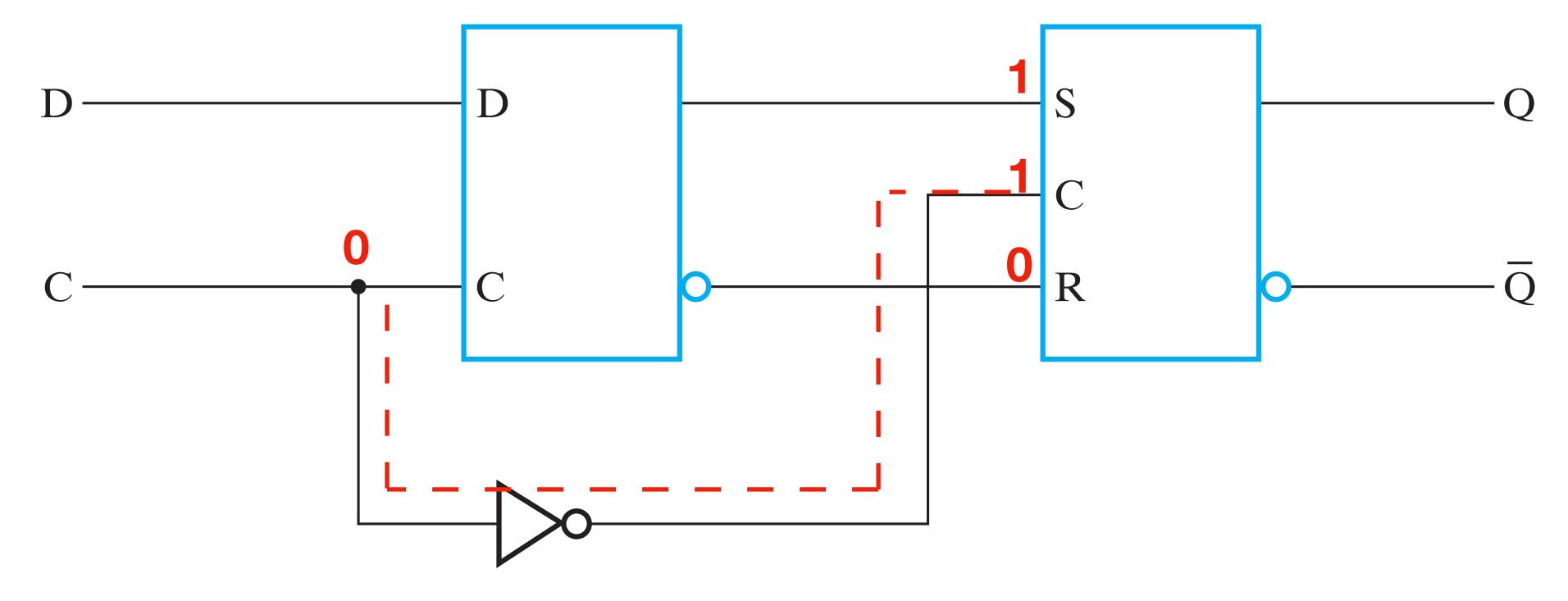

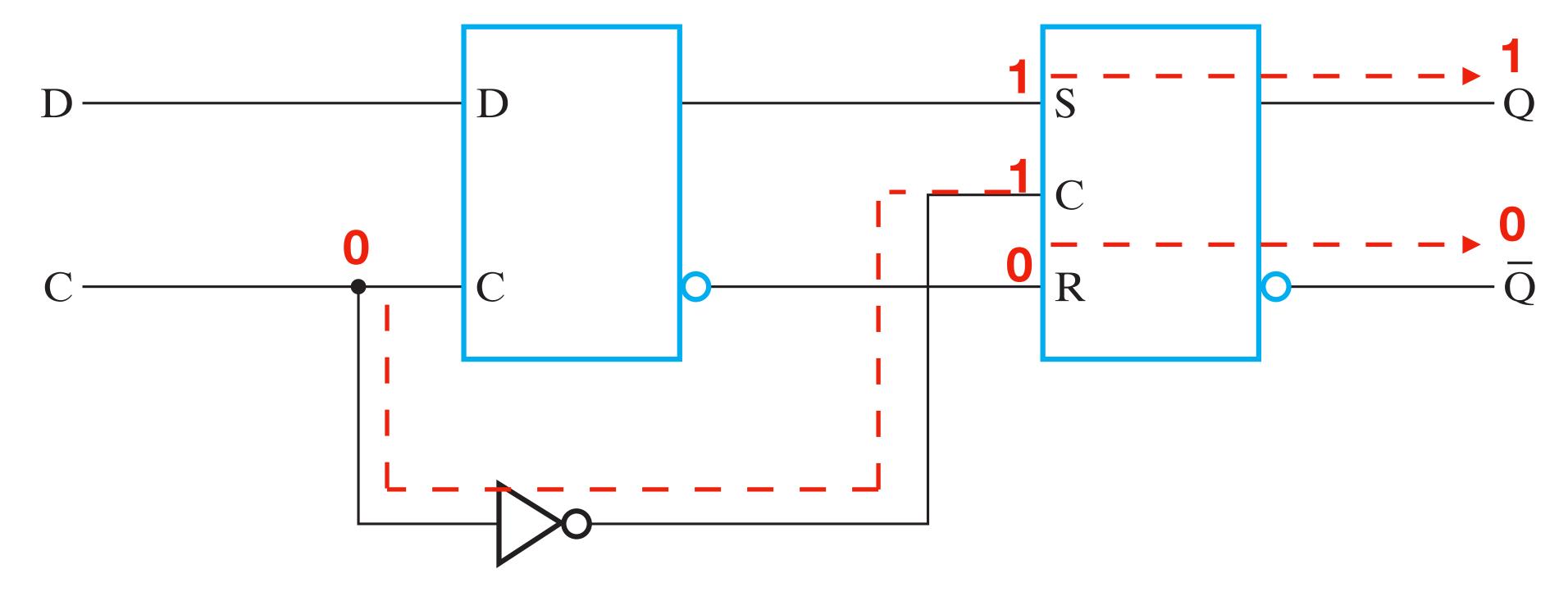

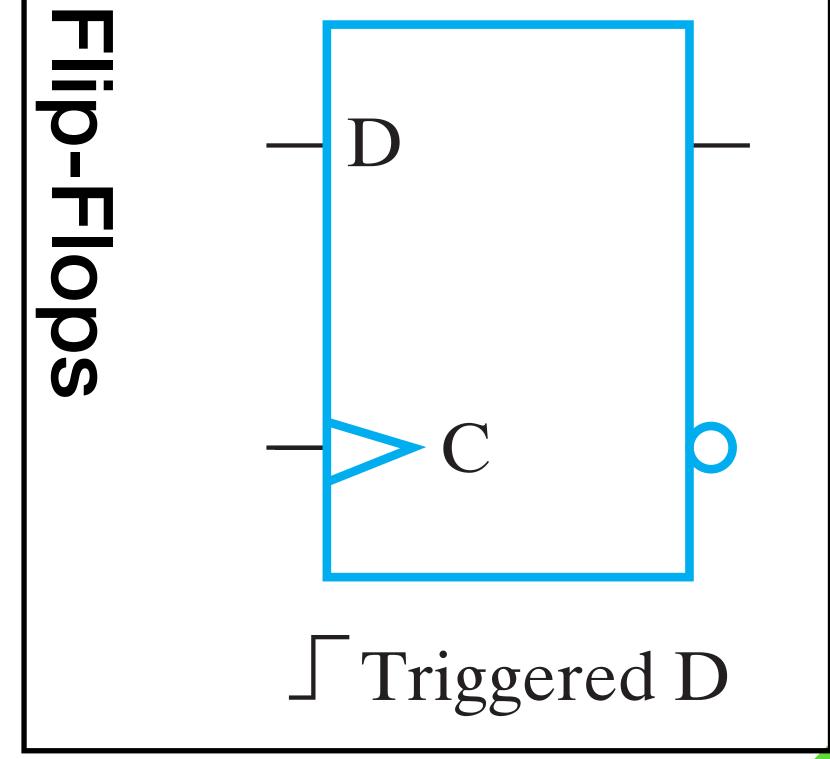

#### Flip-Flops

- Latches are Transparent

input can be seen from outputs while control pulse is 1

- Flip-Flops are not Transparent

Output state changes require changes of control signal

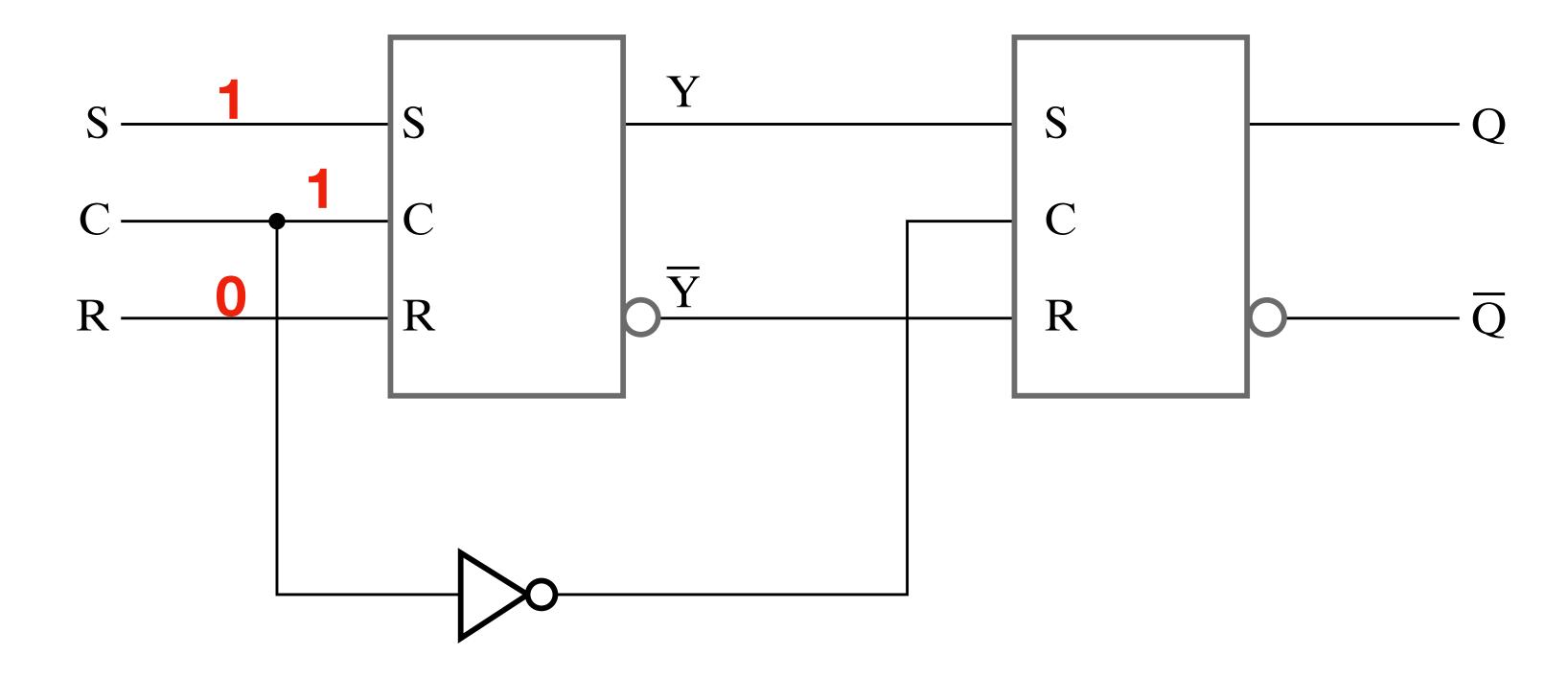

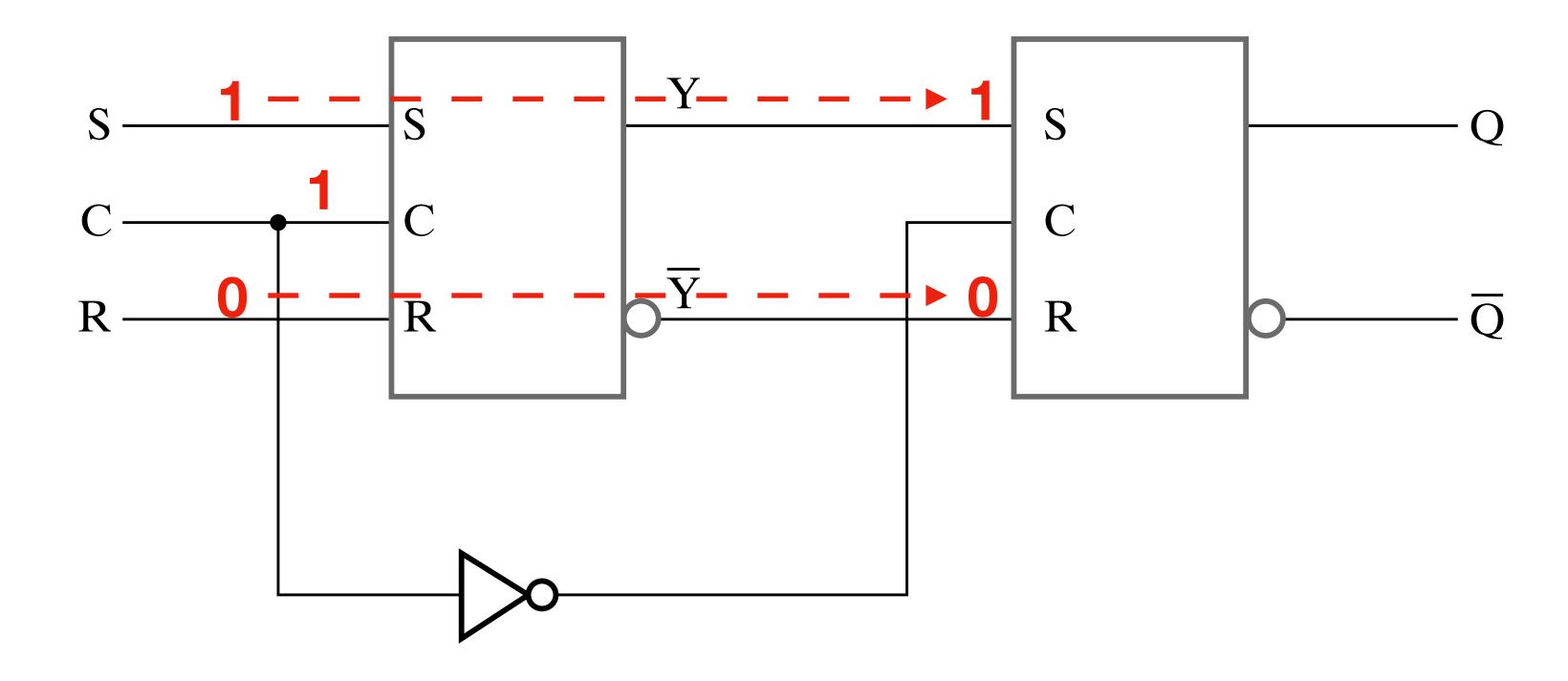

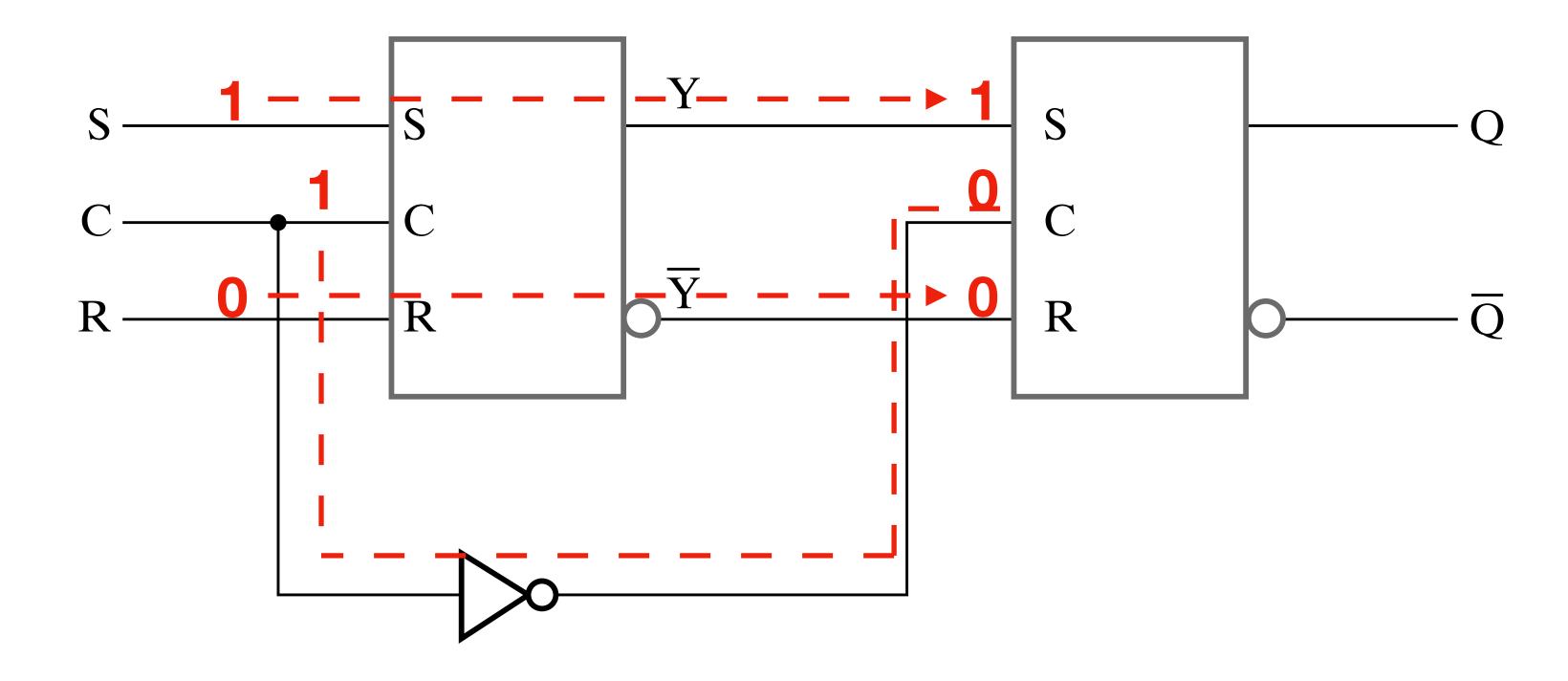

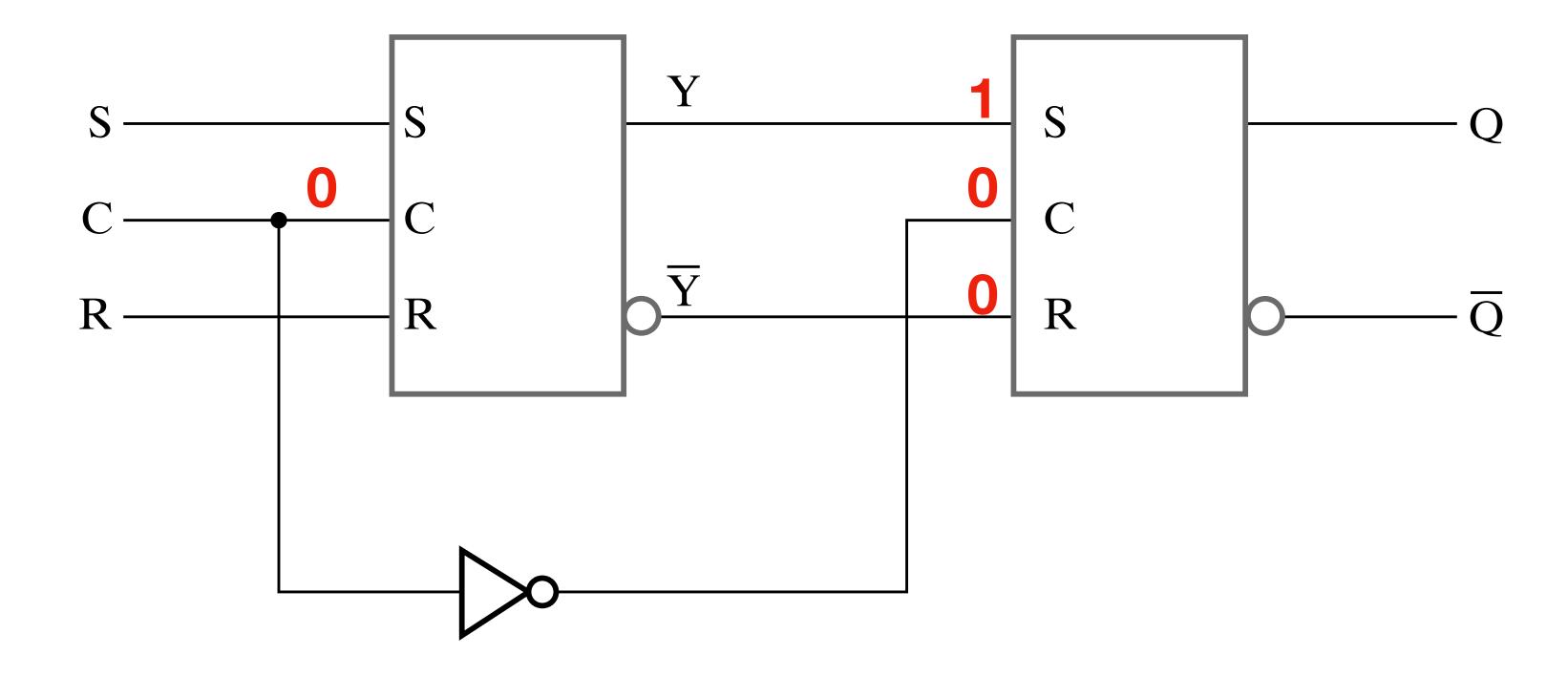

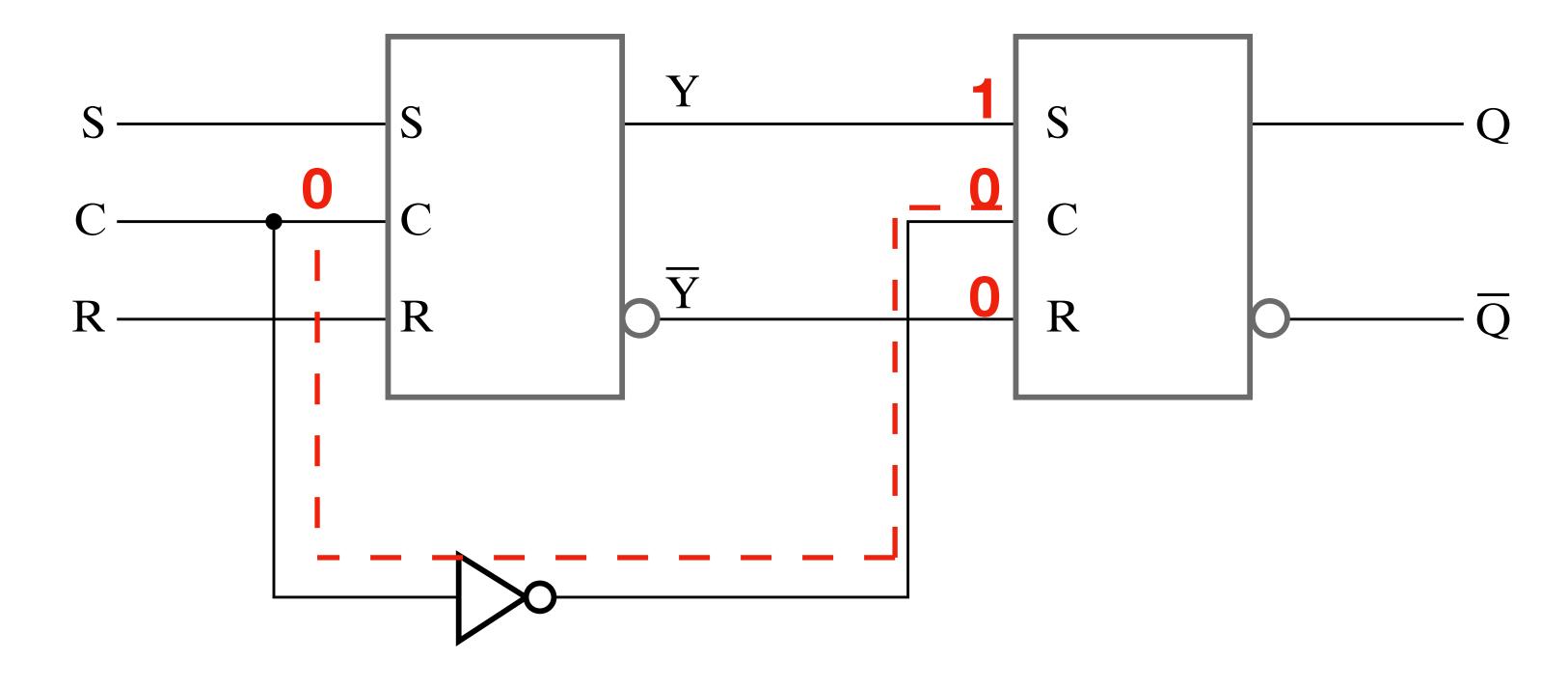

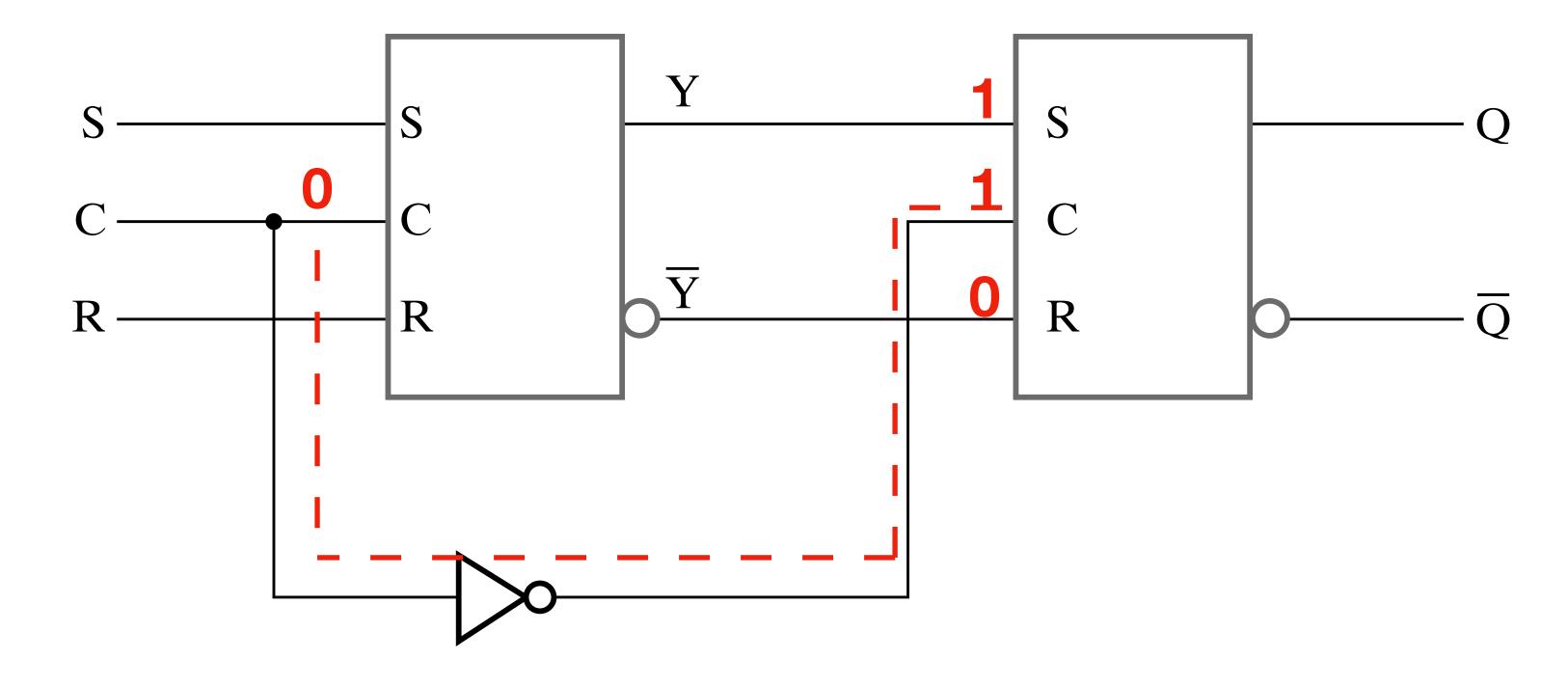

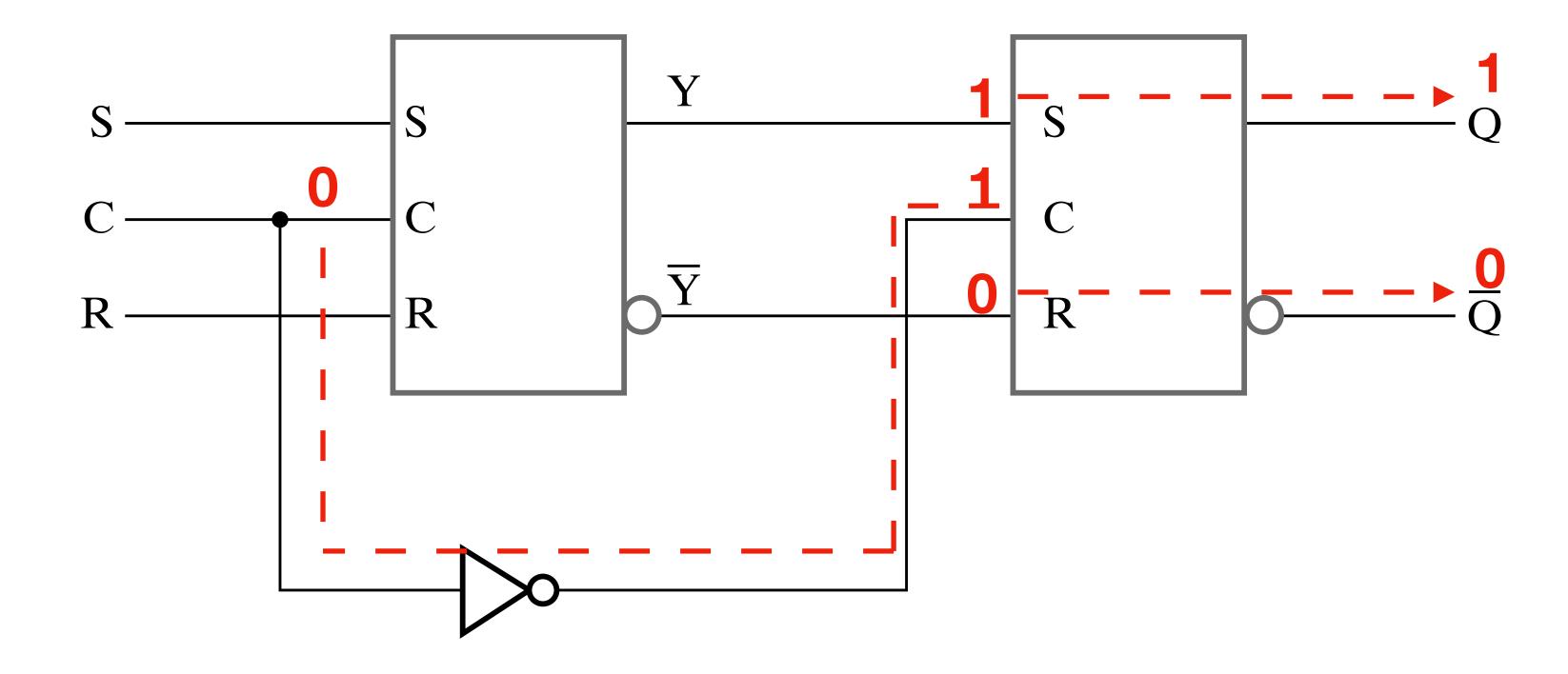

- Constructed using SR latches, left Master, right Slave

- Output state changes require  $C=0 \rightarrow C=1 \rightarrow C=0$  (Positive Pulse)

- Constructed using SR latches, left Master, right Slave

- Output state changes require  $C=0 \rightarrow C=1 \rightarrow C=0$  (Positive Pulse)

- Constructed using SR latches, left Master, right Slave

- Output state changes require  $C=0 \rightarrow C=1 \rightarrow C=0$  (Positive Pulse)

- Constructed using SR latches, left Master, right Slave

- Output state changes require  $C=0 \rightarrow C=1 \rightarrow C=0$  (Positive Pulse)

- Constructed using SR latches, left Master, right Slave

- Output state changes require  $C=0 \rightarrow C=1 \rightarrow C=0$  (Positive Pulse)

- Constructed using SR latches, left Master, right Slave

- Output state changes require  $C=0 \rightarrow C=1 \rightarrow C=0$  (Positive Pulse)

- Constructed using SR latches, left Master, right Slave

- Output state changes require  $C=0 \rightarrow C=1 \rightarrow C=0$  (Positive Pulse)

- Constructed using SR latches, left Master, right Slave

- Output state changes require  $C=0 \rightarrow C=1 \rightarrow C=0$  (Positive Pulse)

- Constructed using SR latches, left Master, right Slave

- Output state changes require  $C=0 \rightarrow C=1 \rightarrow C=0$  (Positive Pulse)

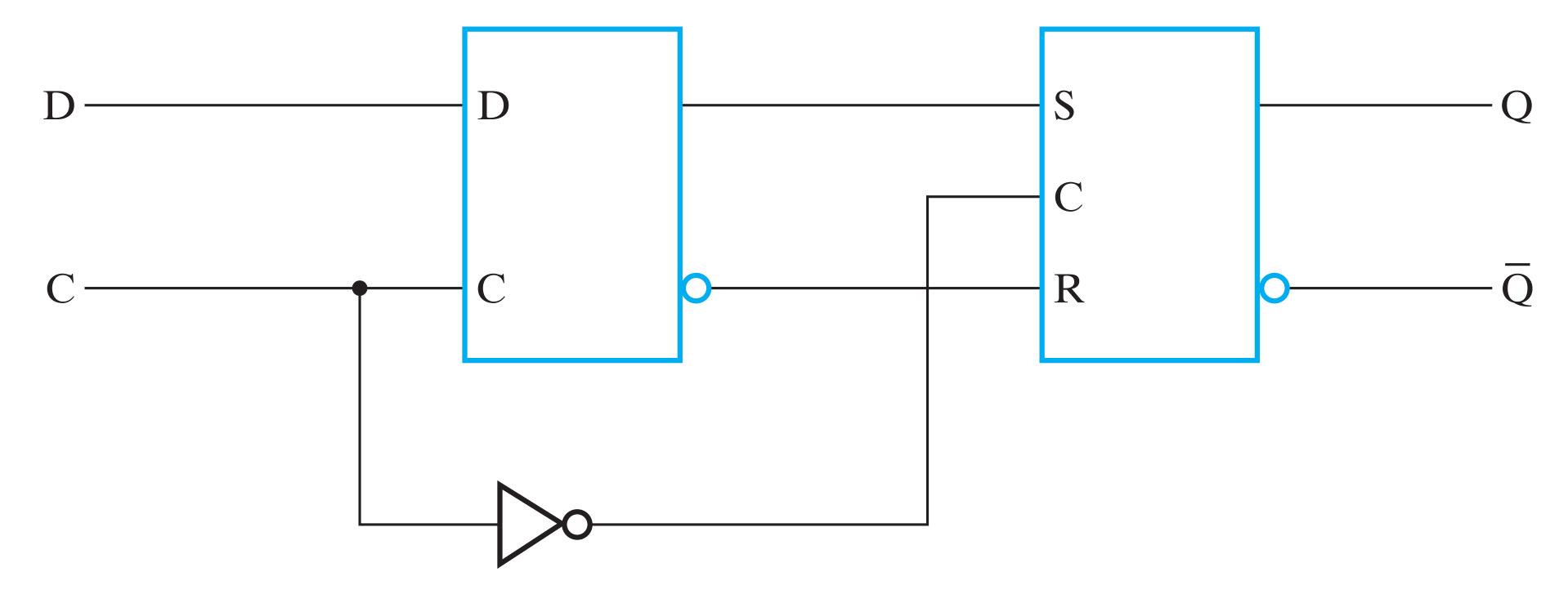

- ullet Replaces SR master in SR Master-Slave with D master Latch

- Negative Edge Triggered D (Flip-Flop):  $C=1 \rightarrow C=0$

- ullet Replaces SR master in SR Master-Slave with D master Latch

- Negative Edge Triggered D (Flip-Flop):  $C=1 \rightarrow C=0$

- ullet Replaces SR master in SR Master-Slave with D master Latch

- Negative Edge Triggered D (Flip-Flop):  $C=1 \rightarrow C=0$

- ullet Replaces SR master in SR Master-Slave with D master Latch

- Negative Edge Triggered D (Flip-Flop):  $C=1 \rightarrow C=0$

- ullet Replaces SR master in SR Master-Slave with D master Latch

- Negative Edge Triggered D (Flip-Flop):  $C=1 \rightarrow C=0$

- ullet Replaces SR master in SR Master-Slave with D master Latch

- Negative Edge Triggered D (Flip-Flop):  $C=1 \rightarrow C=0$

- ullet Replaces SR master in SR Master-Slave with D master Latch

- Negative Edge Triggered D (Flip-Flop):  $C=1 \rightarrow C=0$

- ullet Replaces SR master in SR Master-Slave with D master Latch

- Negative Edge Triggered D (Flip-Flop):  $C=1 \rightarrow C=0$

- ullet Replaces SR master in SR Master-Slave with D master Latch

- Negative Edge Triggered D (Flip-Flop):  $C=1 \rightarrow C=0$

#### Summary

Ook,

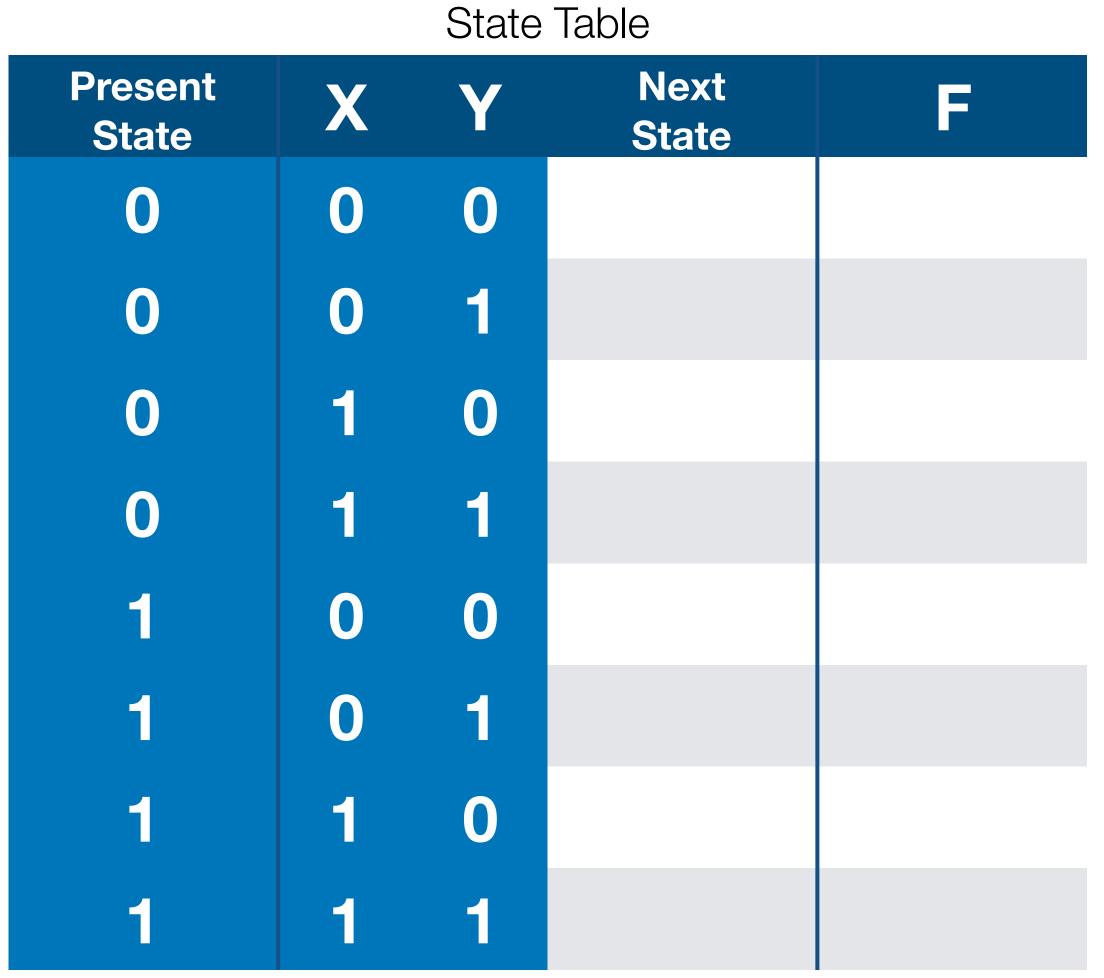

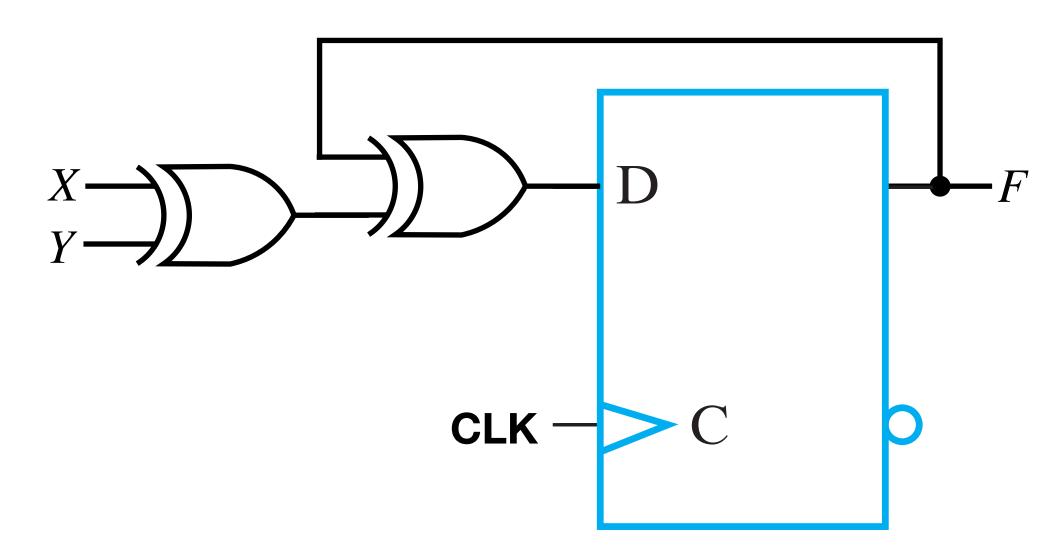

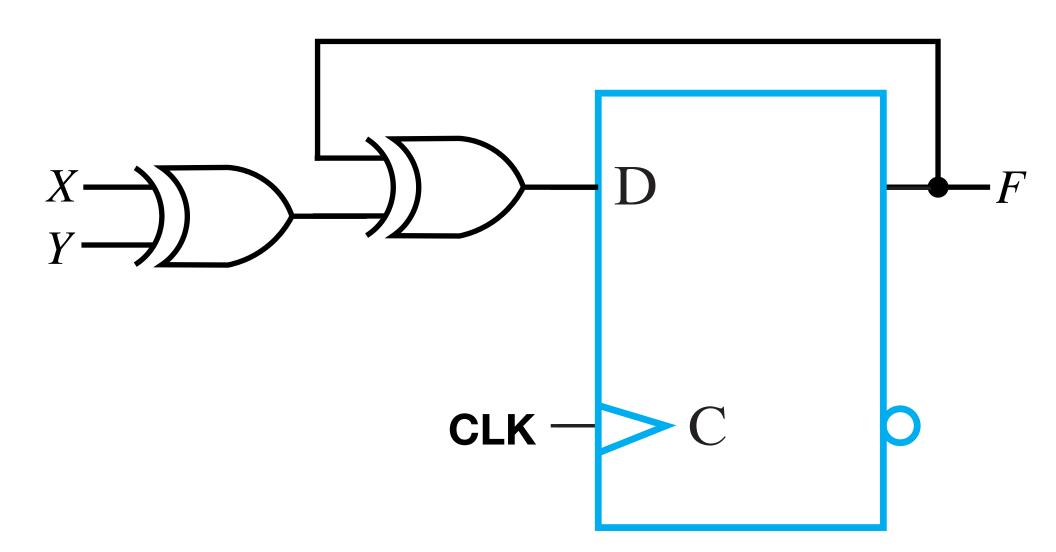

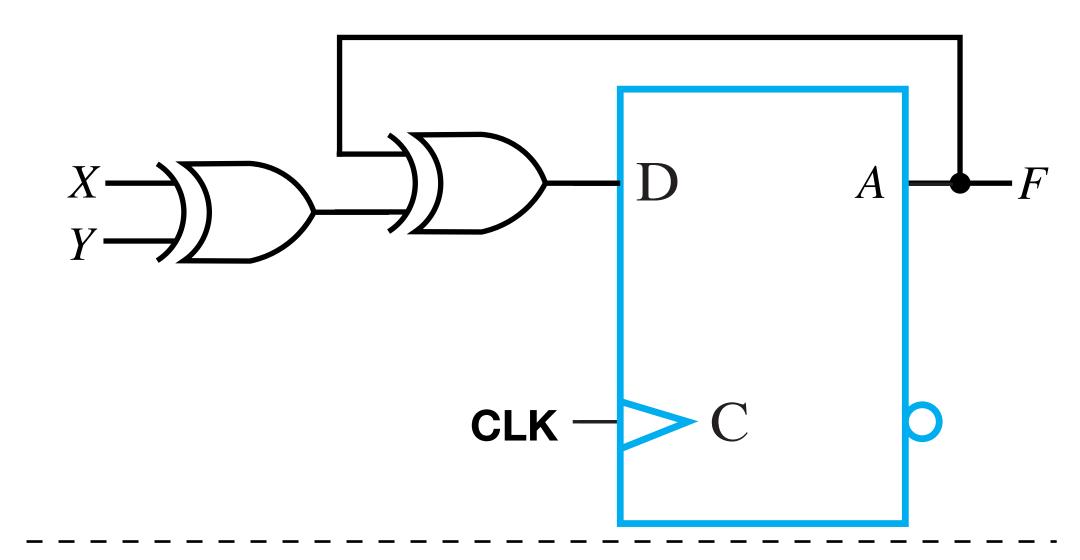

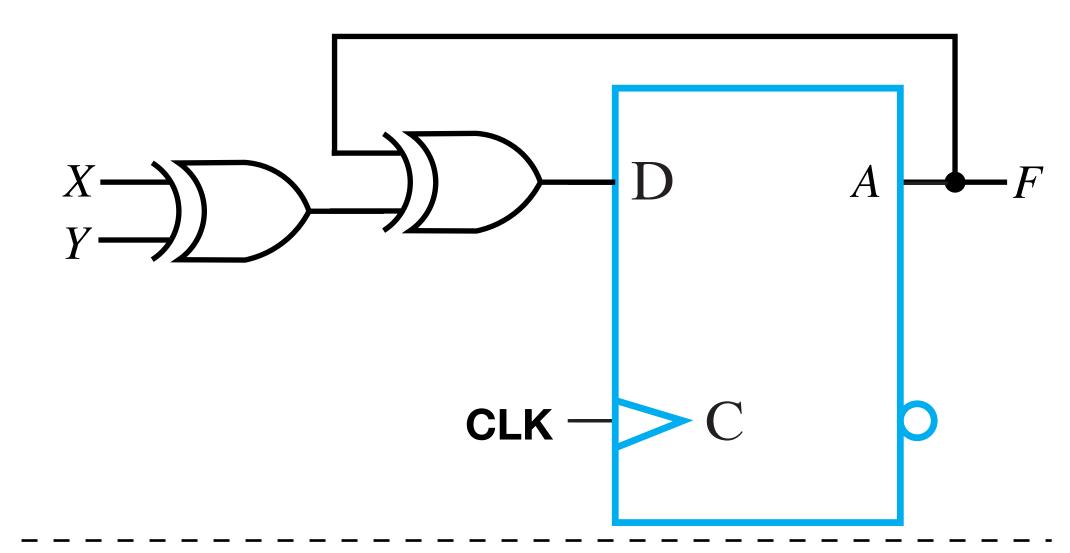

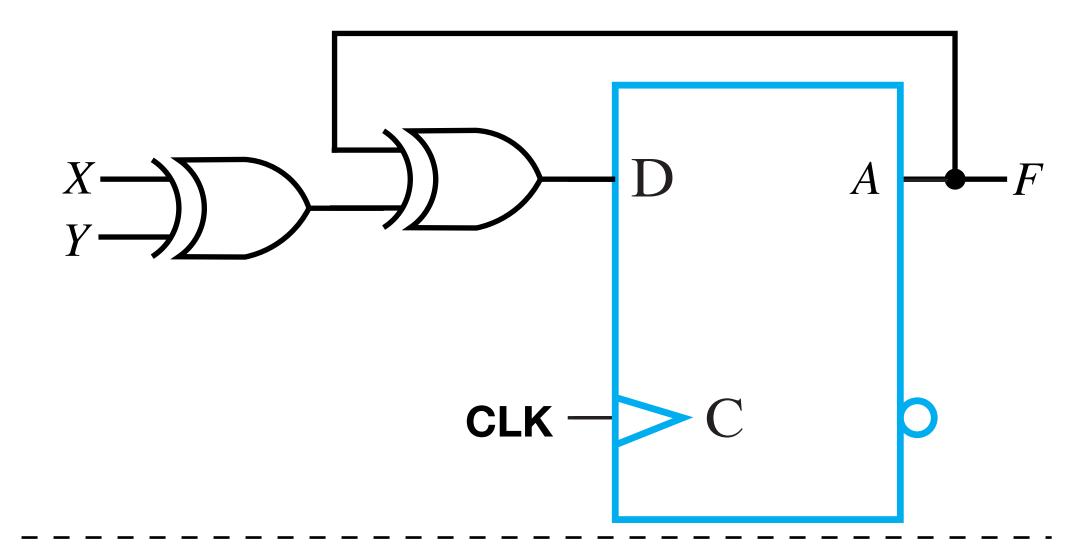

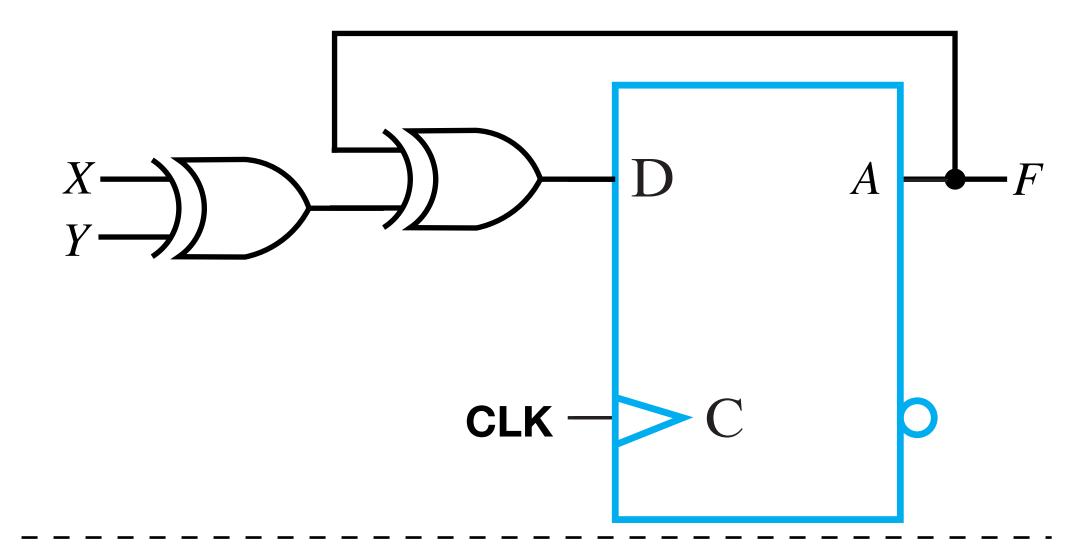

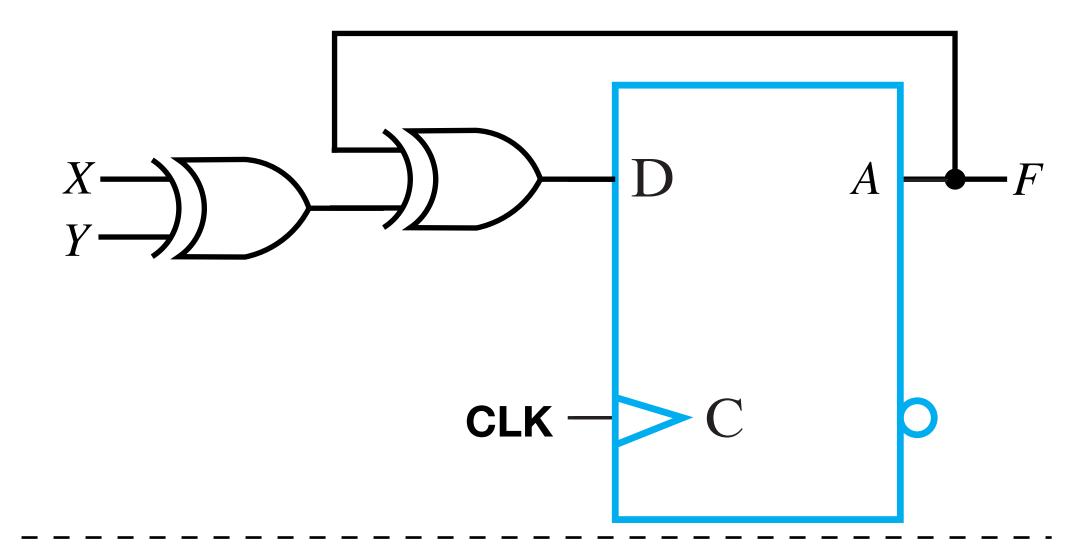

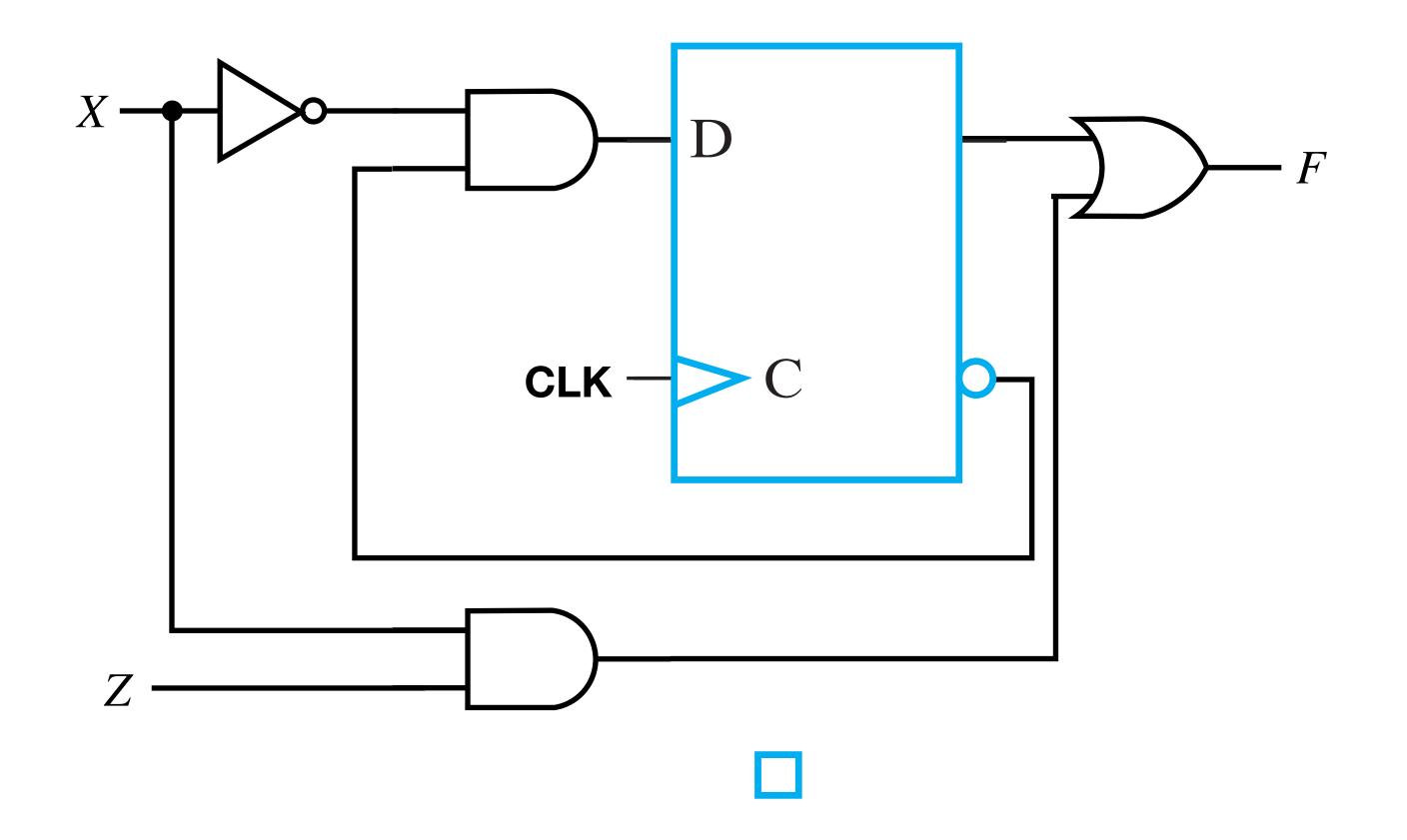

## Sequential Circuit Analysis

State Table; State Diagram

- Similar to truth table

- Input, and Current states

- Output and Next states

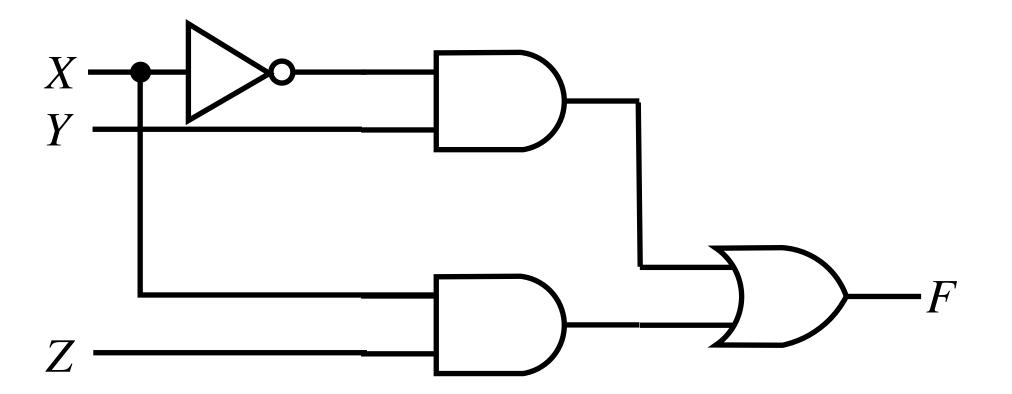

P2 Analysis

Truth Table

| X | Y | Z | F |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 1 | 0 | 1 |

| 1 | 0 | 0 | 0 |

| 1 | 1 | 0 | 0 |

| 0 | 0 | 1 | 0 |

| 0 | 1 | 1 | 1 |

| 1 | 0 | 1 | 1 |

| 1 | 1 | 1 | 1 |

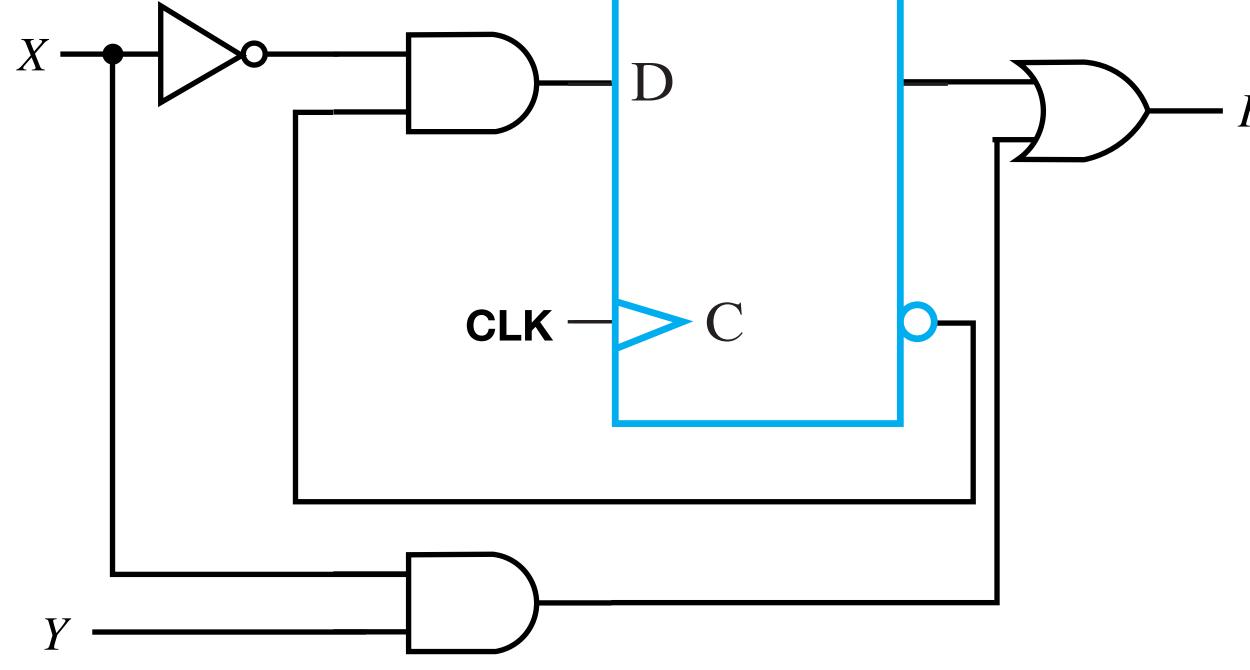

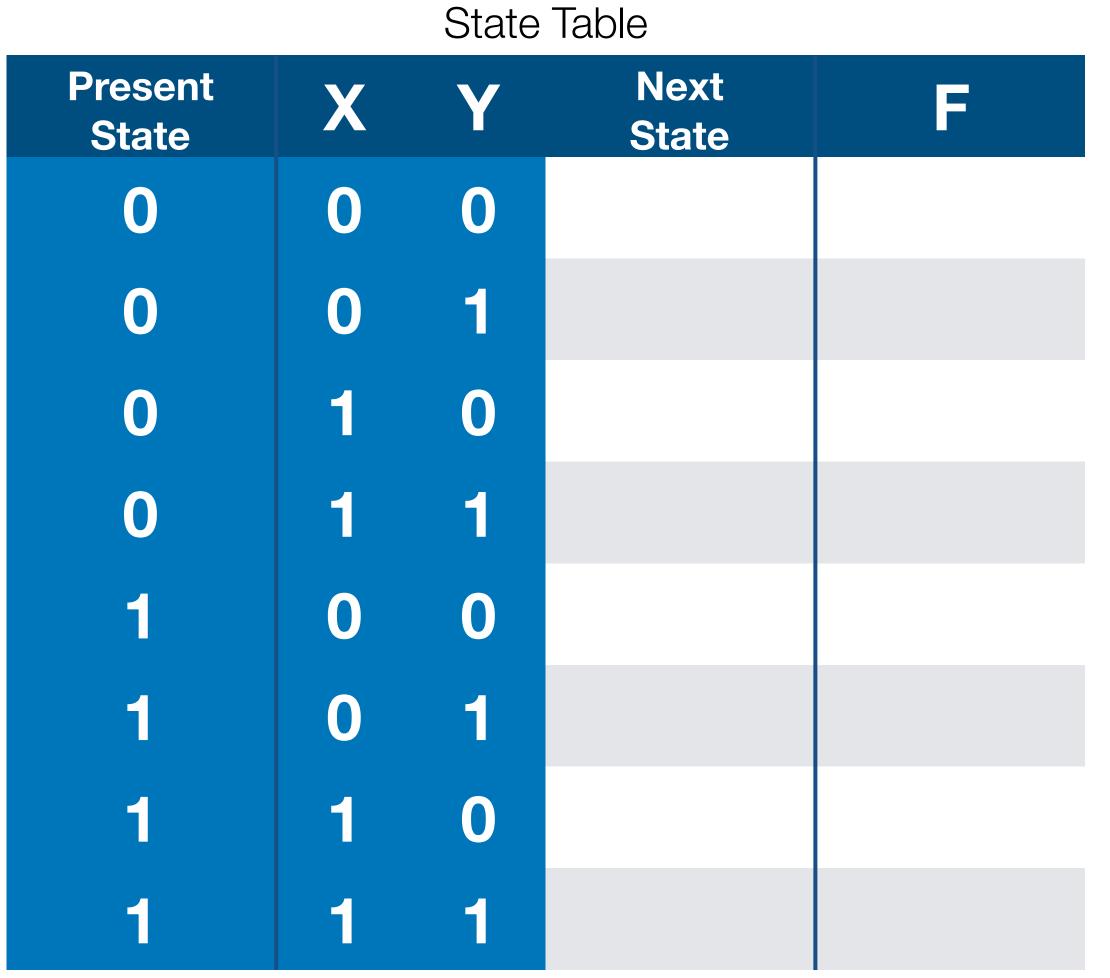

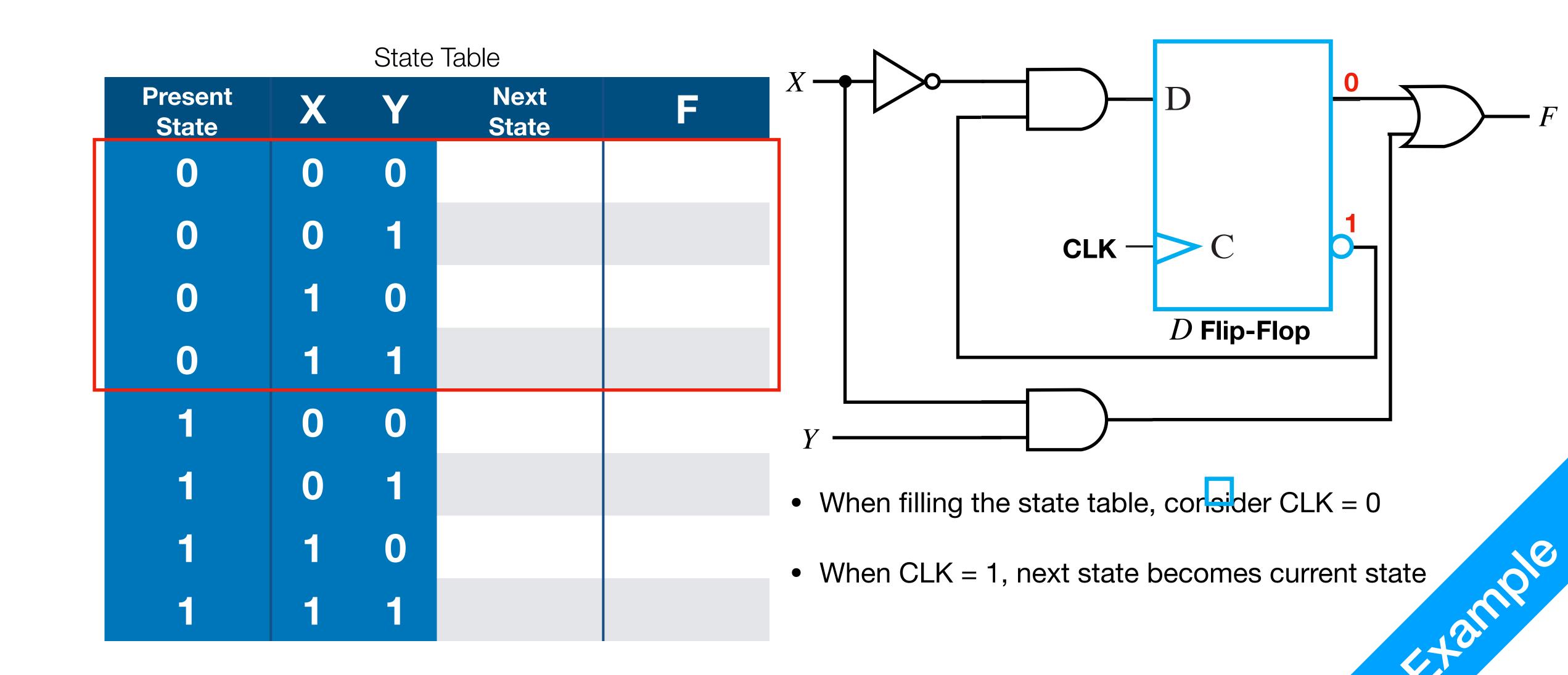

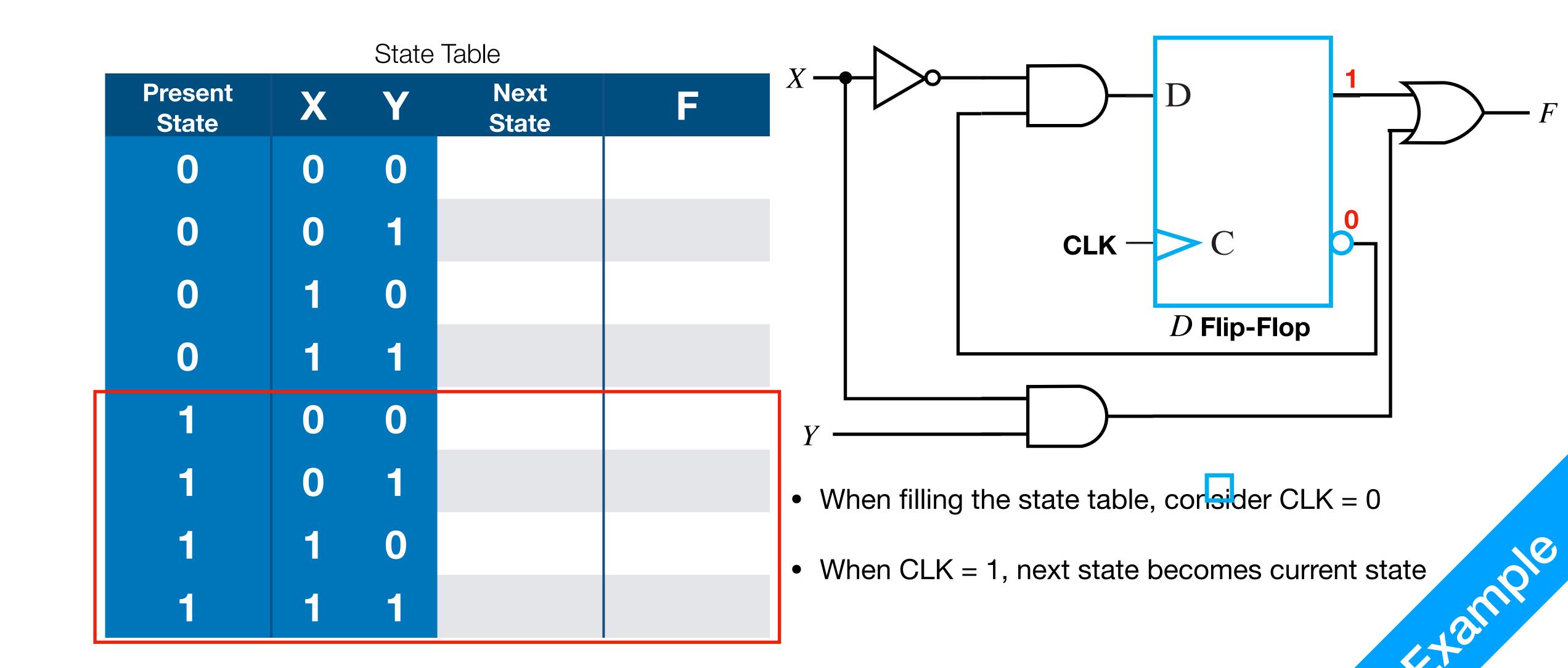

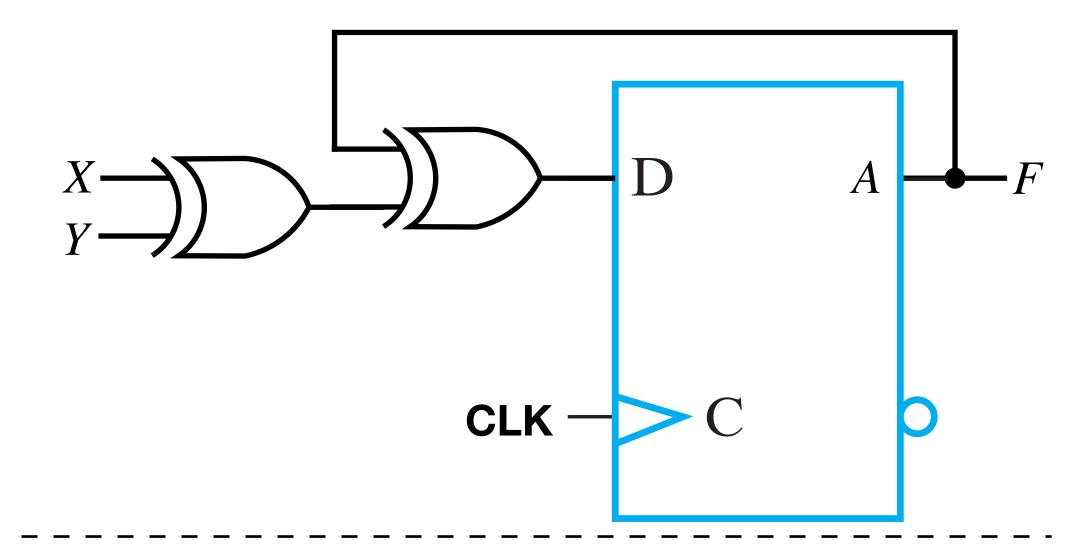

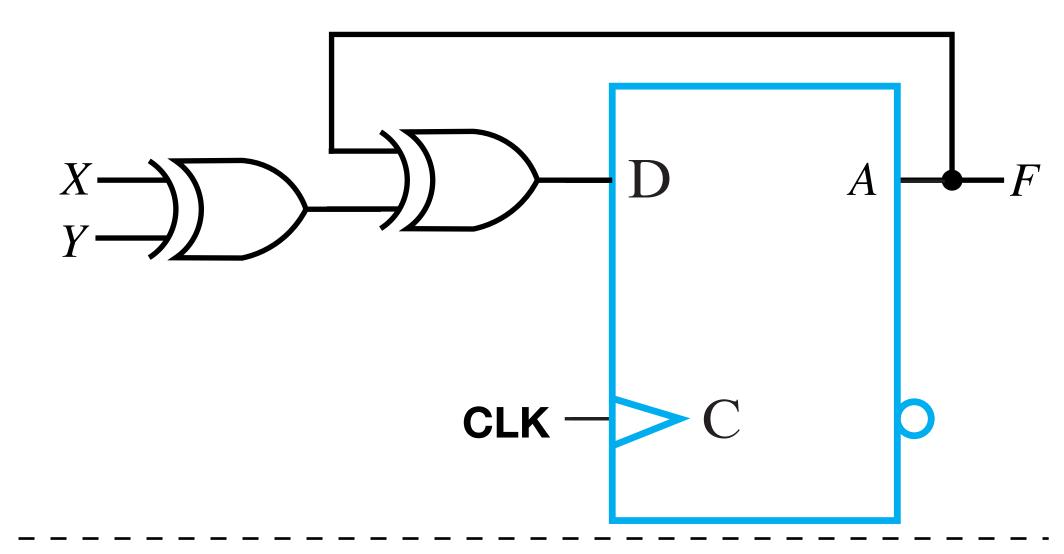

- When filling the state table, consider CLK = 0

- When CLK = 1, next state becomes current state

- When filling the state table, consider CLK = 0

- When CLK = 1, next state becomes current state

State Table

| Present<br>State | X | Y | Next<br>State | F |

|------------------|---|---|---------------|---|

| 0                | 0 | 0 |               |   |

| 0                | 0 | 1 |               |   |

| 0                | 1 | 0 |               |   |

| 0                | 1 | 1 |               |   |

| 1                | 0 | 0 |               |   |

| 1                | 0 | 1 |               |   |

| 1                | 1 | 0 |               |   |

| 1                | 1 | 1 |               |   |

- When filling the state table, consider CLK = 0

- When CLK = 1, next state becomes current state

ciso

State Table

| Present<br>State | X | Y | Next<br>State | F |

|------------------|---|---|---------------|---|

| 0                | 0 | 0 |               |   |

| 0                | 0 | 1 |               |   |

| 0                | 1 | 0 |               |   |

| 0                | 1 | 1 |               |   |

| 1                | 0 | 0 |               |   |

| 1                | 0 | 1 |               |   |

| 1                | 1 | 0 |               |   |

| 1                | 1 | 1 |               |   |

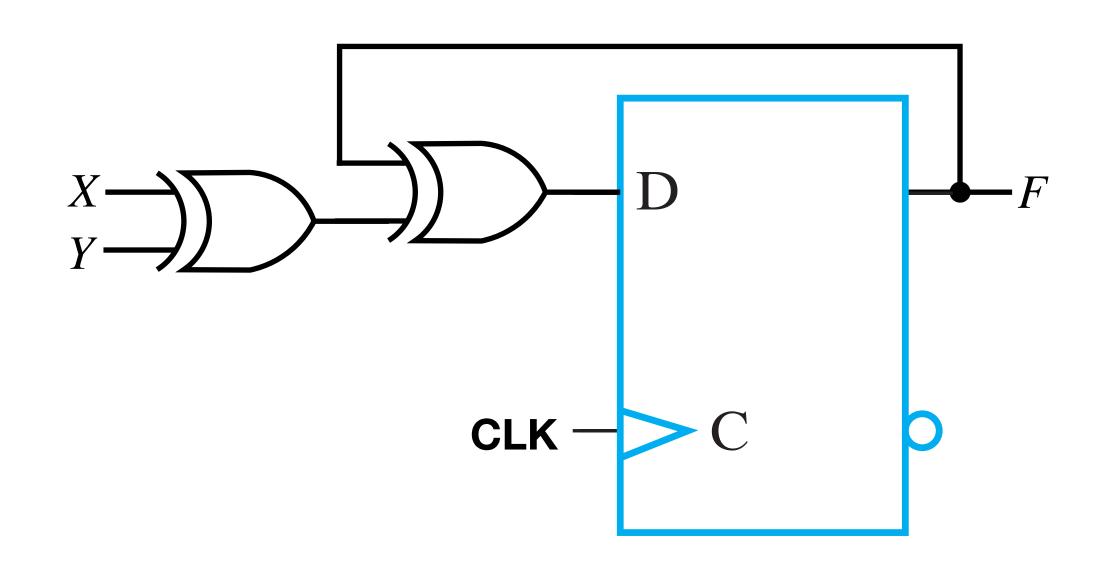

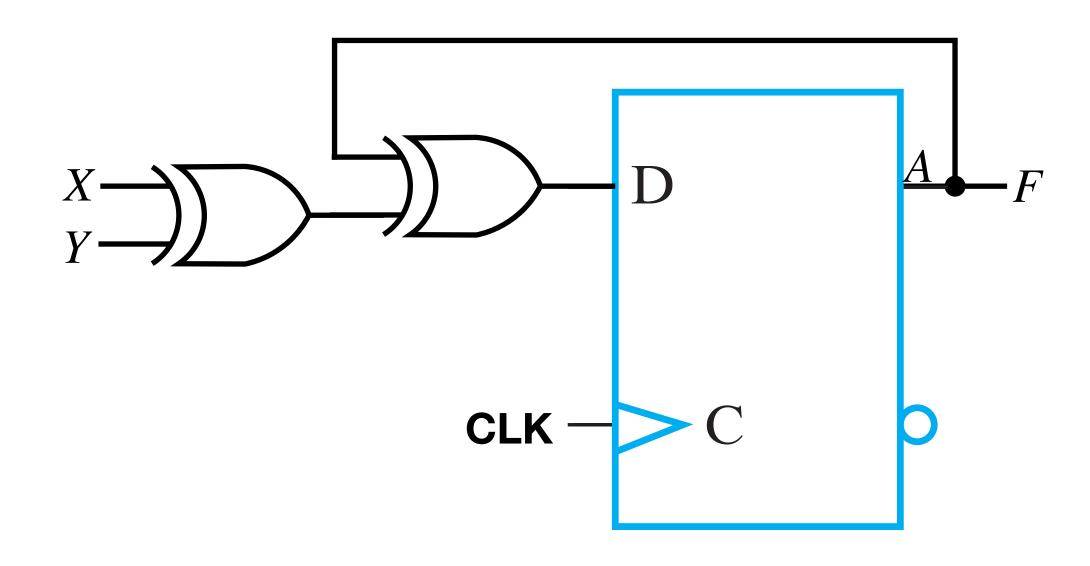

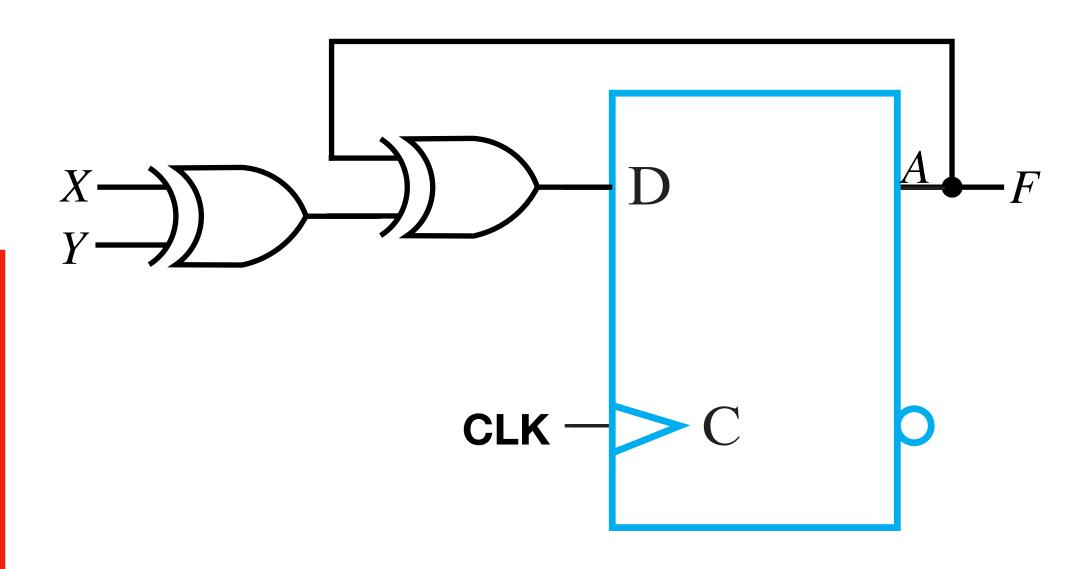

$$D_A = X \oplus Y \oplus A$$

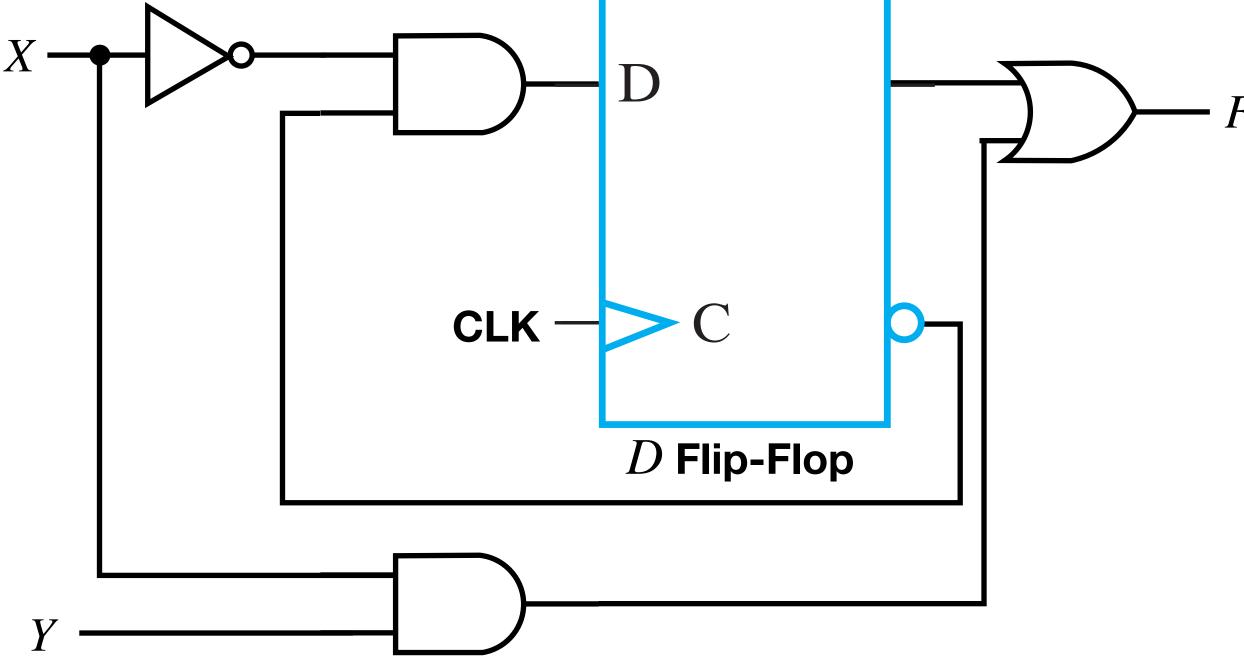

- When filling the state table, consider CLK = 0

- When CLK = 1, next state becomes current state

| Present<br>State | X | Y | Next<br>State | F |

|------------------|---|---|---------------|---|

| 0                | 0 | 0 |               |   |

| 0                | 0 | 1 |               |   |

| 0                | 1 | 0 |               |   |

| 0                | 1 | 1 |               |   |

| 1                | 0 | 0 |               |   |

| 1                | 0 | 1 |               |   |

| 1                | 1 | 0 |               |   |

|                  | 1 | 1 |               |   |

$$D_A = X \oplus Y \oplus A$$

- When filling the state table, consider CLK = 0

- When CLK = 1, next state becomes current state

State Table

| Present<br>State | X | Y | Next<br>State | F |

|------------------|---|---|---------------|---|

| 0                | 0 | 0 | 0             | 0 |

| 0                | 0 | 1 | 1             | 0 |

| 0                | 1 | 0 | 1             | 0 |

| 0                | 1 | 1 | 0             | 0 |

| 1                | 0 | 0 |               |   |

| 1                | 0 | 1 |               |   |

| 1                | 1 | 0 |               |   |

| 1                | 1 | 1 |               |   |

- When filling the state table, consider CLK = 0

- When CLK = 1, next state becomes current state

C/S®

State Table

| Present<br>State | X | Y | Next<br>State | F |

|------------------|---|---|---------------|---|

| 0                | 0 | 0 | 0             | 0 |

| 0                | 0 | 1 | 1             | 0 |

| 0                | 1 | 0 | 1             | 0 |

| 0                | 1 | 1 | 0             | 0 |

| 1                | 0 | 0 |               |   |

| 1                | 0 | 1 |               |   |

| 1                | 1 | 0 |               |   |

| 1                | 1 | 1 |               |   |

- When filling the state table, consider CLK = 0

- When CLK = 1, next state becomes current state

Cisso

State Table

| Present<br>State | X | Y | Next<br>State | F |

|------------------|---|---|---------------|---|

| 0                | 0 | 0 | 0             | 0 |

| 0                | 0 | 1 | 1             | 0 |

| 0                | 1 | 0 | 1             | 0 |

| 0                | 1 | 1 | 0             | 0 |

| 1                | 0 | 0 | 1             | 1 |

| 1                | 0 | 1 | 0             | 1 |

| 1                | 1 | 0 | 0             | 1 |

| 1                | 1 | 1 | 1             | 1 |

- When filling the state table, consider CLK = 0

- When CLK = 1, next state becomes current state

State Table

|   | sent<br>ate | X | Y | Ne<br>Sta |   | <b>Z</b> |

|---|-------------|---|---|-----------|---|----------|

| A | В           |   |   | A         | В |          |

| 0 | 0           | 0 | 0 |           |   |          |

| 0 | 0           | 0 | 1 |           |   |          |

| 0 | 0           | 1 | 0 |           |   |          |

| 0 | 0           | 1 | 1 |           |   |          |

| 0 | 1           | 0 | 0 |           |   |          |

| 0 | 1           | 0 | 1 |           |   |          |

| 0 | 1           | 1 | 0 |           |   |          |

| 0 | 1           | 1 | 1 |           |   |          |

- Draw circuit diagram

- Fill the 8 rows

A CISO

State Table

|   | sent<br>ate | X | Y | Next<br>State | <b>Z</b> |

|---|-------------|---|---|---------------|----------|

| A | В           |   |   | A B           |          |

| 0 | 0           | 0 | 0 |               |          |

| 0 | 0           | 0 | 1 |               |          |

| 0 | 0           | 1 | 0 |               |          |

| 0 | 0           | 1 | 1 |               |          |

| 0 | 1           | 0 | 0 |               |          |

| 0 | 1           | 0 | 1 |               |          |

| 0 | 1           | 1 | 0 |               |          |

| 0 | 1           | 1 | 1 |               |          |

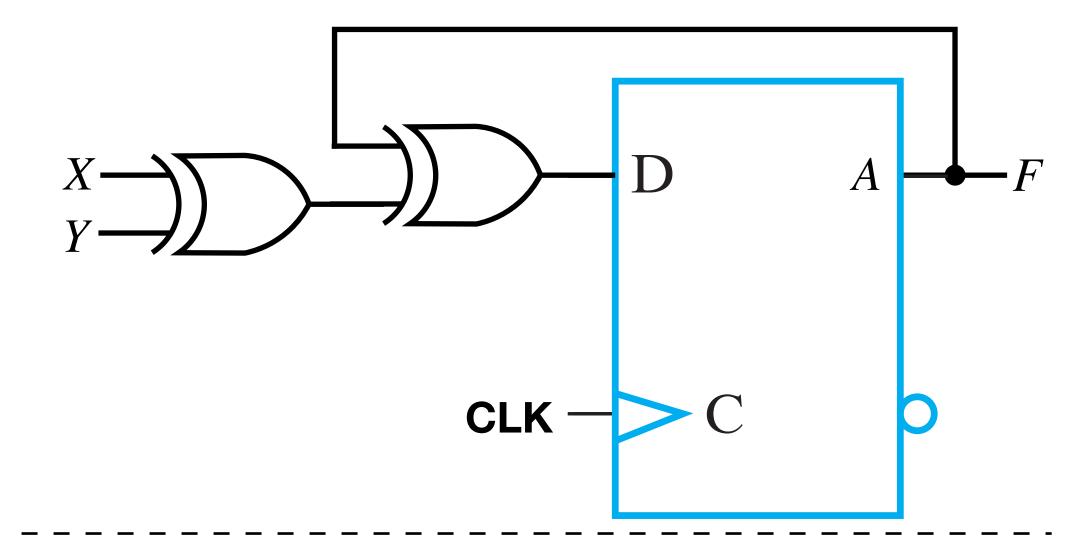

$$D_{A} = \overline{X}A + XY$$

$$D_{B} = \overline{X}B + XA$$

$$Z = XB$$

- Draw circuit diagram

- Fill the 8 rows

e Cise

What happens when there are multiple flip-flops?

- What happens when there are multiple flip-flops?

- Does it work with Latches?

- A circuit with one D flip-flop:  $D_A = A \oplus X$

- Draw the circuit diagram

- Do the state table

- A circuit with one D flip-flop:  $D_A = A \oplus X$

- Draw the circuit diagram

- Do the state table

#### State Table

| Present<br>State | X | Next<br>State |

|------------------|---|---------------|

| 0                | 0 |               |

| 0                | 1 |               |

| 1                | 1 |               |

| 1                | 0 |               |

e cis

- A circuit with 2 D flip-flops:  $D_A=A\oplus B$ ,  $D_B=\overline{B}\cdot X$ ,  $F=\overline{A}B$

- Do the state table

| Presen | t State | V | Next | State |  |

|--------|---------|---|------|-------|--|

| A      | В       | X | A    | В     |  |

| 0      | 0       | 0 |      |       |  |

| 0      | 0       | 1 |      |       |  |

| 0      | 1       | 0 |      |       |  |

| 0      | 1       | 1 |      |       |  |

| 1      | 0       | 0 |      |       |  |

| 1      | 0       | 1 |      |       |  |

| 1      | 1       | 0 |      |       |  |

| 1      | 1       | 4 |      |       |  |

State Table

e, cis

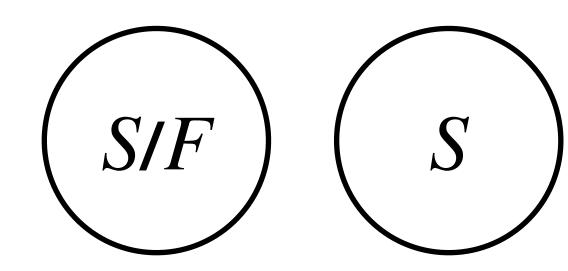

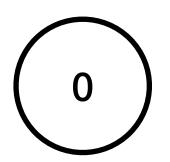

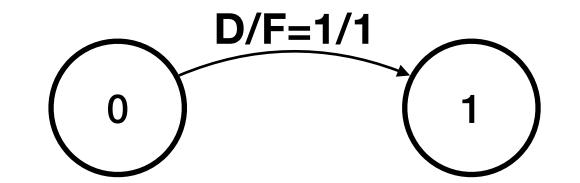

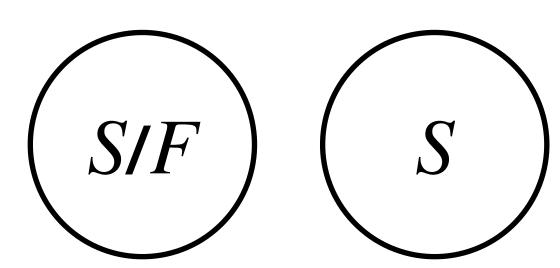

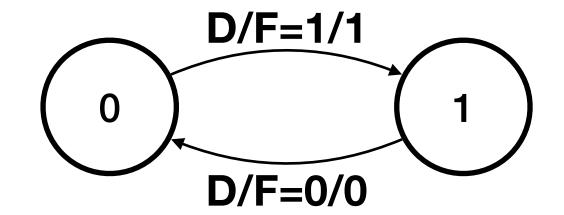

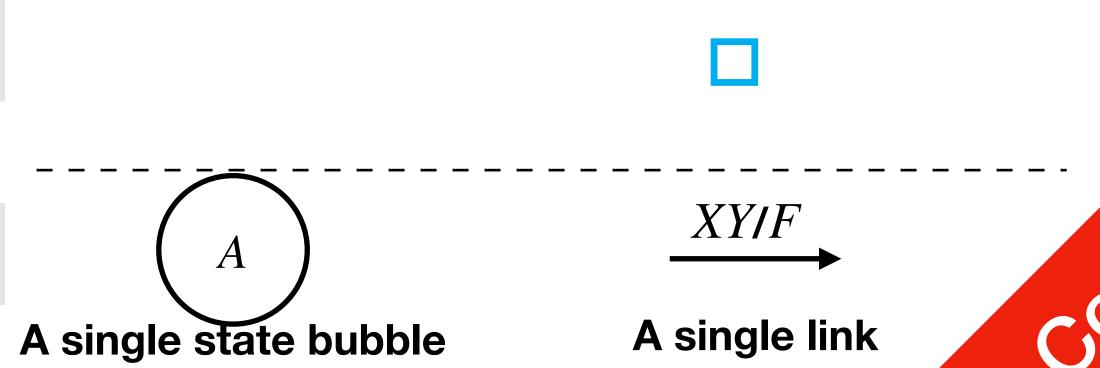

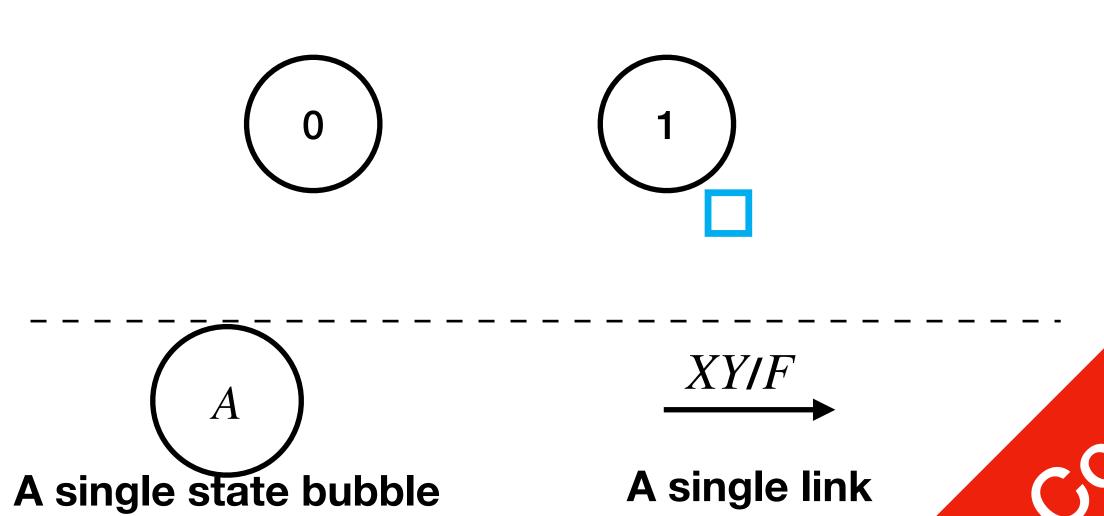

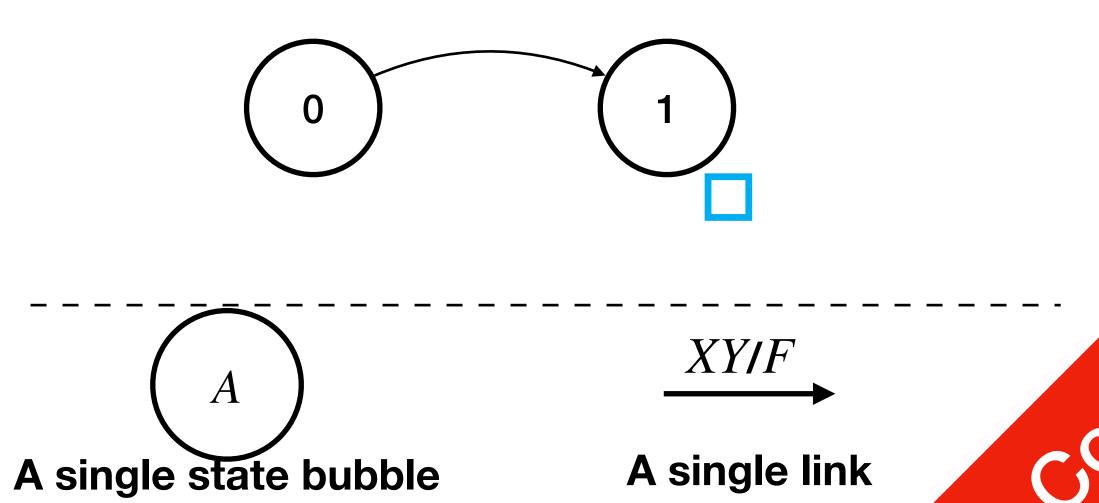

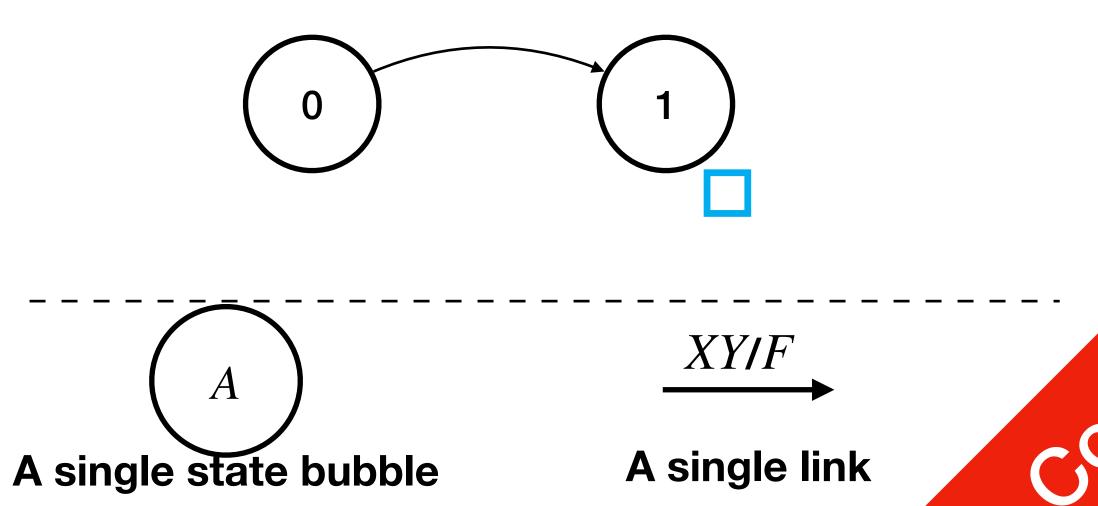

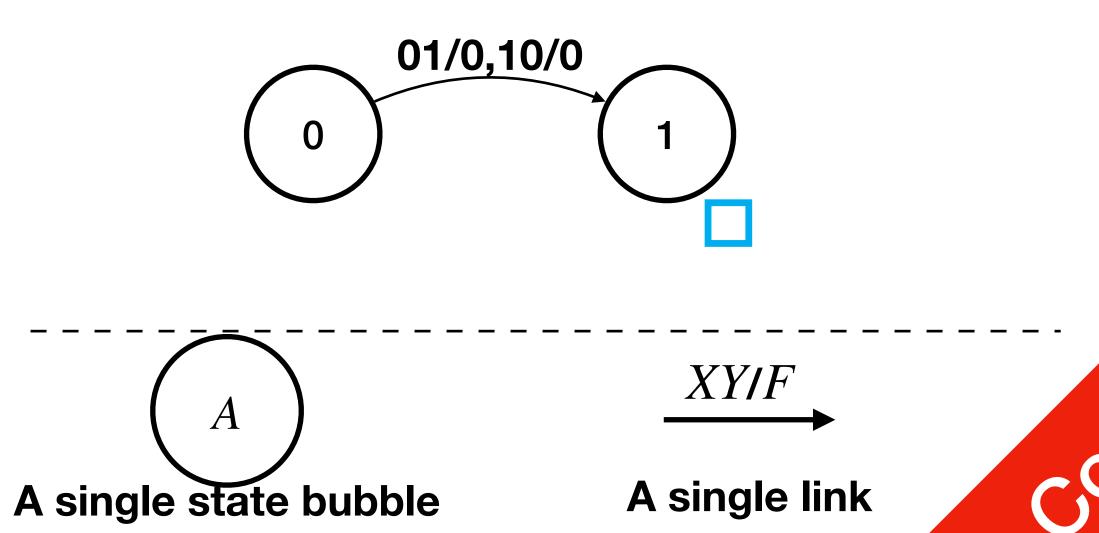

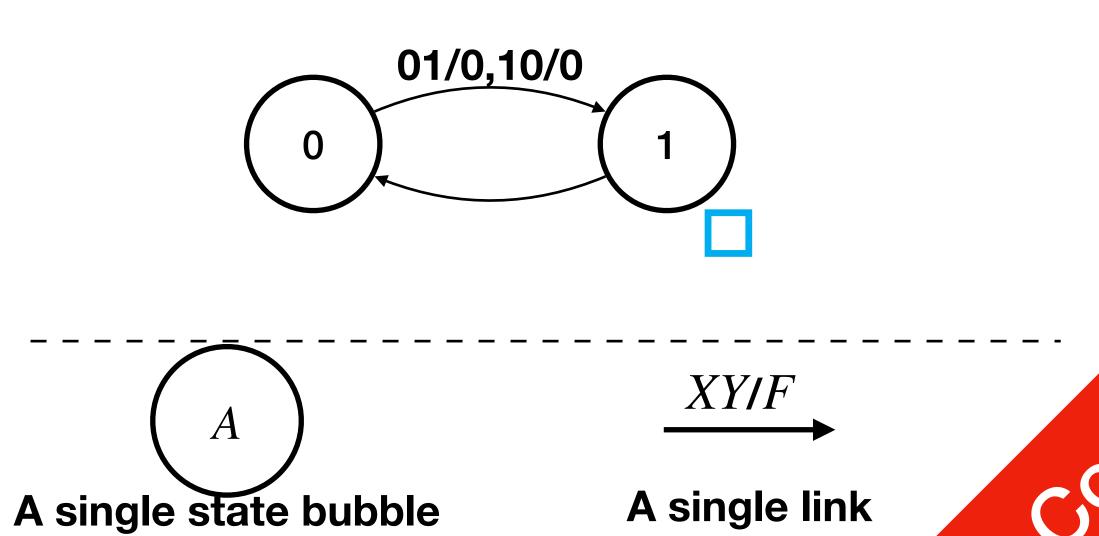

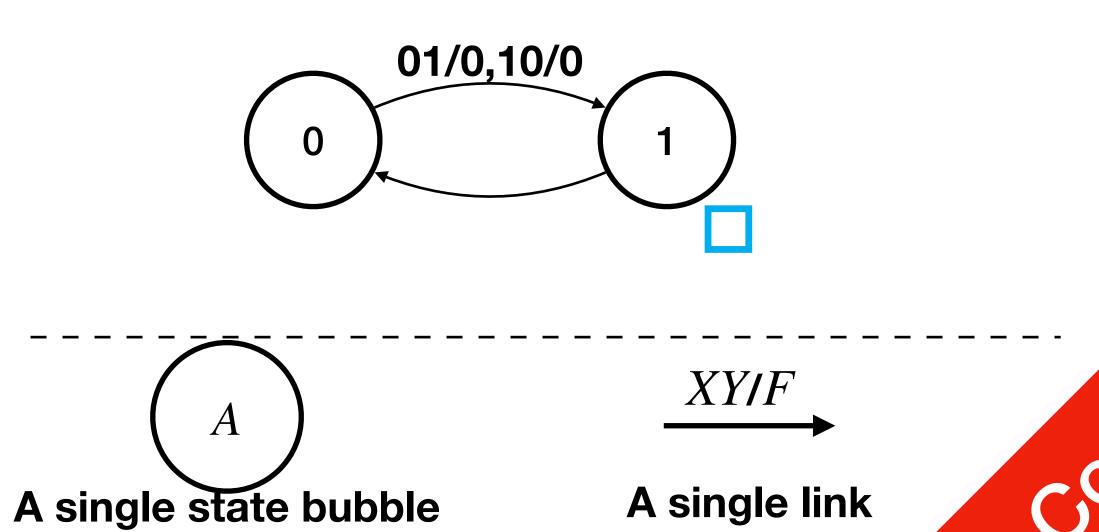

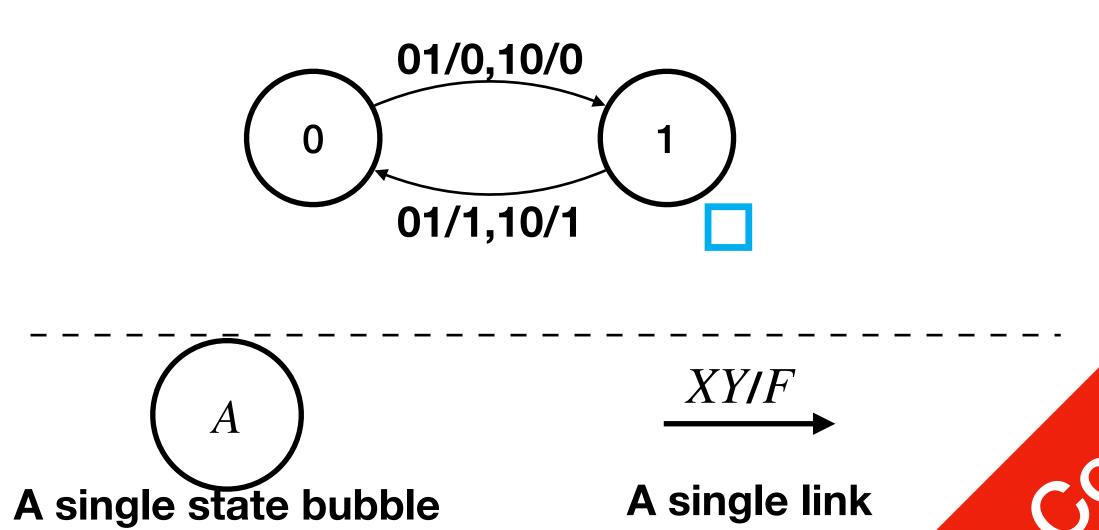

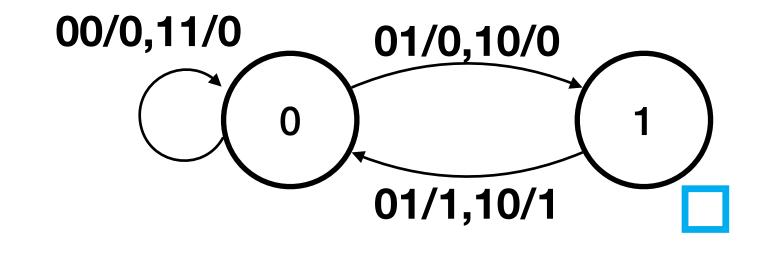

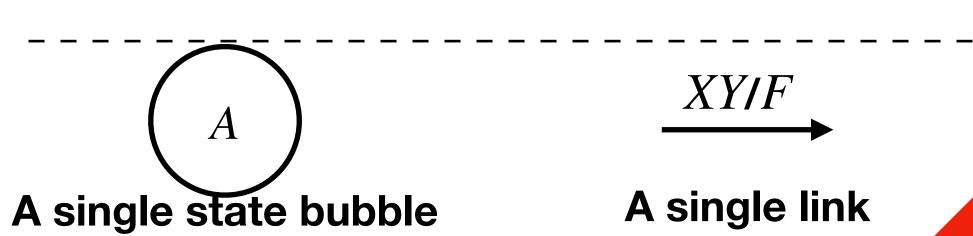

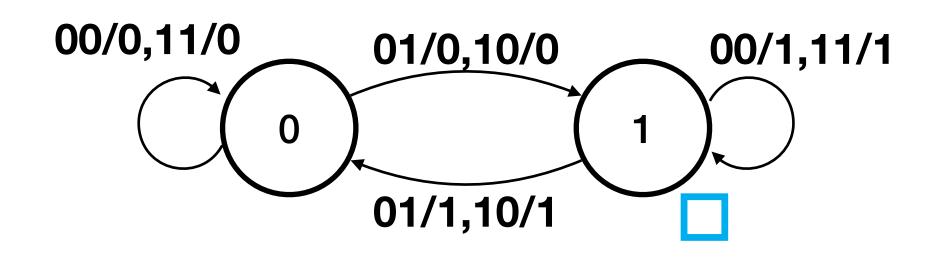

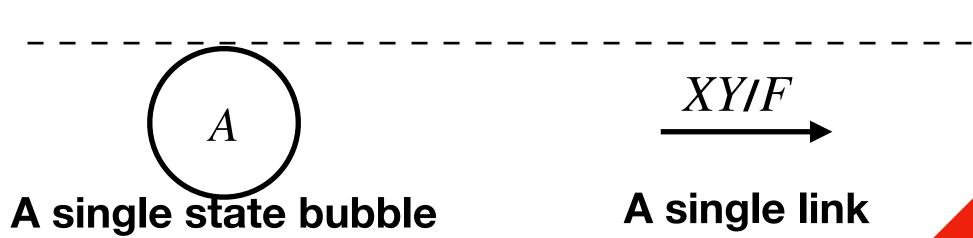

- Similar to state table

- Models state transitions

- A state is represented in a bubble

- Directed links between bubbles: the input used to perform transition Source: **present** state, Target: **next** state (next **CLK**); (optional output F)

- State bubble with state as S (optional output F)

- Similar to state table

- Models state transitions

- A state is represented in a bubble

- Directed links between bubbles: the input used to perform transition Source: **present** state, Target: **next** state (next **CLK**); (optional output F)

- State bubble with state as S (optional output F)

Color,

- Similar to state table

- Models state transitions

- A state is represented in a bubble

- Directed links between bubbles: the input used to perform transition Source: **present** state, Target: **next** state (next **CLK**); (optional output F)

- State bubble with state as S (optional output F)

- Similar to state table

- Models state transitions

- A state is represented in a bubble

- Directed links between bubbles: the input used to perform transition Source: **present** state, Target: **next** state (next **CLK**); (optional output F)

- State bubble with state as S (optional output F)

| Present<br>State | X | Y | Next<br>State | F |

|------------------|---|---|---------------|---|

| 0                | 0 | 0 | 0             | 0 |

| 0                | 0 | 1 | 1             | 0 |

| 0                | 1 | 0 | 1             | 0 |

| 0                | 1 | 1 | 0             | 0 |

| 1                | 0 | 0 | 1             | 1 |

| 1                | 0 | 1 | 0             | 1 |

| 1                | 1 | 0 | 0             | 1 |

| 1                | 1 | 1 | 1             | 1 |

| Present<br>State | X | Y | Next<br>State | F |

|------------------|---|---|---------------|---|

| 0                | 0 | 0 | 0             | 0 |

| 0                | 0 | 1 | 1             | 0 |

| 0                | 1 | 0 | 1             | 0 |

| 0                | 1 | 1 | 0             | 0 |

| 1                | 0 | 0 | 1             | 1 |

| 1                | 0 | 1 | 0             | 1 |

| 1                | 1 | 0 | 0             | 1 |

| 1                | 1 | 1 | 1             | 1 |

| Present<br>State | X | Y | Next<br>State | F |

|------------------|---|---|---------------|---|

| 0                | 0 | 0 | 0             | 0 |

| 0                | 0 | 1 | 1             | 0 |

| 0                | 1 | 0 | 1             | 0 |

| 0                | 1 | 1 | 0             | 0 |

| 1                | 0 | 0 | 1             | 1 |

| 1                | 0 | 1 | 0             | 1 |

| 1                | 1 | 0 | 0             | 1 |

| 1                | 1 | 1 | 1             | 1 |

| Present<br>State | X | Y | Next<br>State | F |

|------------------|---|---|---------------|---|

| 0                | 0 | 0 | 0             | 0 |

| 0                | 0 | 1 | 1             | 0 |

| 0                | 1 | 0 | 1             | 0 |

| 0                | 1 | 1 | 0             | 0 |

| 1                | 0 | 0 | 1             | 1 |

| 1                | 0 | 1 | 0             | 1 |

| 1                | 1 | 0 | 0             | 1 |

| 1                | 1 | 1 | 1             | 1 |

| Present<br>State | X | Y | Next<br>State | F |

|------------------|---|---|---------------|---|

| 0                | 0 | 0 | 0             | 0 |

| 0                | 0 | 1 | 1             | 0 |

| 0                | 1 | 0 | 1             | 0 |

| 0                | 1 | 1 | 0             | 0 |

| 1                | 0 | 0 | 1             | 1 |

| 1                | 0 | 1 | 0             | 1 |

| 1                | 1 | 0 | 0             | 1 |

| 1                | 1 | 1 | 1             | 1 |

| Present<br>State | X | Y | Next<br>State | F |

|------------------|---|---|---------------|---|

| 0                | 0 | 0 | 0             | 0 |

| 0                | 0 | 1 | 1             | 0 |

| 0                | 1 | 0 | 1             | 0 |

| 0                | 1 | 1 | 0             | 0 |

| 1                | 0 | 0 | 1             | 1 |

| 1                | 0 | 1 | 0             | 1 |

| 1                | 1 | 0 | 0             | 1 |

| 1                | 1 | 1 | 1             | 1 |

| Present<br>State | X | Y | Next<br>State | F |

|------------------|---|---|---------------|---|

| 0                | 0 | 0 | 0             | 0 |

| 0                | 0 | 1 | 1             | 0 |

| 0                | 1 | 0 | 1             | 0 |

| 0                | 1 | 1 | 0             | 0 |

| 1                | 0 | 0 | 1             | 1 |

| 1                | 0 | 1 | 0             | 1 |

| 1                | 1 | 0 | 0             | 1 |

| 1                | 1 | 1 | 1             | 1 |

| Present<br>State | X | Y | Next<br>State | F |

|------------------|---|---|---------------|---|

| 0                | 0 | 0 | 0             | 0 |

| 0                | 0 | 1 | 1             | 0 |

| 0                | 1 | 0 | 1             | 0 |

| 0                | 1 | 1 | 0             | 0 |

| 1                | 0 | 0 | 1             | 1 |

| 1                | 0 | 1 | 0             | 1 |

| 1                | 1 | 0 | 0             | 1 |

| 1                | 1 | 1 | 1             | 1 |

| Present<br>State | X | Y | Next<br>State | F |

|------------------|---|---|---------------|---|

| 0                | 0 | 0 | 0             | 0 |

| 0                | 0 | 1 | 1             | 0 |

| 0                | 1 | 0 | 1             | 0 |

| 0                | 1 | 1 | 0             | 0 |

| 1                | 0 | 0 | 1             | 1 |

| 1                | 0 | 1 | 0             | 1 |

| 1                | 1 | 0 | 0             | 1 |

| 1                | 1 | 1 | 1             | 1 |

| Present<br>State | X | Y | Next<br>State | F |

|------------------|---|---|---------------|---|

| 0                | 0 | 0 | 0             | 0 |

| 0                | 0 | 1 | 1             | 0 |

| 0                | 1 | 0 | 1             | 0 |

| 0                | 1 | 1 | 0             | 0 |

| 1                | 0 | 0 | 1             | 1 |

| 1                | 0 | 1 | 0             | 1 |

| 1                | 1 | 0 | 0             | 1 |

| 1                | 1 | 1 | 1             | 1 |

• Draw the state diagram for:  $D_A=\overline{X}A+XY$ ,  $D_B=\overline{X}B+XA$ , Z=XB

- A circuit with one D flip-flop:  $D_A = A \oplus X$

- Draw the state diagram

P1 Analysis

## In Class Exercise 1

- A circuit with one D flip-flop:  $D_A = A \oplus X$

- Draw the state diagram

State Table

| Present<br>State | X | Next<br>State |

|------------------|---|---------------|

| 0                | 0 | 0             |

| 0                | 1 | 1             |

| 1                | 0 | 1             |

| 1                | 1 | 0             |

e de la cisa

- A circuit with 2 D flip-flops:  $D_A=A\oplus B$ ,  $D_B=\overline{B}\cdot X$ ,  $F=\overline{A}B$

- Do the state diagram

| Presen | t State | X | Next State |   |   |

|--------|---------|---|------------|---|---|

| A      | В       |   | A          | В |   |

| 0      | 0       | 0 | 0          | 0 | 0 |

| 0      | 0       | 1 | 0          | 1 | 0 |

| 0      | 1       | 0 | 1          | 0 | 1 |

| 0      | 1       | 1 | 1          | 0 | 1 |

| 1      | 0       | 0 | 1          | 0 | 0 |

| 1      | 0       | 1 | 1          | 1 | 0 |

| 1      | 1       | 0 | 0          | 0 | 0 |

| 1      | 1       | 1 | 0          | 0 | 0 |

State Table

e icis

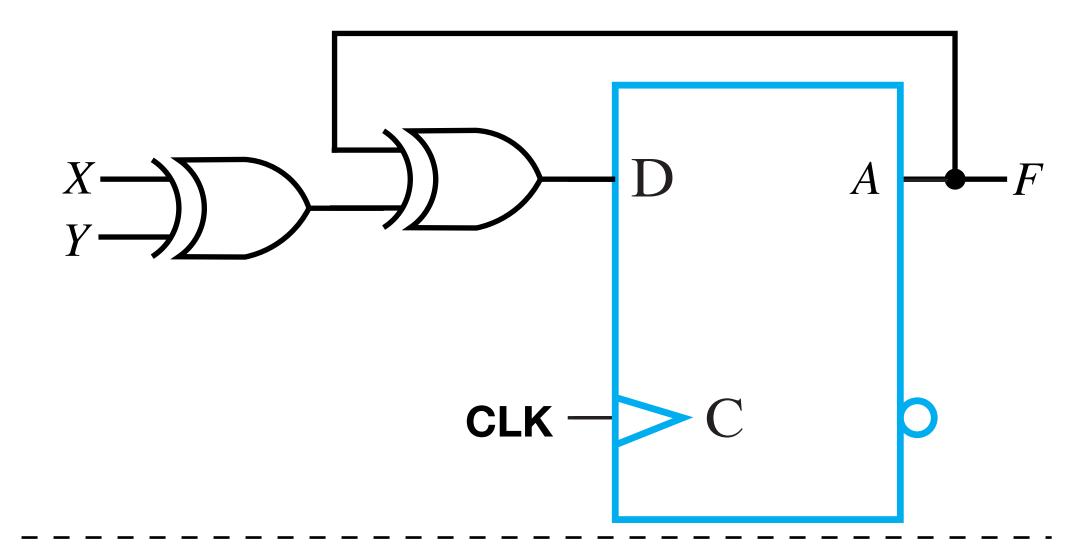

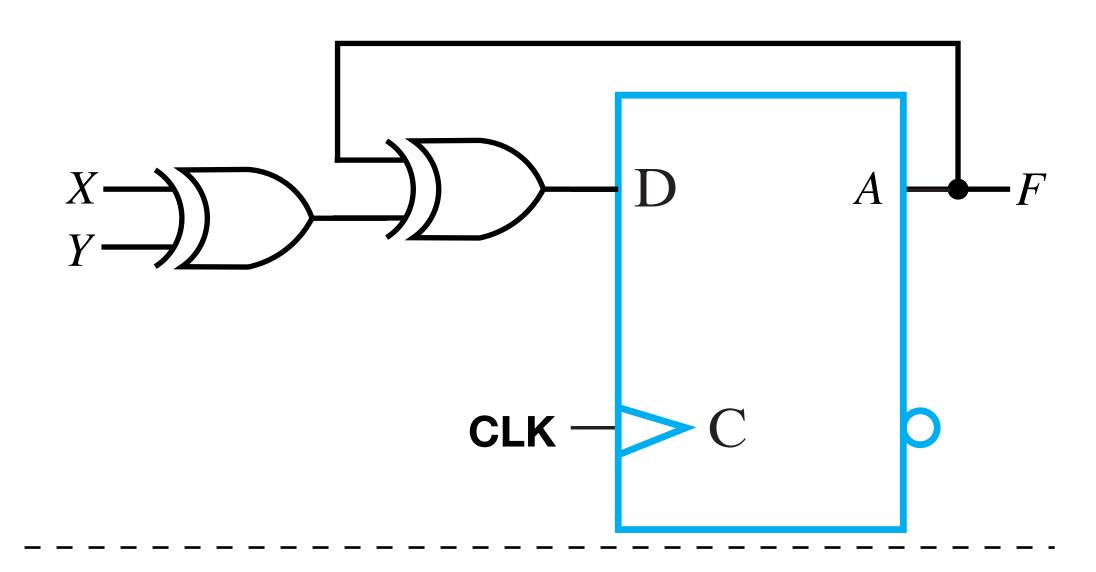

## LogicWorks Exercise

- Implement D flip flop using D latch and SR latch Save it as a component in your library

- Implement circuit  $D_S = X \oplus Y \oplus S$ , where  $D_S$  is a D flip flop

- Implement  $D_A=\overline{X}A+XY,$   $D_B=\overline{X}B+XA,$  Z=XB

- Draw the state table and diagram, and verify your table with LogicWorks