# CSCI 150 Introduction to Digital and Computer System Design Lecture 3: Combinational Logic Design III

Jetic Gū

# Overview

- Focus: Logic Functions

- Architecture: Combinatory Logical Circuits

- Textbook v4: Ch3 3.6; v5: Ch3 3.1, 3.4

- Core Ideas:

- 1. Terminologies: Value-Fixing, Transferring, Inverting, Enabler

- 2. Decoder

# Systematic Design Procedures

- **Specification**: Write a specification for the circuit

- 2. **Formulation**: Derive relationship between inputs and outputs of the system e.g. using truth table or Boolean expressions

- 3. **Optimisation**: Apply optimisation, minimise the number of logic gates and literals required

- 4. **Technology Mapping**: Transform design to new diagram using available implementation technology

- 5. **Verification**: Verify the correctness of the final design in meeting the specifications

# Systematic Design Procedures

- Hierarchical Design

- Divide complex designs into smaller functional blocks, then apply the same 5-step design procedures for each block

- Reusable, easier and more efficient Implementation

# Value-Fixing, Transferring, Inverting, Enabler

Elementary Combinational Logic Functions

# Value-Fixing, Transferring, and Inverting

- 1 Value-Fixing: giving a constant value to a wire

- F = 0; F = 1;

- 2 Transferring: giving a variable (wire) value from another variable (wire)

- F = X;

- 3 Inverting: inverting the value of a variable

- $F = \overline{X}$

# Value-Fixing, Transferring, and Inverting

0 - F = 0

1 Value-Fixing

1 Value-Fixing

$$X - F = X$$

2 Transferring

$$X \longrightarrow F = \overline{X}$$

3 Inverting

## Vector Denotation

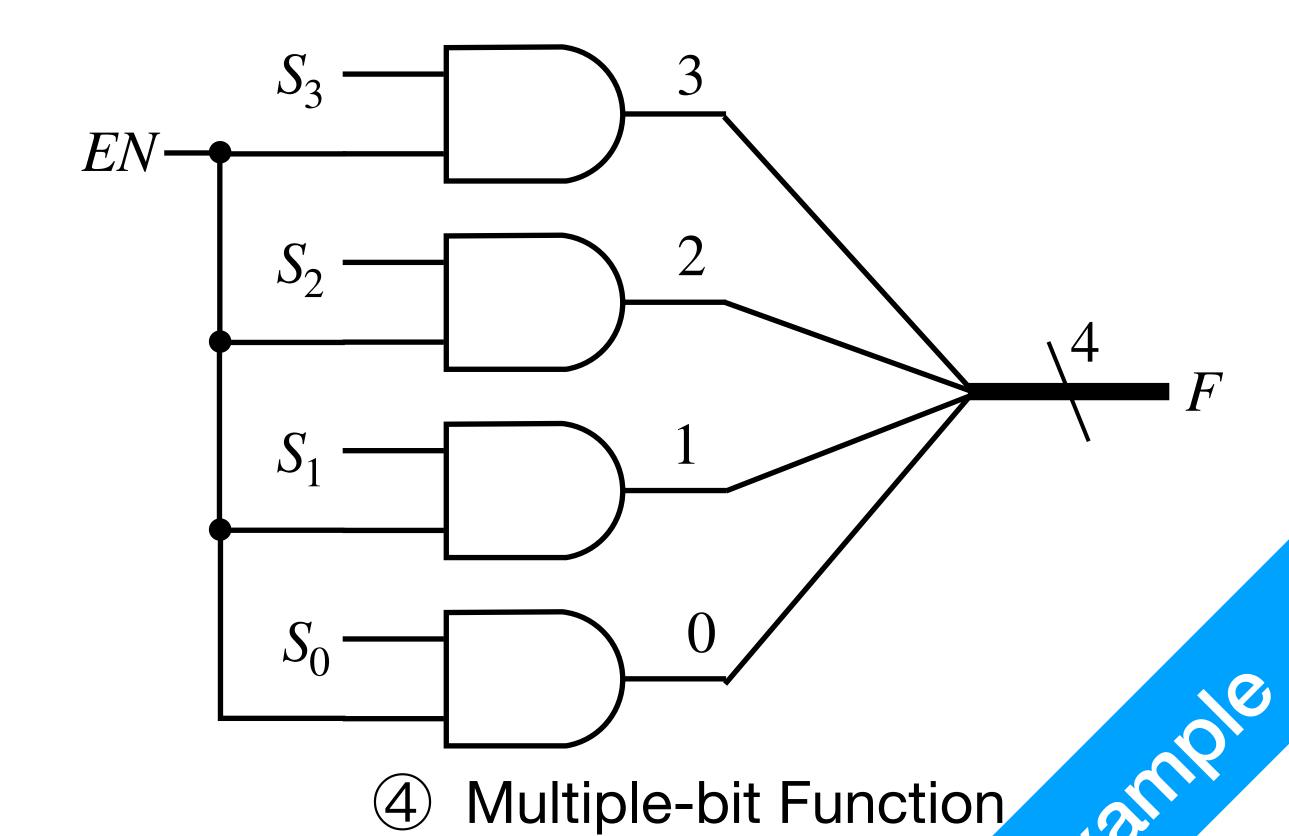

#### 4 Multiple-bit Function

- Functions we've seen so far has only one-bit output: 0/1

- Certain functions may have *n*-bit output

- $F(n-1:0) = (F_{n-1}, F_{n-2}, \dots, F_0)$ , each  $F_i$  is a one-bit function

- Curtain Motor Control Circuit:  $F = (F_{\text{Motor}_1}, F_{\text{Motor}_2}, F_{\text{Light}})$

### Vector Denotation

```

0 — F_3

```

$$1$$

— $F_2$

$$A$$

—  $F_1$

$$\overline{A}$$

————  $F_0$

P1 Elementary Func.

# Vector Denotation

4 Multiple-bit Function

Course

Elementary Func.

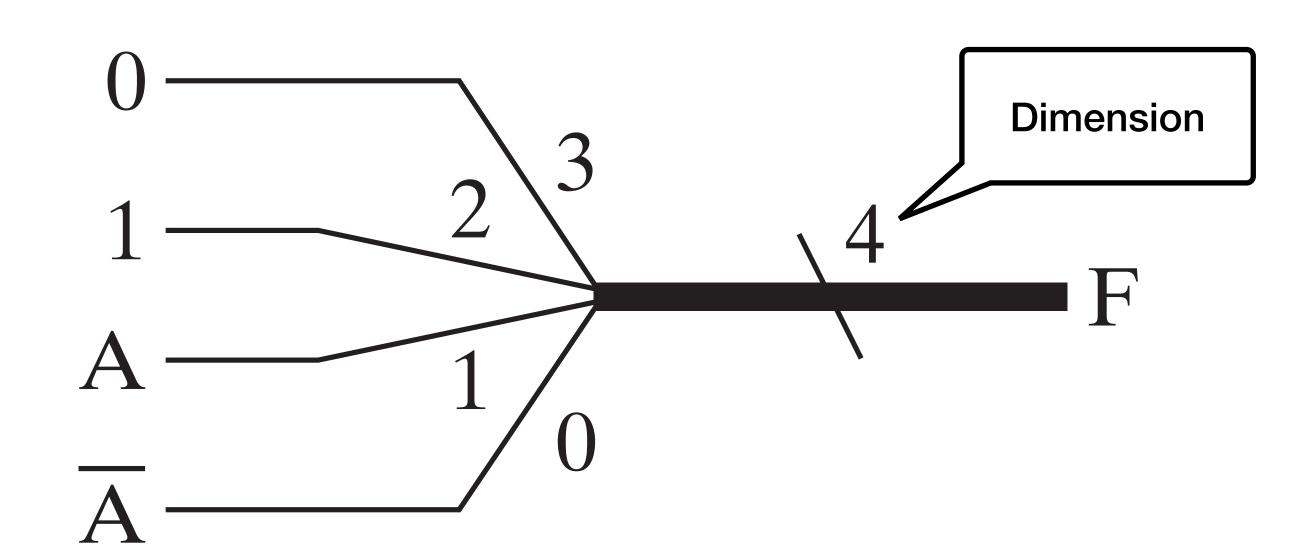

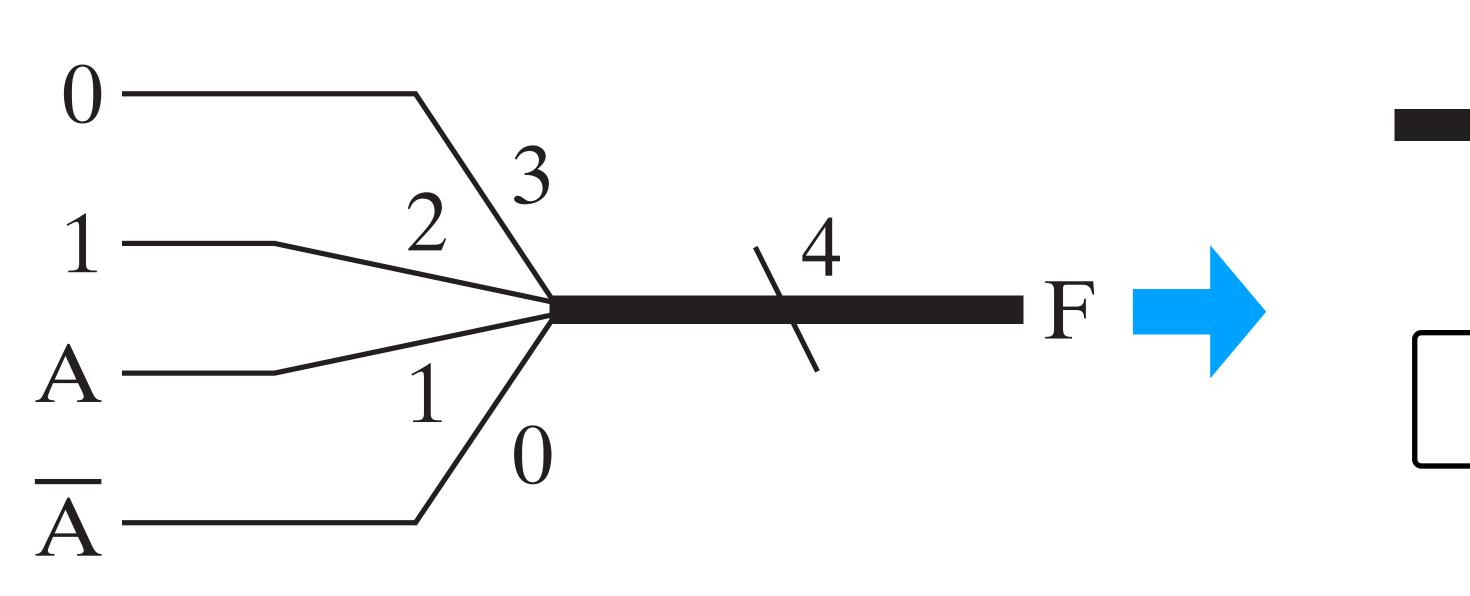

# Taking part of the Vector

4 Multiple-bit Function

**Dimension**

Output:  $(F_3, F_1, F_0)$

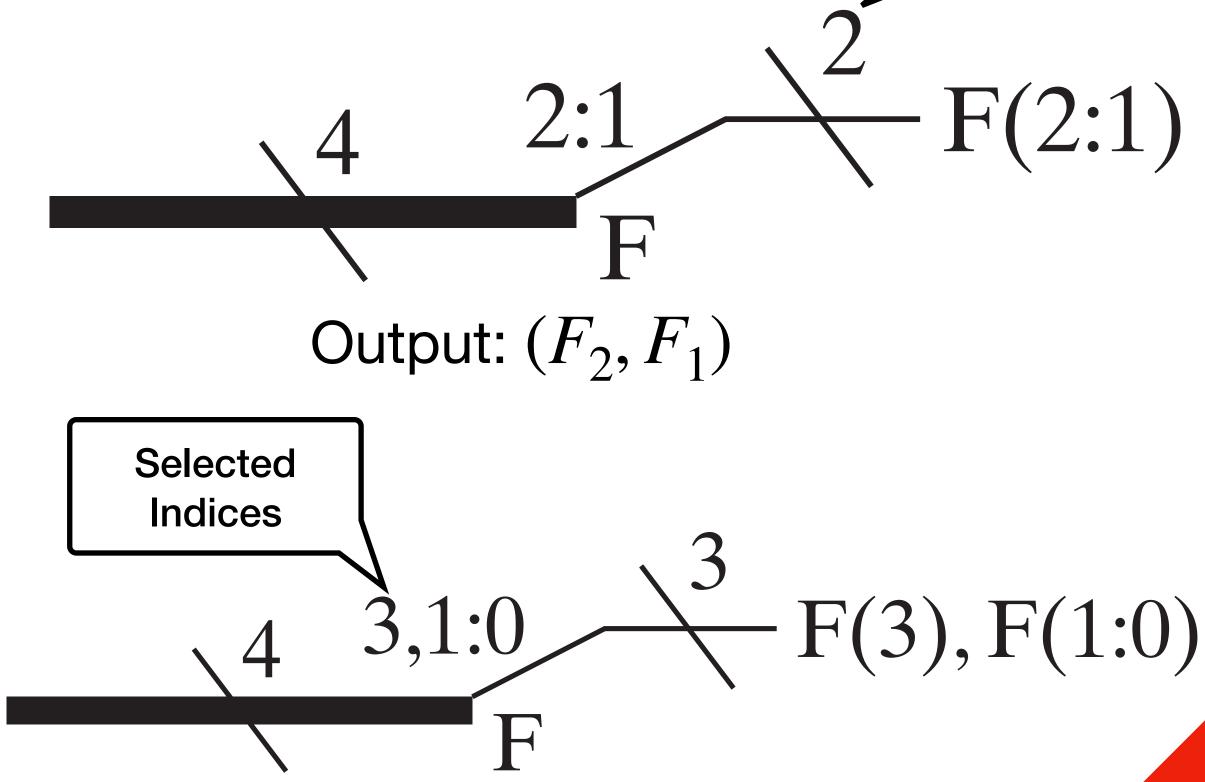

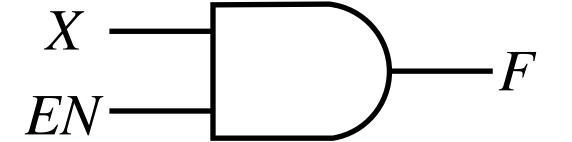

#### **5** Enabler

• Transferring function, but with an additional EN signal acting as switch

| EN | X | F |

|----|---|---|

| 0  |   | 0 |

| 1  | 0 | 0 |

| 1  | 1 | 1 |

Color, Co

#### **5** Enabler

• Transferring function, but with an additional EN signal acting as switch

Color

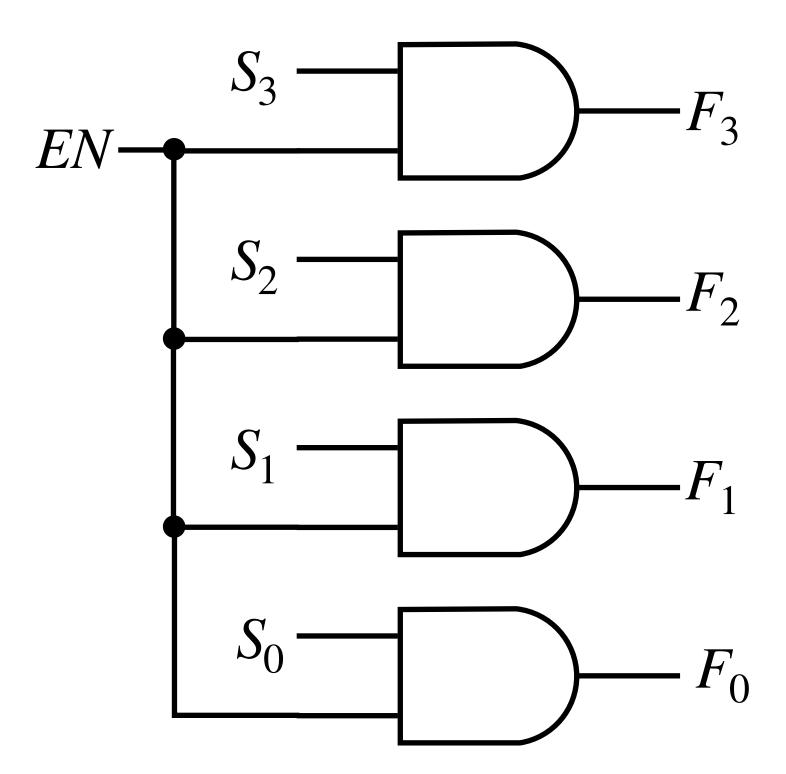

- A building with individual lights F(3:0), and individual switches S(3:0)

- $S_i$  controls  $F_i$

- Master switch: EN

- A building with individual lights F(3:0), and individual switches S(3:0)

- $S_i$  controls  $F_i$

- Master switch: EN

# Summary

- **1** Value-Fixing

- 2 Transferring

- 3 Inverting

- 4 Multiple-bit Function

- **5** Enabler

Simon

# Decoding

n-bit input,  $2^n$ -bit output

### Decoder

- *n*-bit input

- 2<sup>n</sup> different combinations

- Decoder

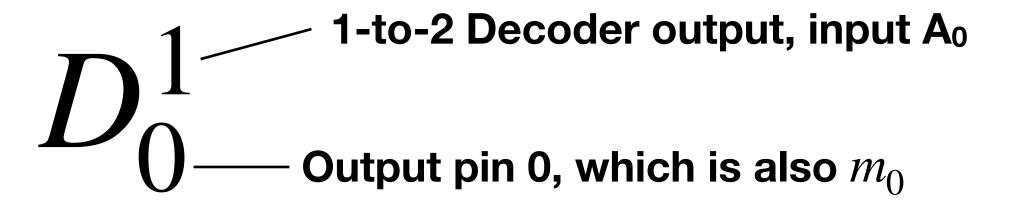

- n-bit input  $(A_0,A_1,\ldots,A_{n-1})$   $2^n$  output  $(D_0,D_1,\ldots,D_{2^n-1})$  each unique input produces a unique output

- Each output port is a minterm ( $D_i = m_i$ )

Decoder

# 1-to-2 Decoder - 1 x NOT Gate

• 1bit input, 2bits output

| Ao | D1 <sub>0</sub> | D <sup>1</sup> <sub>1</sub> |

|----|-----------------|-----------------------------|

| 0  | 1               | 0                           |

| 1  | 0               | 1                           |

$$D_1^1 = m_1(A_0) = A_0$$

$$D_0^1 = m_0(A_0) = \overline{A_0}$$

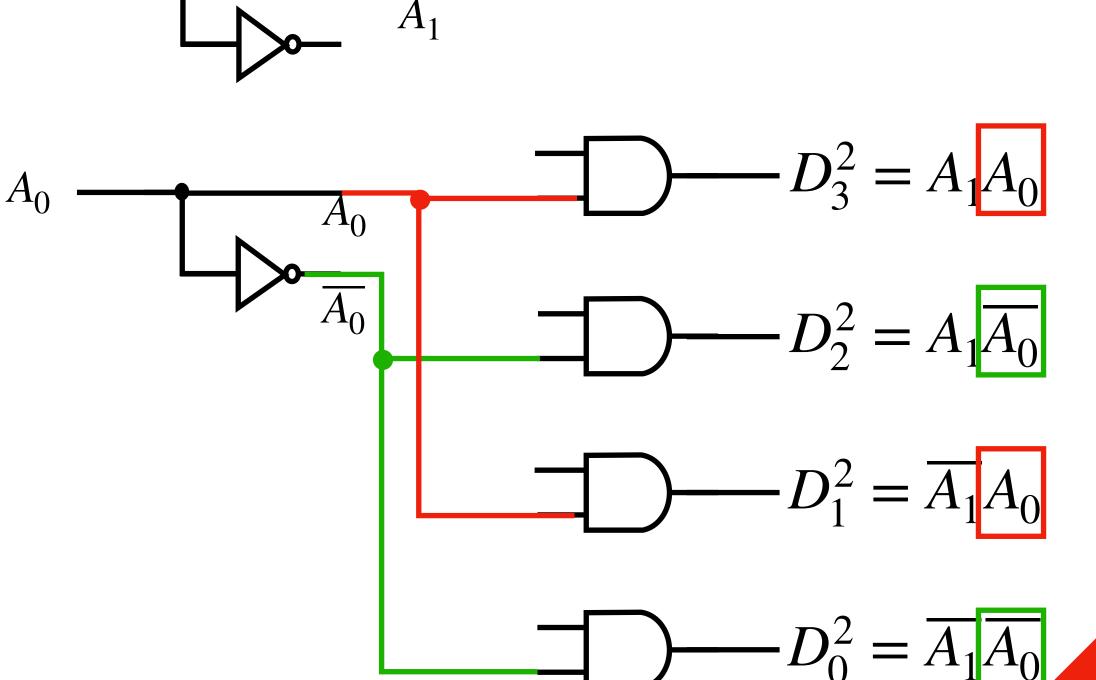

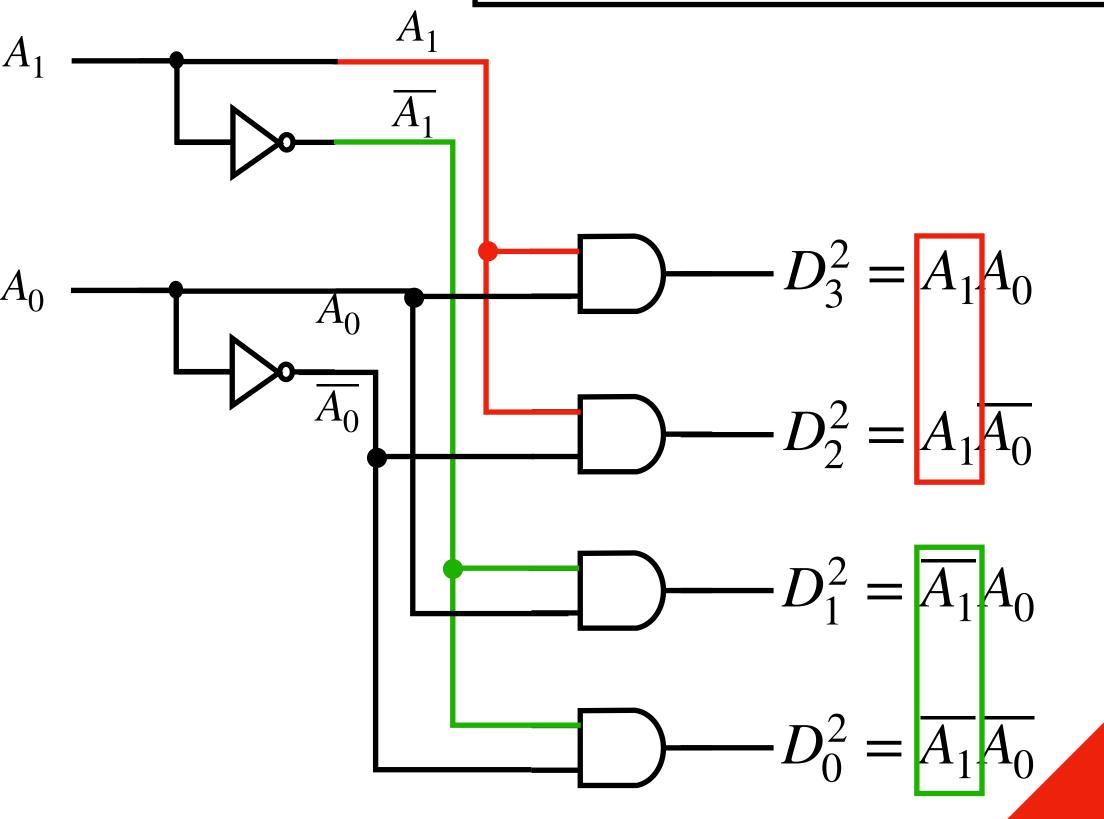

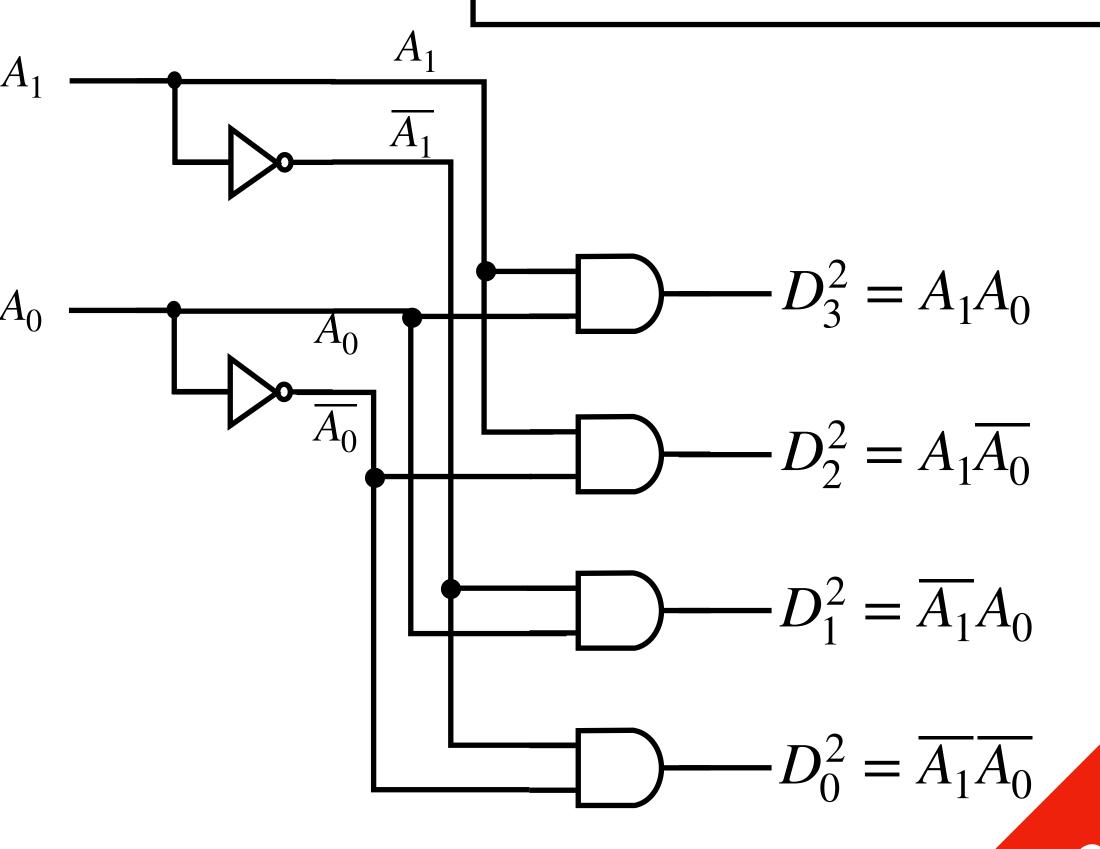

# 2-to-4 Decoder - 2 x 1-to-2 Decoder

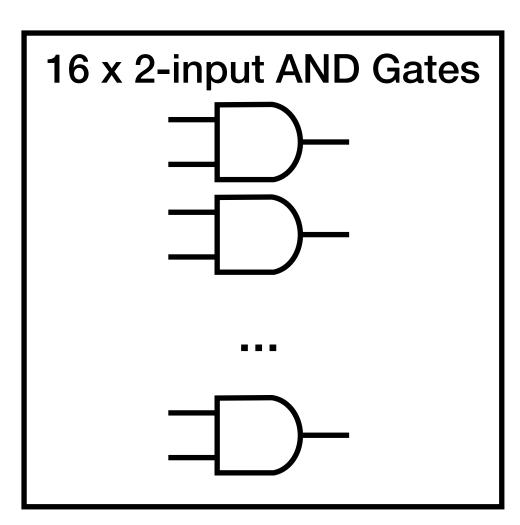

- 4 x 2-input AND Gate

- 2bit input, 4bits output

- $D_i = m_i$

| A <sub>1</sub> | A <sub>0</sub> | D <sub>0</sub> | D <sub>1</sub> | D <sub>2</sub> | D <sub>3</sub> |

|----------------|----------------|----------------|----------------|----------------|----------------|

| 0              | 0              | 1              | 0              | 0              | 0              |

| 0              | 1              | 0              | 1              | 0              | 0              |

| 1              | 0              | 0              | 0              | 1              | 0              |

| 1              | 1              | 0              | 0              | 0              | 1              |

# 2-to-4 Decoder - 2 x 1-to-2 Decoder

- Technology

- 4 x 2-input AND Gate

- 2bit input, 4bits output

- $D_i = m_i$

| A <sub>1</sub> | A <sub>0</sub> | D <sub>0</sub> | D <sub>1</sub> | D <sub>2</sub> | D <sub>3</sub> |

|----------------|----------------|----------------|----------------|----------------|----------------|

| 0              | 0              | 1              | 0              | 0              | 0              |

| 0              | 1              | 0              | 1              | 0              | 0              |

| 1              | 0              | 0              | 0              | 1              | 0              |

| 1              | 1              | 0              | 0              | 0              | 1              |

# 2-to-4 Decoder - 2 x 1-to-2 Decoder

- Technology

- 4 x 2-input AND Gate

- 2bit input, 4bits output

- $D_i = m_i$

| A <sub>1</sub> | A <sub>0</sub> | D <sub>0</sub> | D <sub>1</sub> | D <sub>2</sub> | D <sub>3</sub> |

|----------------|----------------|----------------|----------------|----------------|----------------|

| 0              | 0              | 1              | 0              | 0              | 0              |

| 0              | 1              | 0              | 1              | 0              | 0              |

| 1              | 0              | 0              | 0              | 1              | 0              |

| 1              | 1              | 0              | 0              | 0              | 1              |

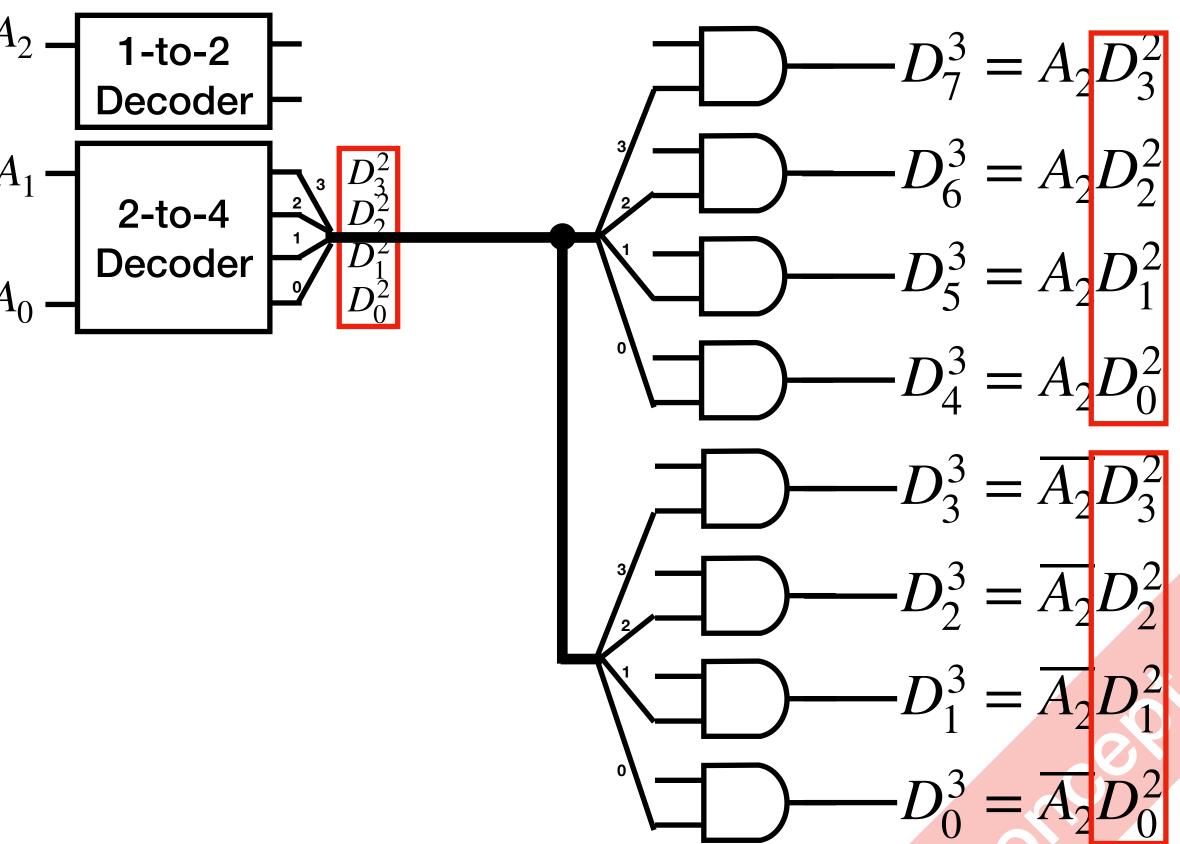

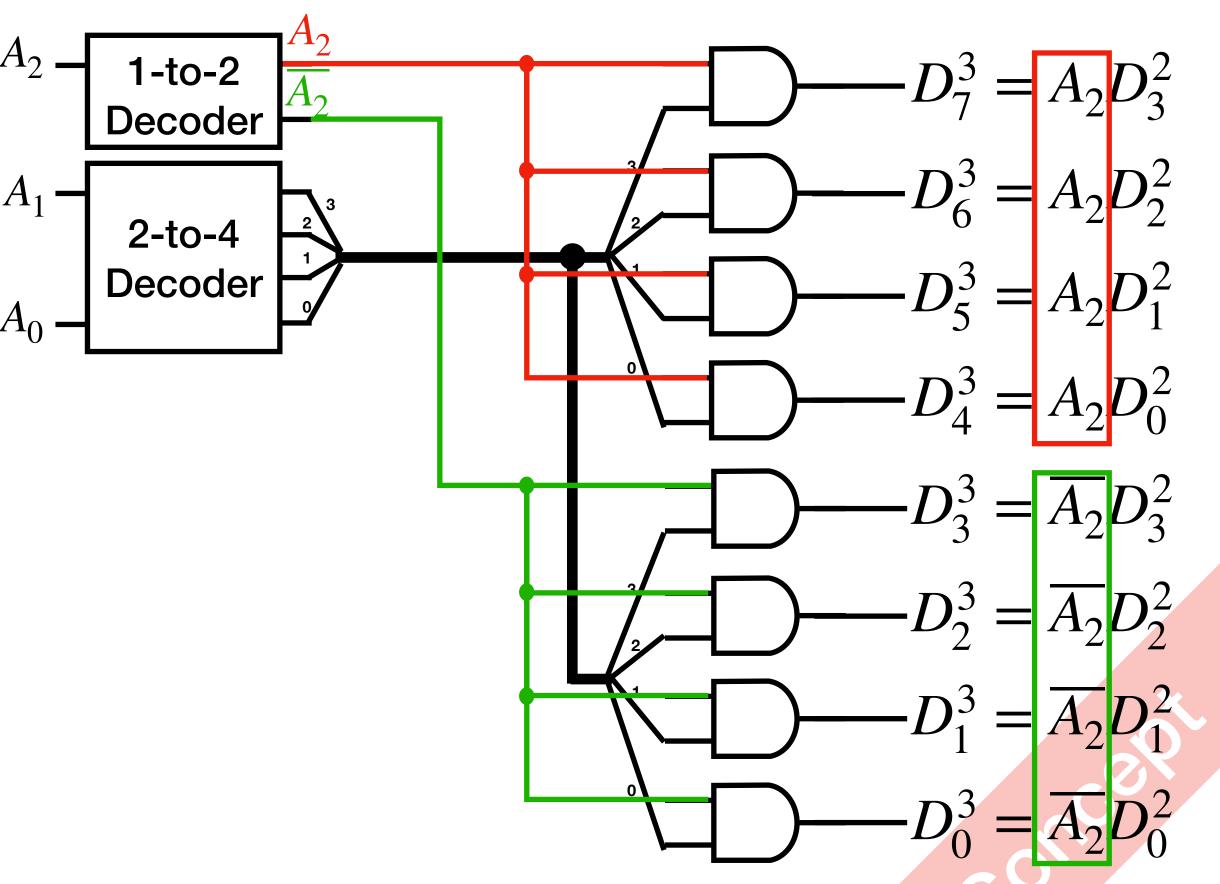

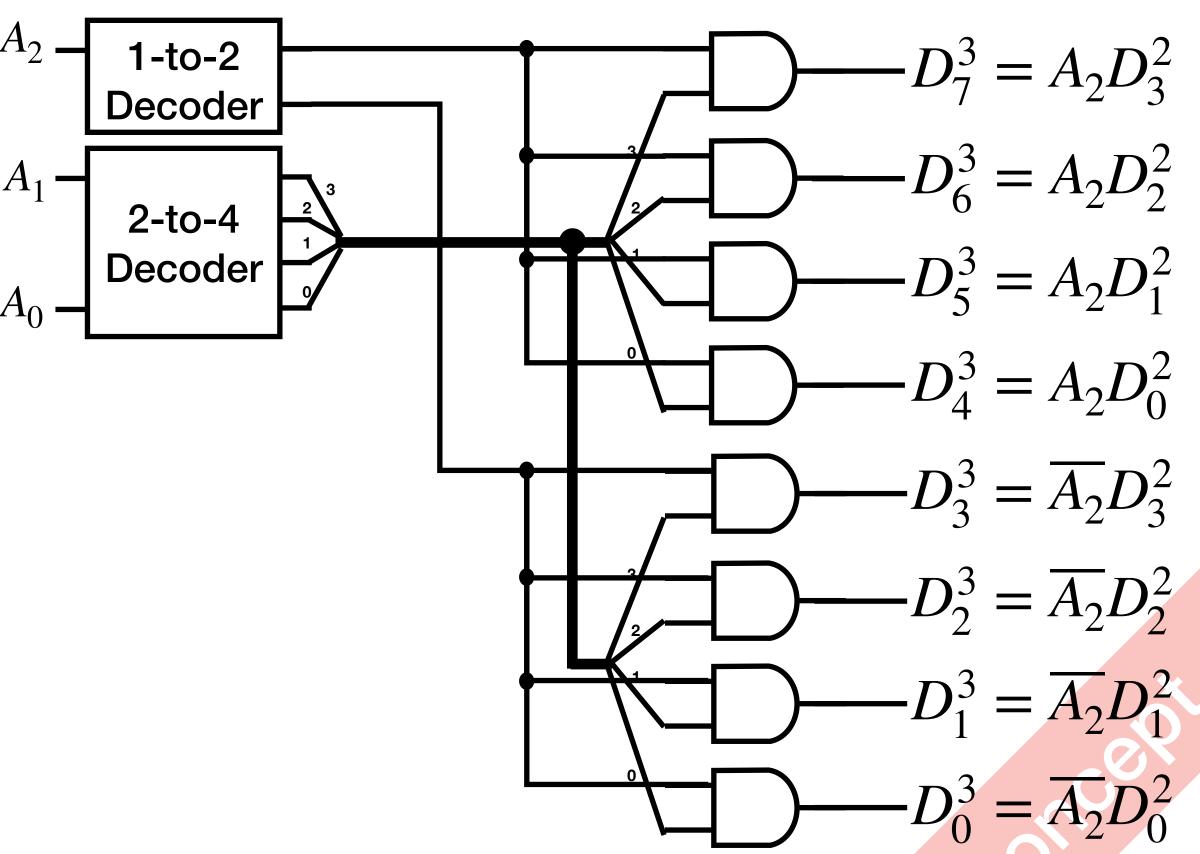

# 3-to-8 Decoder - 1 x 1-to-2 Decoder

- 3bit input, 8bits output

- $D_i = m_i$

| A <sub>2</sub> | A <sub>1</sub> | A <sub>0</sub> | D <sub>0</sub> | D <sub>1</sub> | D <sub>2</sub> | D <sub>3</sub> | D <sub>4</sub> | D <sub>5</sub> | D <sub>6</sub> | D <sub>7</sub> |

|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|

| 0              | 0              | 0              | 1              | 0              | 0              | 0              | 0              | 0              | 0              | 0              |

| 0              | 0              | 1              | 0              | 1              | 0              | 0              | 0              | 0              | 0              | 0              |

| 0              | 1              | 0              | 0              | 0              | 1              | 0              | 0              | 0              | 0              | 0              |

| 0              | 1              | 1              | 0              | 0              | 0              | 1              | 0              | 0              | 0              | 0              |

| 1              | 0              | 0              | 0              | 0              | 0              | 0              | 1              | 0              | 0              | 0              |

| 1              | 0              | 1              | 0              | 0              | 0              | 0              | 0              | 1              | 0              | 0              |

| 1              | 1              | 0              | 0              | 0              | 0              | 0              | 0              | 0              | 1              | 0              |

| 1              | 1              | 1              | 0              | 0              | 0              | 0              | 0              | 0              | 0              | 1              |

- 1 x 2-to-4 Decoder

- 8 x 2-input AND Gate

# 3-to-8 Decoder - 1 x 1-to-2 Decoder

#### Technology

- 1 x 2-to-4 Decoder8 x 2-input AND Gate

• 3bit input, 8bits output

•

$$D_i = m_i$$

| A <sub>2</sub> | A <sub>1</sub> | A <sub>0</sub> | D <sub>0</sub> | D <sub>1</sub> | D <sub>2</sub> | D <sub>3</sub> | D <sub>4</sub> | D <sub>5</sub> | D <sub>6</sub> | D <sub>7</sub> |

|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|

| 0              |                |                |                |                |                |                | 0              |                | 0              | 0              |

| 0              | 0              | 1              | 0              | 1              | 0              | 0              | 0              | 0              | 0              | 0              |

| 0              | 1              | 0              | 0              | 0              | 1              | 0              | 0              | 0              | 0              | 0              |

| 0              | 1              | 1              | 0              | 0              | 0              | 1              | 0              | 0              | 0              | 0              |

| 1              | 0              | 0              | 0              | 0              | 0              | 0              | 1              | 0              | 0              | 0              |

| 1              | 0              | 1              | 0              | 0              | 0              | 0              | 0              | 1              | 0              | 0              |

| 1              | 1              | 0              | 0              | 0              | 0              | 0              | 0              | 0              | 1              | 0              |

| 1              | 1              | 1              | 0              | 0              | 0              | 0              | 0              | 0              | 0              | 1              |

$$D_{0:3}^3 = \overline{A_2} D_{0:3}^2$$

e.g.

$$D_2^3 = m_2(A_2A_1A_0) = \overline{A_2}A_1\overline{A_0}$$

=  $\overline{A_2}(A_1\overline{A_0}) = \overline{A_2}m_2(A_1A_0) = \overline{A_2}D_2^2$

$$D_{4:7}^3 = A_2 D_{0:3}^2$$

e.g.

$$D_7^3 = m_7(A_2A_1A_0) = A_2A_1A_0$$

$$= A_2(A_1A_0) = A_2m_3(A_1A_0) = A_2D_3^2$$

# 3-to-8 Decoder.

- Technology

- 1 x 1-to-2 Decoder

- 1 x 2-to-4 Decoder

- 8 x 2-input AND Gate

• 3bit input, 8bits output

| •              | $D_i$ =        | $= m_i$ |                |                |                |                |                |                |                |                |

|----------------|----------------|---------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|

| A <sub>2</sub> | A <sub>1</sub> | $A_0$   | D <sub>0</sub> | D <sub>1</sub> | D <sub>2</sub> | D <sub>3</sub> | D <sub>4</sub> | D <sub>5</sub> | D <sub>6</sub> | D <sub>7</sub> |

|                | 0              | 0       | 1              | 0              | 0              | 0              | 0              | 0              | 0              | 0              |

|                | 0              | 1       | 0              | 1              | 0              | 0              | 0              | 0              | 0              | 0              |

| U              | 1              | 0       | 0              | 0              | 1              | 0              | 0              | 0              | 0              | 0              |

|                | 1              | 1       | 0              | 0              | 0              | 1              | 0              | 0              | 0              | 0              |

|                | 0              | 0       | 0              | 0              | 0              |                | 1              | 0              | 0              | 0              |

|                | 0              | 1       | 0              | 0              | 0              | 0              | 0              | 1              | 0              | 0              |

|                | 1              | 0       | 0              | 0              | 0              | 0              | 0              | 0              | 1              | 0              |

|                | 1              | 1       | 0              | 0              | 0 0 0          | 0              | 0              | 0              | 0              | 1              |

# 3-to-8 Decoder.

- Technology

- 1 x 1-to-2 Decoder

- 1 x 2-to-4 Decoder

- 8 x 2-input AND Gate

| • | 3bit | input, | 8bits | output |

|---|------|--------|-------|--------|

|---|------|--------|-------|--------|

|                | $D_i$ -        | $= rrl_i$      |                |                |                |                |                |                |                |                |

|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|

| A <sub>2</sub> | A <sub>1</sub> | A <sub>0</sub> | D <sub>0</sub> | D <sub>1</sub> | D <sub>2</sub> | D <sub>3</sub> | D <sub>4</sub> | D <sub>5</sub> | D <sub>6</sub> | D <sub>7</sub> |

|                | 0              | 0              |                | 0              | 0              | 0              | 0              | 0              | 0              | 0              |

| 0              | 0              | 1              | 0              | 1              | 0              | 0              | 0              | 0              | 0              | 0              |

| U              | 1              | 0              |                | 0              | 1              | 0              | 0              | 0              | 0              | 0              |

|                | 1              | 1              | 0              | 0              | 0              | 1              | 0              | 0              | 0              | 0              |

|                | 0              | 0              | 0              | 0              | 0              | 0              | 1              | 0              | 0              | 0              |

| 4              | 0              | 1              | 0              | 0              | 0              | 0              | 0              | 1              | 0              | 0              |

|                | 1              | 0              | 0              | 0              | 0              | 0              | 0              | 0              | 1              | 0              |

|                | 1              | 1              | 0              | 0              | 0              | 0              | 0              | 0              | 0              | 1              |

# 3-to-8 Decoder.

- Technology

- 1 x 1-to-2 Decoder

- 1 x 2-to-4 Decoder

- 8 x 2-input AND Gate

• 3bit input, 8bits output

|                | $D_i$ -        | $= rrl_i$      |                |                |                |                |                |                |                |                |

|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|

| A <sub>2</sub> | A <sub>1</sub> | A <sub>0</sub> | D <sub>0</sub> | D <sub>1</sub> | D <sub>2</sub> | D <sub>3</sub> | D <sub>4</sub> | D <sub>5</sub> | D <sub>6</sub> | D <sub>7</sub> |

|                | 0              | 0              |                | 0              | 0              | 0              | 0              | 0              | 0              | 0              |

| 0              | 0              | 1              | 0              | 1              | 0              | 0              | 0              | 0              | 0              | 0              |

| U              | 1              | 0              |                | 0              | 1              | 0              | 0              | 0              | 0              | 0              |

|                | 1              | 1              | 0              | 0              | 0              | 1              | 0              | 0              | 0              | 0              |

|                | 0              | 0              | 0              | 0              | 0              | 0              | 1              | 0              | 0              | 0              |

| 4              | 0              | 1              | 0              | 0              | 0              | 0              | 0              | 1              | 0              | 0              |

|                | 1              | 0              | 0              | 0              | 0              | 0              | 0              | 0              | 1              | 0              |

|                | 1              | 1              | 0              | 0              | 0              | 0              | 0              | 0              | 0              | 1              |

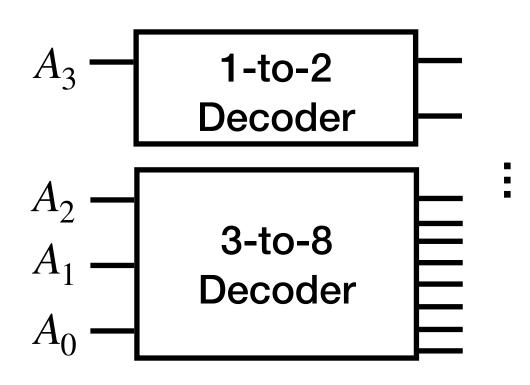

**Incremental Design**

• 4bit input, 16bits output

•

$$D_i = m_i$$

$$D_{0:7}^4 = \overline{A_3} D_{0:7}^3$$

$$D_{0:7}^4 = \overline{A_3}D_{0:7}^3 \quad D_{8:15}^4 = A_3D_{0:7}^3$$

Technology

1 x 3-to-8 Decoder

• 16 x 2-input AND Gate

| <b>A</b> <sub>3</sub> | A <sub>2</sub> | A <sub>1</sub> | A <sub>0</sub> | $D_0$ | D <sub>1</sub> | D <sub>2</sub> | D <sub>3</sub> | D <sub>4</sub> | D <sub>5</sub> | D <sub>6</sub> | D <sub>7</sub> |

|-----------------------|----------------|----------------|----------------|-------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|

|                       | 0              | 0              | 0              | 1     | 0              | 0              | 0              | 0              | 0              | 0              | 0              |

|                       | 0              | 0              | 1              |       |                | 0              |                |                |                |                | 0              |

|                       | 0              | 1              | 0              |       |                | 1              |                |                |                |                | 0              |

|                       | 0              | 1              | 1              | 0     | 0              | 0              | 1              | 0              | 0              | 0              | 0              |

| U                     | 1              | 0              | 0              | 0     | 0              | 0              | 0              | 1              | 0              | 0              | 0              |

|                       | 1              | 0              | 1              | 0     | 0              | 0              | 0              | 0              | 1              | 0              | 0              |

|                       | 1              | 1              | 0              | 0     | 0              | 0              | 0              | 0              | 0              | 1              | 0              |

|                       | 1              | 1              | 1              | 0     | 0              | 0              | 0              | 0              | 0              | 0              | 1              |

| <b>A</b> <sub>3</sub> | A <sub>2</sub> | A <sub>1</sub> | A <sub>0</sub> | D <sub>8</sub> | D <sub>9</sub> | D <sub>10</sub> | D <sub>11</sub> | D <sub>12</sub> | <b>D</b> <sub>13</sub> | D <sub>14</sub> | <b>D</b> <sub>15</sub> |

|-----------------------|----------------|----------------|----------------|----------------|----------------|-----------------|-----------------|-----------------|------------------------|-----------------|------------------------|

|                       | 0              |                | 0              | 1              | 0              | 0               | 0               | 0               |                        | 0               | 0                      |

|                       | 0              | 0              | 1              | 0              | 1              | 0               | 0               | 0               | 0                      | 0               | 0                      |

|                       | 0              | 1              | 0              |                |                |                 |                 | 0               |                        | 0               | 0                      |

|                       | 0              | 1              | 1              | 0              |                |                 |                 | 0               |                        |                 | 0                      |

|                       | 1              | 0              | 0              | 0              | 0              | 0               | 0               | 1               | 0                      | 0               | 0                      |

|                       | 1              | 0              | 1              |                | 0              | 0               |                 | 0               |                        |                 | 0                      |

|                       | 1              | 1              | 0              | 0              | 0              | 0               | 0               | 0               | 0                      | 1               | 0                      |

|                       | 1              | 1              | 1              | 0              | 0              | 0               | 0               | 0               | 0                      | 0               | 1                      |

**Incremental Design**

- 4bit input, 16bits output

- $D_i = m_i$

- 1 x 3-to-8 Decoder

- 16 x 2-input AND Gate

$$D_{8:15}^4 = A_3 D_{0:7}^3$$

$$D_{0:7}^4 = \overline{A_3} D_{0:7}^3$$

Technology

16 x 2-input AND Gate

#### **Recursive Design**

• 4bit input, 16bits output

•

$$D_i = m_i$$

$$D_{0:7}^4 = \overline{A_3} D_{0:7}^3$$

$$D_{0:7}^4 = \overline{A_3}D_{0:7}^3 \quad D_{8:15}^4 = A_3D_{0:7}^3$$

| <b>A</b> <sub>3</sub> | A <sub>2</sub> | A <sub>1</sub> | A <sub>0</sub> | $D_0$ | D <sub>1</sub> | D <sub>2</sub> | D <sub>3</sub> | D <sub>4</sub> | D <sub>5</sub> | D <sub>6</sub> | D <sub>7</sub> |

|-----------------------|----------------|----------------|----------------|-------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|

|                       |                | 0              | 0              | 1     | 0              | 0              | 0              | 0              | 0              | 0              | 0              |

|                       |                | 0              | 1              | 0     | 1              | 0              | 0              | 0              | 0              | 0              | 0              |

|                       | U              | 1              | 0              | 0     | 0              | 1              | 0              | 0              | 0              | 0              | 0              |

|                       |                | 1              | 1              | 0     | 0              | 0              | 1              | 0              | 0              | 0              | 0              |

| U                     |                | 0              |                |       |                |                |                | 1              |                | 0              | 0              |

|                       | 4              | 0              |                |       |                |                |                | 0              |                |                |                |

|                       |                | 1              | 0              | 0     | 0              | 0              | 0              | 0              | 0              | 1              | 0              |

|                       |                | 1              | 1              | 0     | 0              | 0              | 0              | 0              | 0              | 0              | 1              |

| <b>A</b> <sub>3</sub> | A <sub>2</sub> | A <sub>1</sub> | A <sub>0</sub> | D <sub>8</sub> | D <sub>9</sub> | D <sub>10</sub> | D <sub>11</sub> | D <sub>12</sub> | <b>D</b> <sub>13</sub> | <b>D</b> <sub>14</sub> | <b>D</b> <sub>15</sub> |

|-----------------------|----------------|----------------|----------------|----------------|----------------|-----------------|-----------------|-----------------|------------------------|------------------------|------------------------|

|                       |                | 0              | 0              | 1              | 0              | 0               | 0               | 0               | 0                      | 0                      | 0                      |

|                       |                | 0              | 1              | 0              | 1              | 0               | 0               | 0               | 0                      | 0                      | 0                      |

|                       | U              | 1              |                |                |                | 1               |                 |                 |                        |                        | 0                      |

| 4                     |                | 1              | 1              | 0              | 0              | 0               | 1               | 0               | 0                      | 0                      | 0                      |

|                       |                | 0              | 0              | 0              | 0              | 0               | 0               | 1               | 0                      | 0                      | 0                      |

|                       | 4              | 0              | 1              | 0              | 0              | 0               | 0               | 0               | 1                      | 0                      | 0                      |

|                       |                | 1              | 0              | 0              | 0              | 0               | 0               | 0               | 0                      | 1                      | 0                      |

|                       |                | 1              | 1              | 0              | 0              | 0               | 0               | 0               | 0                      | 0                      | 1                      |

Technology

16 x 2-input AND Gate

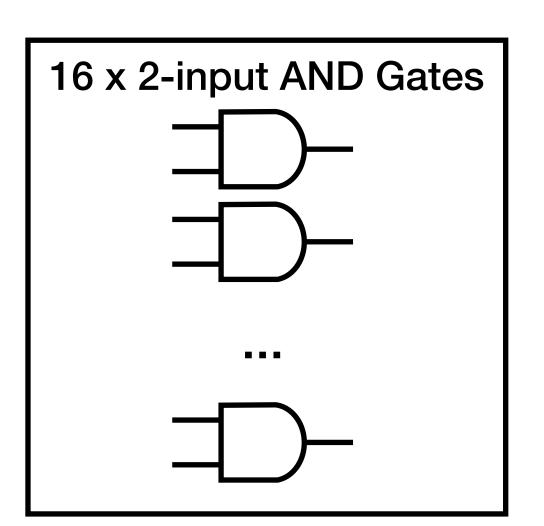

#### **Recursive Design**

• 4bit input, 16bits output

•

$$D_i = m_i$$

$$D_{0:7}^4 = \overline{A_3}D_{0:7}^3 \quad D_{8:15}^4 = A_3D_{0:7}^3$$

$$\begin{array}{|c|c|c|}\hline \text{16 x 2-input AND Gates} \\ \hline \Box - \\ \hline \Box - \\ \hline \end{array} \qquad \begin{array}{|c|c|c|}\hline D_{12:15}^4 = A_3 A_2 D^2\\ \hline D_{8:11}^4 = A_3 \overline{A_2} D^2\\ \hline D_{4:7}^4 = \overline{A_3} A_2 D^2\\ \hline D_{0:3}^4 = \overline{A_3} \overline{A_2} D^2\\ \end{array}$$

**Recursive Design**

- 4bit input, 16bits output

- $D_i = m_i$

$$D_{8:15}^{4} = A_3 D_{0:7}^3$$

$$D_{0:7}^{4} = \overline{A_3} D_{0:7}^3$$

#### Technology

- 16 x 2-input AND Gate

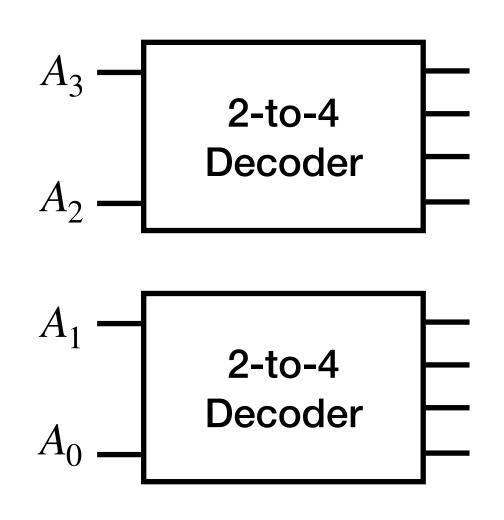

# 4-to-16 Decoder Technology 2 x 2-to-4 Decoder

16 x 2-input AND Gate

#### **Recursive Design**

- 4bit input, 16bits output

- $D_i = m_i$

$$D^4 = D_{0:15}^4 = [\overline{A_3}D_{0:7}^3; A_3D_{0:7}^3] = [\overline{A_3}D^3; A_3D^3]$$

**Bracket: concatenation of vectors**

# 4-to-16 Decoder Technology 2 x 2-to-4 Decoder

16 x 2-input AND Gate

#### **Recursive Design**

- 4bit input, 16bits output

- $D_i = m_i$

$$D^4 = [\overline{A_3}D^3; A_3D^3]$$

**P2** Decoder

# 4-to-16 Decoder 2 x 2-to-4 Decoder

Technology

16 x 2-input AND Gate

#### **Recursive Design**

• 4bit input, 16bits output

$$D^4 = [\overline{A_3}D^3; A_3D^3]$$

•

$$D_i = m_i$$

$$D^{3} = \begin{bmatrix} \overline{A_{2}}D_{0}^{2} \\ \overline{A_{2}}D_{1}^{2} \\ \overline{A_{2}}D_{2}^{2} \\ \overline{A_{2}}D_{3}^{2} \end{bmatrix}; \begin{bmatrix} A_{2}D_{0}^{2} \\ A_{2}D_{1}^{2} \\ A_{2}D_{2}^{2} \\ A_{2}D_{3}^{2} \end{bmatrix}] = [\overline{A_{2}} \begin{bmatrix} D_{0}^{2} \\ D_{1}^{2} \\ D_{2}^{2} \\ D_{3}^{2} \end{bmatrix}; A_{2} \begin{bmatrix} D_{0}^{2} \\ D_{1}^{2} \\ D_{2}^{2} \\ D_{3}^{2} \end{bmatrix}] = [\overline{A_{2}}D^{2}; A_{2}D^{2}]$$

#### **Recursive Design**

$D^4 = [\overline{A_3}D^3; A_3D^3]$

- 4bit input, 16bits output

- $D_i = m_i$

# 4-to-16 Decoder 2 x 2-to-4 Decoder

#### Technology

- 16 x 2-input AND Gate

$$D^3 = [\overline{A_2}D^2; A_2D^2]$$

**Recursive Design**

- 4bit input, 16bits output

- $D_i = m_i$

$$D^3 = [\overline{A_2}D^2; A_2D^2]$$

$$D^{4} = [\overline{A_{3}}D^{3}; A_{3}D^{3}] = [\overline{A_{3}}[\overline{A_{2}}D^{2}; A_{2}D^{2}]; A_{3}[\overline{A_{2}}D^{2}; A_{2}D^{2}]]$$

=

$$[\overline{A_3}\overline{A_2}D^2; \overline{A_3}A_2D^2]; [A_3\overline{A_2}D^2; A_3A_2D^2]]$$

=

$$[\overline{A_3}\overline{A_2}D^2; \overline{A_3}A_2D^2; A_3\overline{A_2}D^2; A_3A_2D^2]$$

$$= [\overline{A_3}\overline{A_2}; \overline{A_3}A_2; A_3\overline{A_2}; A_3\overline{A_2}; A_3A_2]D^2$$

Technology

16 x 2-input AND Gate

# Summary

- What is a decoder

- Truth table of a decoder

- Implementation of 1-to-2, 2-to-4, *n*-to-2<sup>n</sup> decoder

- Incremental design

- Recursive design

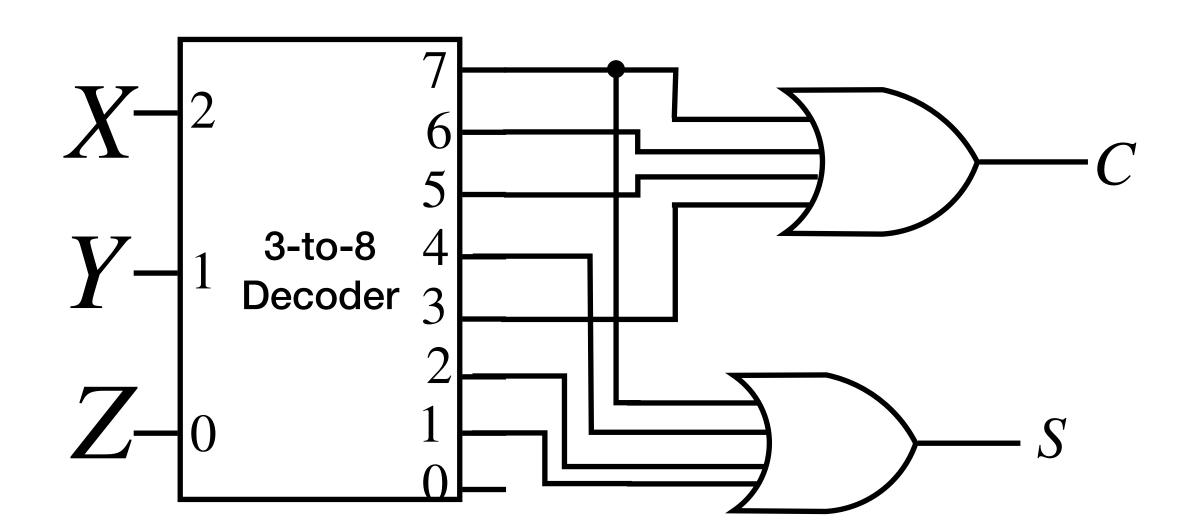

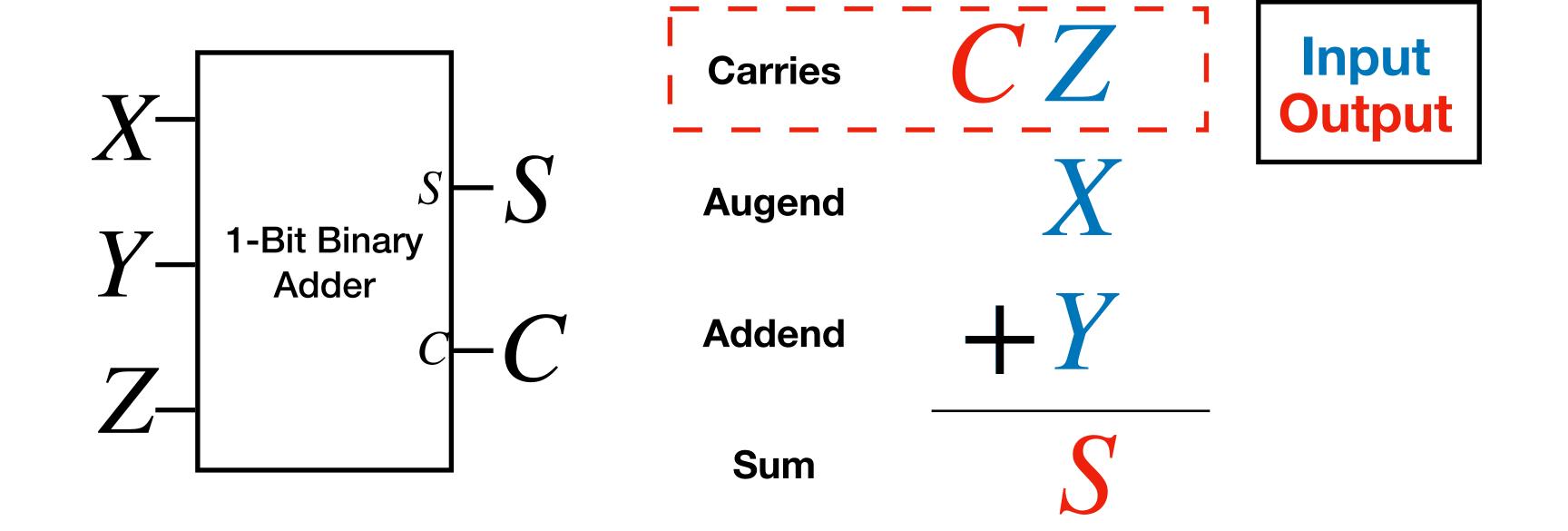

# 1-bit Binary Adder

Using decoder

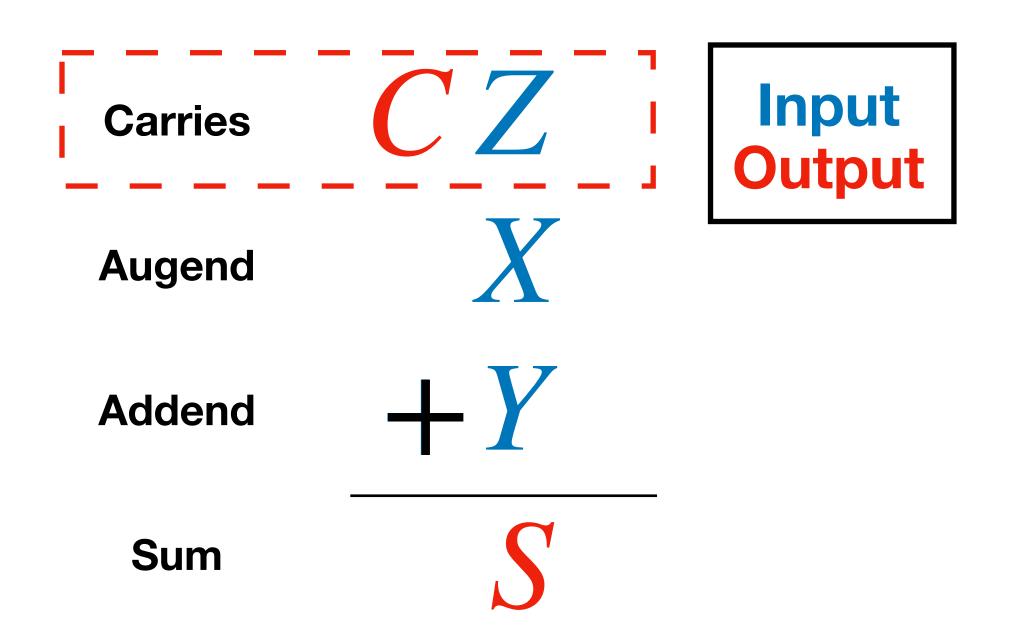

# Binary Addition

Carries

$$Z$$

$11010$

Augend  $X$   $01101$

Addend  $Y$   $+00101$

Sum  $10010$

# 1-bit Binary Adder

- Binary Adder

- Logical functional block that performs addition

- 1-Bit Binary Adder: smallest building block of a multi-bit adder

- Inputs

Augend: X; Addend: Y; Previous Carry: Z

Outputs

Sum bit: S; next carry: C

# 1. Specification

# 2. Formulation

| X | Y | Z | S | C |

|---|---|---|---|---|

| 0 | 0 | 0 |   |   |

| 0 | 0 | 1 |   |   |

| 0 | 1 | 0 |   |   |

| 0 | 1 | 1 |   |   |

| 1 | 0 | 0 |   |   |

| 1 | 0 | 1 |   |   |

| 1 | 1 | 0 |   |   |

| 1 | 1 | 1 |   |   |

# 2. Formulation

| X | Y | Z | C | S |

|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 0 | 1 |

| 0 | 1 | 0 | 0 | 1 |

| 0 | 1 | 1 | 1 | 0 |

| 1 | 0 | 0 | 0 | 1 |

| 1 | 0 | 1 | 1 | 0 |

| 1 | 1 | 0 | 1 | 0 |

| 1 | 1 | 1 | 1 | 1 |

## 2. Formulation

| X | Y | Z | C | S |

|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 0 | 1 |

| 0 | 1 | 0 | 0 | 1 |

| 0 | 1 | 1 | 1 | 0 |

| 1 | 0 | 0 | 0 | 1 |

| 1 | 0 | 1 | 1 | 0 |

| 1 | 1 | 0 | 1 | 0 |

| 1 | 1 | 1 | 1 | 1 |

#### **Sum of Minterms**

$$C(X, Y, Z) = \Sigma m(3,5,6,7)$$

$$S(X, Y, Z) = \Sigma m(1, 2, 4, 7)$$

# 3. Optimisation

| X | Y | Z | C | S |

|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 0 | 1 |

| 0 | 1 | 0 | 0 | 1 |

| 0 | 1 | 1 | 1 | 0 |

| 1 | 0 | 0 | 0 | 1 |

| 1 | 0 | 1 | 1 | 0 |

| 1 | 1 | 0 | 1 | 0 |

| 1 | 1 | 1 | 1 | 1 |

#### **Sum of Minterms**

$$C(X, Y, Z) = \Sigma m(3,5,6,7)$$

$$S(X, Y, Z) = \sum m(1, 2, 4, 7)$$

We can use decoders to implement the adder!

# 4. Technology Mapping : 1 x 3-to-8 OR Gates

Technology

#### **Sum of Minterms**

$$C(X, Y, Z) = \Sigma m(3,5,6,7)$$

$$S(X, Y, Z) = \sum m(1, 2, 4, 7)$$