# CSCI 150 Introduction to Digital and Computer System Design Lecture 3: Combinational Logic Design II

Jetic Gū

#### Overview

- Focus: Methodology

- Architecture: Combinatory Logical Circuits

- Textbook v4: Ch3 3.1, 3.2, 3.3; v5: Ch3 3.1, 3.2

- Core Ideas:

- 1. BCD-to-Seven-Segment Decoder

- 2. 4-bit Equity Comparator

- 3. Technology Mapping

#### Systematic Design Procedures

- **Specification**: Write a specification for the circuit

- 2. **Formulation**: Derive relationship between inputs and outputs of the system e.g. using truth table or Boolean expressions

- 3. **Optimisation**: Apply optimisation, minimise the number of logic gates and literals required

- 4. **Technology Mapping**: Transform design to new diagram using available implementation technology

- 5. **Verification**: Verify the correctness of the final design in meeting the specifications

# BCD-to-Seven-Segment Decoder

Ah, not again

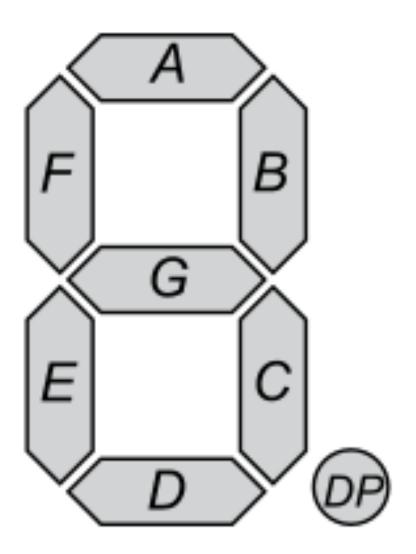

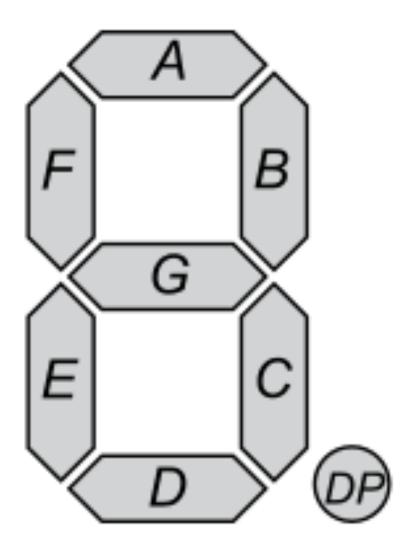

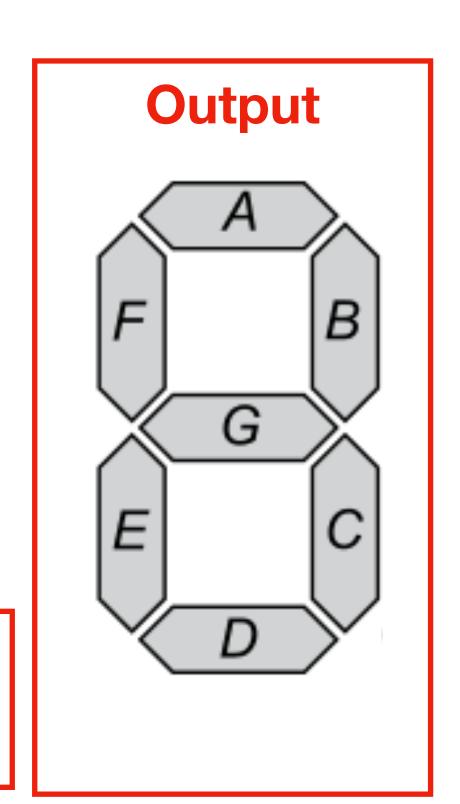

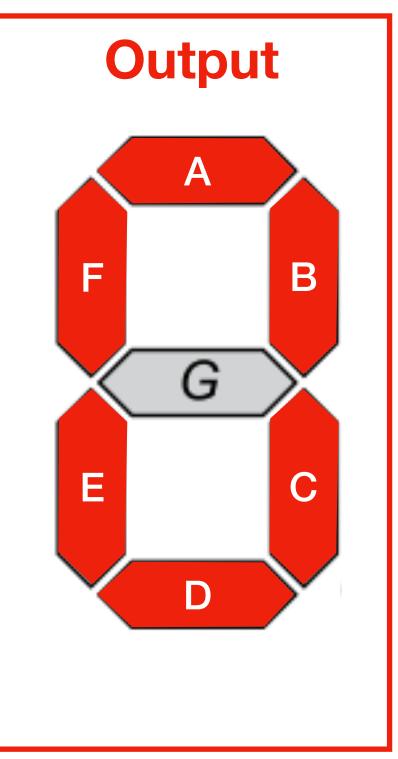

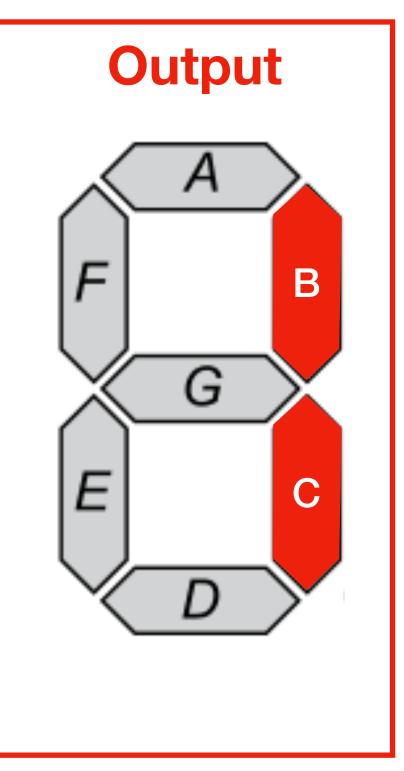

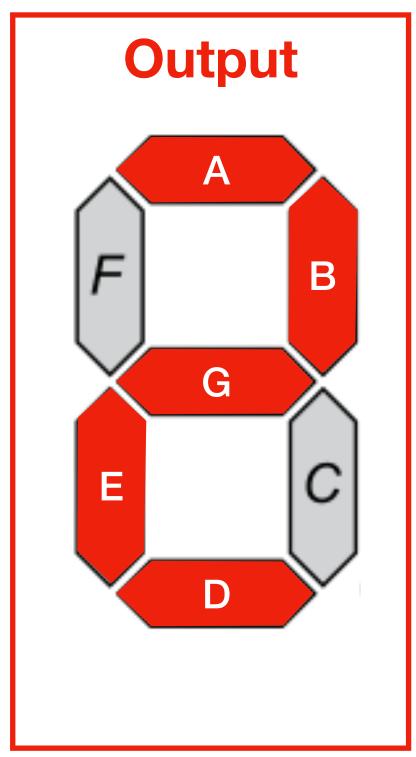

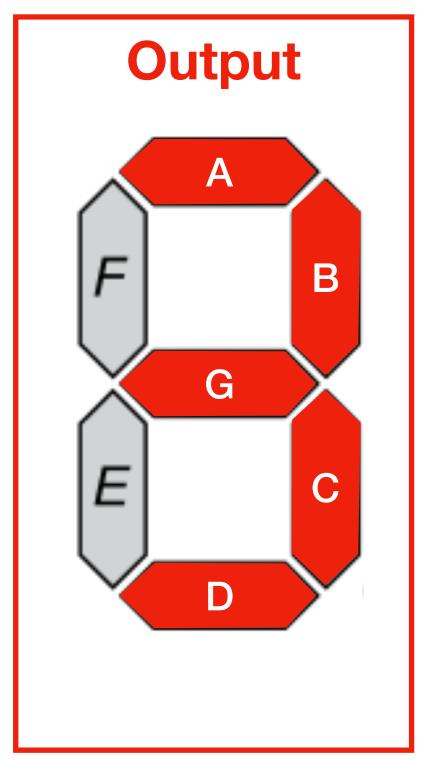

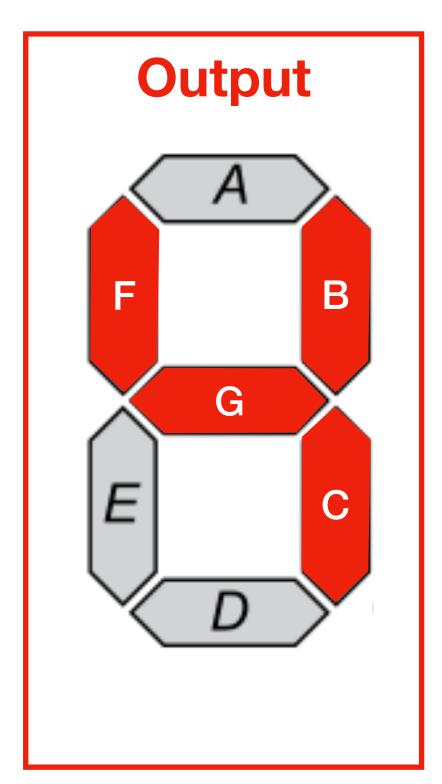

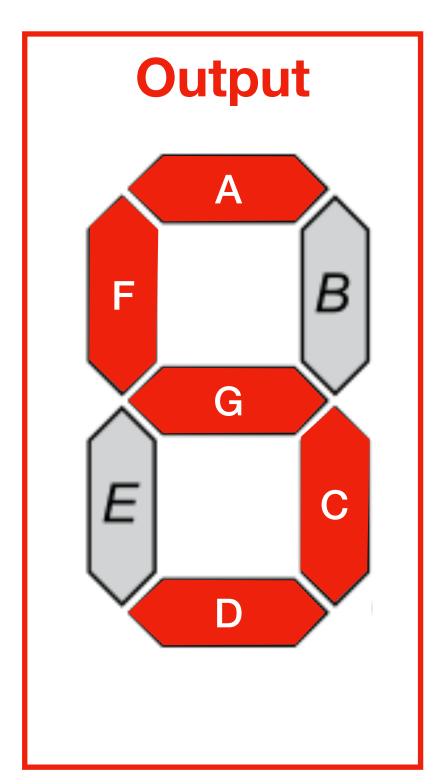

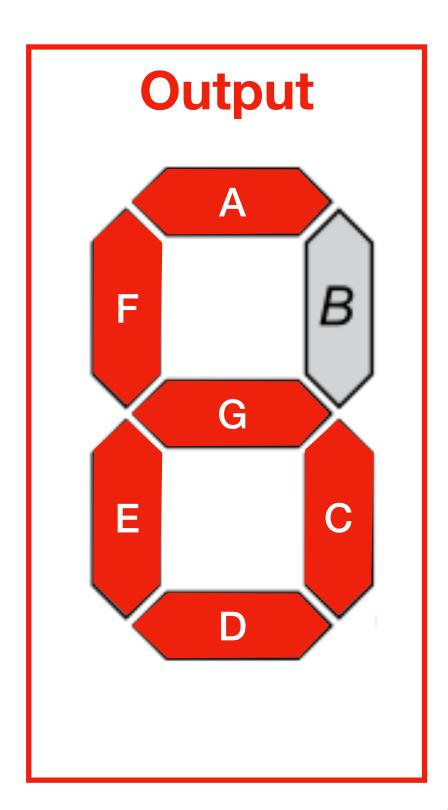

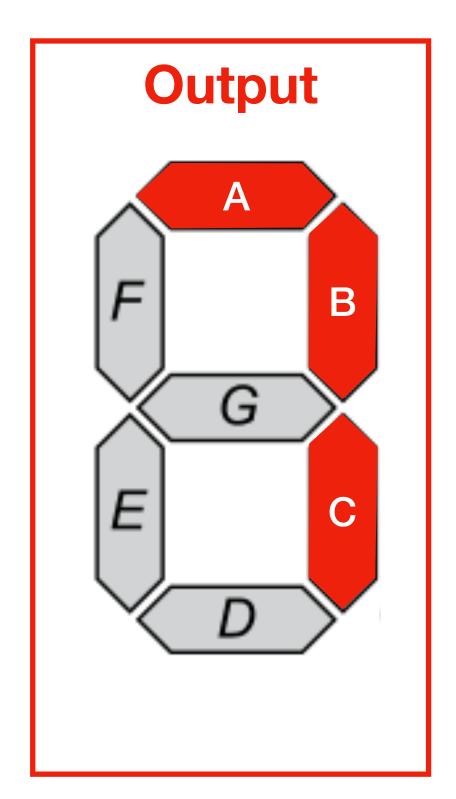

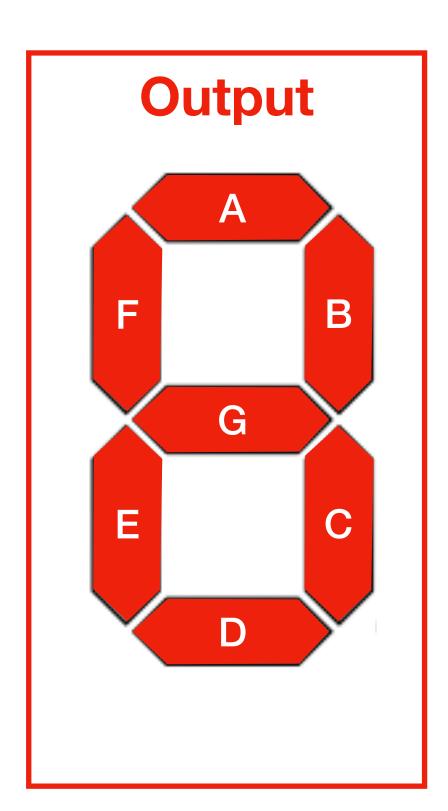

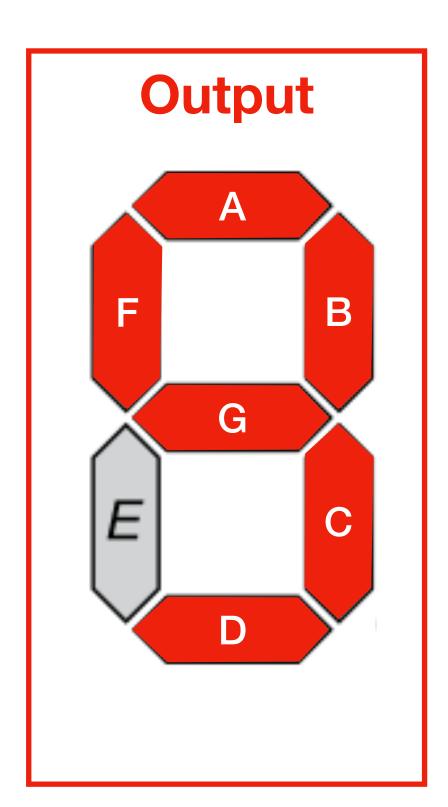

#### LED Seven Segment Display

- LED: Light-Emitting Diodes

- A single digit display takes 7bit inputs (and an optional one for decimal point)

#### BCD to 7 Segment Display(s)

- BCD: Each digit is represented using 4bit binary int

- BCD-to-7-segment decoder A Combinational circuit that

- takes a decimal digit in BCD (4bit int A, B, C, D); and

- generates the appropriate control signals for the display unit (a, b, c, d, e, f, g)

#### 1. Specification

- BCD: Each digit is represented using 4bit binary int

- BCD-to-7-segment decoder

A Combinational circuit that

- Input takes a decimal digit in BCD (4bit int A, B, C, D); and

• generates the appropriate control signals for the display unit (a,b,c,d,e,f,g)

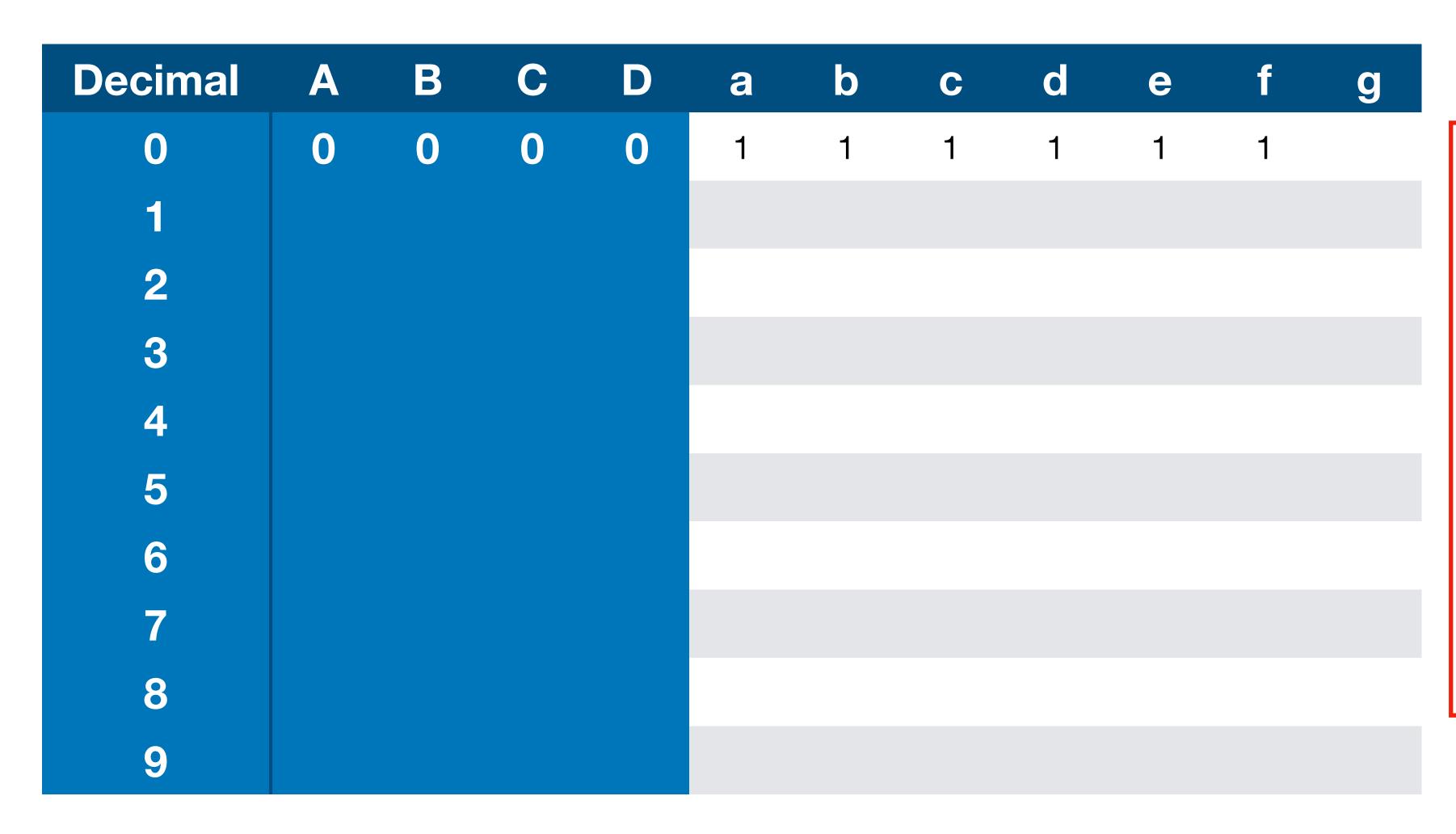

#### 2. Formulation

Silve

#### 2. Formulation

| Decimal | A | В | C | D | a | b | C | d | е | f | g |

|---------|---|---|---|---|---|---|---|---|---|---|---|

| 0       | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 |   |

| 1       | 0 | 0 | 0 | 1 |   | 1 | 1 |   |   |   |   |

| 2       |   |   |   |   |   |   |   |   |   |   |   |

| 3       |   |   |   |   |   |   |   |   |   |   |   |

| 4       |   |   |   |   |   |   |   |   |   |   |   |

| 5       |   |   |   |   |   |   |   |   |   |   |   |

| 6       |   |   |   |   |   |   |   |   |   |   |   |

| 7       |   |   |   |   |   |   |   |   |   |   |   |

| 8       |   |   |   |   |   |   |   |   |   |   |   |

| 9       |   |   |   |   |   |   |   |   |   |   |   |

#### 2. Formulation

| Decimal | A | В | C | D | a | b | C | d | е | f | g |

|---------|---|---|---|---|---|---|---|---|---|---|---|

| 0       | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 |   |

| 1       | 0 | 0 | 0 | 1 |   | 1 | 1 |   |   |   |   |

| 2       | 0 | 0 | 1 | 0 | 1 | 1 |   | 1 | 1 |   | 1 |

| 3       |   |   |   |   |   |   |   |   |   |   |   |

| 4       |   |   |   |   |   |   |   |   |   |   |   |

| 5       |   |   |   |   |   |   |   |   |   |   |   |

| 6       |   |   |   |   |   |   |   |   |   |   |   |

| 7       |   |   |   |   |   |   |   |   |   |   |   |

| 8       |   |   |   |   |   |   |   |   |   |   |   |

| 9       |   |   |   |   |   |   |   |   |   |   |   |

#### 2. Formulation

| Decimal | A | В | C | D | a | b | C | d | е | f | g |

|---------|---|---|---|---|---|---|---|---|---|---|---|

| 0       | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 |   |

| 1       | 0 | 0 | 0 | 1 |   | 1 | 1 |   |   |   |   |

| 2       | 0 | 0 | 1 | 0 | 1 | 1 |   | 1 | 1 |   | 1 |

| 3       | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 |   |   | 1 |

| 4       |   |   |   |   |   |   |   |   |   |   |   |

| 5       |   |   |   |   |   |   |   |   |   |   |   |

| 6       |   |   |   |   |   |   |   |   |   |   |   |

| 7       |   |   |   |   |   |   |   |   |   |   |   |

| 8       |   |   |   |   |   |   |   |   |   |   |   |

| 9       |   |   |   |   |   |   |   |   |   |   |   |

Salue Salue

#### 2. Formulation

| Decimal | A | В | C | D | a | b | C | d | е | f | g |

|---------|---|---|---|---|---|---|---|---|---|---|---|

| 0       | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 |   |

| 1       | 0 | 0 | 0 | 1 |   | 1 | 1 |   |   |   |   |

| 2       | 0 | 0 | 1 | 0 | 1 | 1 |   | 1 | 1 |   | 1 |

| 3       | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 |   |   | 1 |

| 4       | 0 | 1 | 0 | 0 |   | 1 | 1 |   |   | 1 | 1 |

| 5       |   |   |   |   |   |   |   |   |   |   |   |

| 6       |   |   |   |   |   |   |   |   |   |   |   |

| 7       |   |   |   |   |   |   |   |   |   |   |   |

| 8       |   |   |   |   |   |   |   |   |   |   |   |

| 9       |   |   |   |   |   |   |   |   |   |   |   |

Silve

#### 2. Formulation

| Decimal | A | В | C | D | a | b | C | d | е | f | g |

|---------|---|---|---|---|---|---|---|---|---|---|---|

| 0       | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 |   |

| 1       | 0 | 0 | 0 | 1 |   | 1 | 1 |   |   |   |   |

| 2       | 0 | 0 | 1 | 0 | 1 | 1 |   | 1 | 1 |   | 1 |

| 3       | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 |   |   | 1 |

| 4       | 0 | 1 | 0 | 0 |   | 1 | 1 |   |   | 1 | 1 |

| 5       | 0 | 1 | 0 | 1 | 1 |   | 1 | 1 |   | 1 | 1 |

| 6       |   |   |   |   |   |   |   |   |   |   |   |

| 7       |   |   |   |   |   |   |   |   |   |   |   |

| 8       |   |   |   |   |   |   |   |   |   |   |   |

| 9       |   |   |   |   |   |   |   |   |   |   |   |

SUUG !

#### 2. Formulation

| Decimal | A | В | C | D | a | b | C | d | е | f | g |

|---------|---|---|---|---|---|---|---|---|---|---|---|

| 0       | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 |   |

| 1       | 0 | 0 | 0 | 1 |   | 1 | 1 |   |   |   |   |

| 2       | 0 | 0 | 1 | 0 | 1 | 1 |   | 1 | 1 |   | 1 |

| 3       | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 |   |   | 1 |

| 4       | 0 | 1 | 0 | 0 |   | 1 | 1 |   |   | 1 | 1 |

| 5       | 0 | 1 | 0 | 1 | 1 |   | 1 | 1 |   | 1 | 1 |

| 6       | 0 | 1 | 1 | 0 | 1 |   | 1 | 1 | 1 | 1 | 1 |

| 7       |   |   |   |   |   |   |   |   |   |   |   |

| 8       |   |   |   |   |   |   |   |   |   |   |   |

| 9       |   |   |   |   |   |   |   |   |   |   |   |

Silvio,

#### 2. Formulation

| Decimal | A | В | C | D | a | b | C | d | е | f | g |

|---------|---|---|---|---|---|---|---|---|---|---|---|

| 0       | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 |   |

| 1       | 0 | 0 | 0 | 1 |   | 1 | 1 |   |   |   |   |

| 2       | 0 | 0 | 1 | 0 | 1 | 1 |   | 1 | 1 |   | 1 |

| 3       | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 |   |   | 1 |

| 4       | 0 | 1 | 0 | 0 |   | 1 | 1 |   |   | 1 | 1 |

| 5       | 0 | 1 | 0 | 1 | 1 |   | 1 | 1 |   | 1 | 1 |

| 6       | 0 | 1 | 1 | 0 | 1 |   | 1 | 1 | 1 | 1 | 1 |

| 7       | 0 | 1 | 1 | 1 | 1 | 1 | 1 |   |   |   |   |

| 8       |   |   |   |   |   |   |   |   |   |   |   |

| 9       |   |   |   |   |   |   |   |   |   |   |   |

Silvino,

#### 2. Formulation

| Decimal | A | В | C | D | a | b | C | d | е | f | g |

|---------|---|---|---|---|---|---|---|---|---|---|---|

| 0       | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 |   |

| 1       | 0 | 0 | 0 | 1 |   | 1 | 1 |   |   |   |   |

| 2       | 0 | 0 | 1 | 0 | 1 | 1 |   | 1 | 1 |   | 1 |

| 3       | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 |   |   | 1 |

| 4       | 0 | 1 | 0 | 0 |   | 1 | 1 |   |   | 1 | 1 |

| 5       | 0 | 1 | 0 | 1 | 1 |   | 1 | 1 |   | 1 | 1 |

| 6       | 0 | 1 | 1 | 0 | 1 |   | 1 | 1 | 1 | 1 | 1 |

| 7       | 0 | 1 | 1 | 1 | 1 | 1 | 1 |   |   |   |   |

| 8       | 1 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

| 9       |   |   |   |   |   |   |   |   |   |   |   |

#### 2. Formulation

| Decimal | A | В | C | D | a | b | C | d | е | f | g |

|---------|---|---|---|---|---|---|---|---|---|---|---|

| 0       | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 |   |

| 1       | 0 | 0 | 0 | 1 |   | 1 | 1 |   |   |   |   |

| 2       | 0 | 0 | 1 | 0 | 1 | 1 |   | 1 | 1 |   | 1 |

| 3       | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 |   |   | 1 |

| 4       | 0 | 1 | 0 | 0 |   | 1 | 1 |   |   | 1 | 1 |

| 5       | 0 | 1 | 0 | 1 | 1 |   | 1 | 1 |   | 1 | 1 |

| 6       | 0 | 1 | 1 | 0 | 1 |   | 1 | 1 | 1 | 1 | 1 |

| 7       | 0 | 1 | 1 | 1 | 1 | 1 | 1 |   |   |   |   |

| 8       | 1 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

| 9       | 1 | 0 | 0 | 1 | 1 | 1 | 1 | 1 |   | 1 | 1 |

# 3. Optimisation

Convert to Boolean expression

| Decimal | A | В | C | D | a | b | C | d | е | f | g |

|---------|---|---|---|---|---|---|---|---|---|---|---|

| 0       | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 0 |

| 1       | 0 | 0 | 0 | 1 | 0 | 1 | 1 | 0 | 0 | 0 | 0 |

| 2       | 0 | 0 | 1 | 0 | 1 | 1 | 0 | 1 | 1 | 0 | 1 |

| 3       | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 0 | 1 |

| 4       | 0 | 1 | 0 | 0 | 0 | 1 | 1 | 0 | 0 | 1 | 1 |

| 5       | 0 | 1 | 0 | 1 | 1 | 0 | 1 | 1 | 0 | 1 | 1 |

| 6       | 0 | 1 | 1 | 0 | 1 | 0 | 1 | 1 | 1 | 1 | 1 |

| 7       | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 0 | 0 | 0 |

| 8       | 1 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

| 9       | 1 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 0 | 1 | 1 |

Convert to Boolean expression

$$a = \overline{A}C + \overline{A}BD + \overline{B}\overline{C}\overline{D} + A\overline{B}\overline{C}$$

$$b = \overline{A}\overline{B} + \overline{A}\overline{C}\overline{D} + \overline{A}CD + A\overline{B}\overline{C}$$

$$c = \overline{A}B + \overline{A}D + \overline{B}\overline{C}\overline{D} + A\overline{B}\overline{C}$$

$$d = \overline{A}C\overline{D} + \overline{A}\overline{B}C + \overline{B}\overline{C}\overline{D} + A\overline{B}\overline{C} + \overline{A}B\overline{C}D$$

$$e = \overline{A}C\overline{D} + \overline{B}\overline{C}\overline{D}$$

$$f = \overline{A}B\overline{C} + \overline{A}\overline{C}\overline{D} + \overline{A}B\overline{D} + A\overline{B}\overline{C}$$

$$g = \overline{A}C\overline{D} + \overline{A}BC + \overline{A}B\overline{C} + A\overline{B}\overline{C}$$

- Convert to Boolean expression

- Indie: 27 AND7 OR gates

$$a = \overline{A}C + \overline{A}BD + \overline{B}\overline{C}\overline{D} + \overline{A}\overline{B}\overline{C}$$

$$b = \overline{A}\overline{B} + \overline{A}\overline{C}\overline{D} + \overline{A}CD + \overline{A}\overline{B}\overline{C}$$

$$c = \overline{A}B + \overline{A}D + \overline{B}\overline{C}\overline{D} + \overline{A}\overline{B}\overline{C}$$

$$d = \overline{A}C\overline{D} + \overline{A}\overline{B}C + \overline{B}\overline{C}\overline{D} + \overline{A}\overline{B}\overline{C} + \overline{A}B\overline{C}D$$

$$e = \overline{A}C\overline{D} + \overline{B}\overline{C}\overline{D}$$

$$f = \overline{A}B\overline{C} + \overline{A}\overline{C}\overline{D} + \overline{A}B\overline{D} + \overline{A}\overline{B}\overline{C}$$

$$g = \overline{A}C\overline{D} + \overline{A}\overline{B}C + \overline{A}B\overline{C} + \overline{A}B\overline{C}$$

#### 5. Verification (Skipped here)

- Convert to Boolean expression

- Indie: 27 AND 7 OR gates

$$a = \overline{A}C + \overline{A}BD + \overline{B}\overline{C}\overline{D} + \overline{A}\overline{B}\overline{C}$$

$$b = \overline{A}\overline{B} + \overline{A}\overline{C}\overline{D} + \overline{A}CD + \overline{A}\overline{B}\overline{C}$$

$$c = \overline{A}B + \overline{A}D + \overline{B}\overline{C}\overline{D} + \overline{A}\overline{B}\overline{C}$$

$$d = \overline{A}C\overline{D} + \overline{A}\overline{B}C + \overline{B}\overline{C}\overline{D} + \overline{A}\overline{B}\overline{C} + \overline{A}B\overline{C}D$$

$$e = \overline{A}C\overline{D} + \overline{B}\overline{C}\overline{D}$$

$$f = \overline{A}B\overline{C} + \overline{A}\overline{C}\overline{D} + \overline{A}B\overline{D} + \overline{A}B\overline{C}$$

$$g = \overline{A}C\overline{D} + \overline{A}\overline{B}C + \overline{A}B\overline{C} + \overline{A}B\overline{C}$$

# BCD to 7 Segment Display

- 'BCD-to-seven-segment decoder'

- 'decodes' binary code for decimal digit

- usually decoders mean something different, which we'll discuss later

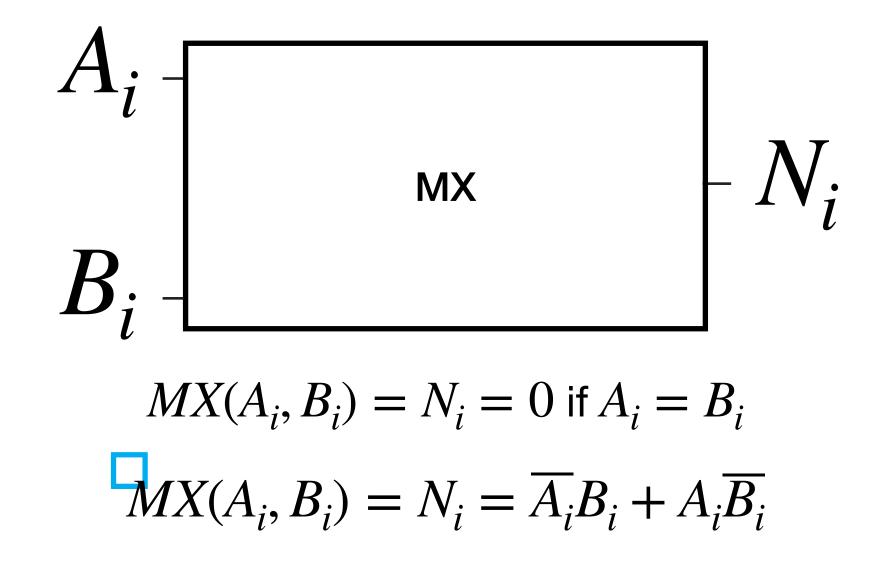

# 4-bit Equity Comparator

Ah, not again

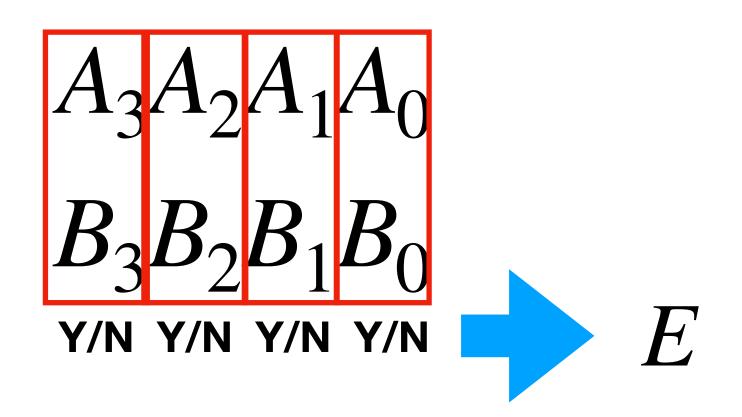

# 4-bit Equity Comparator

- Compare two numbers

- Equal or not

#### 1. Specification

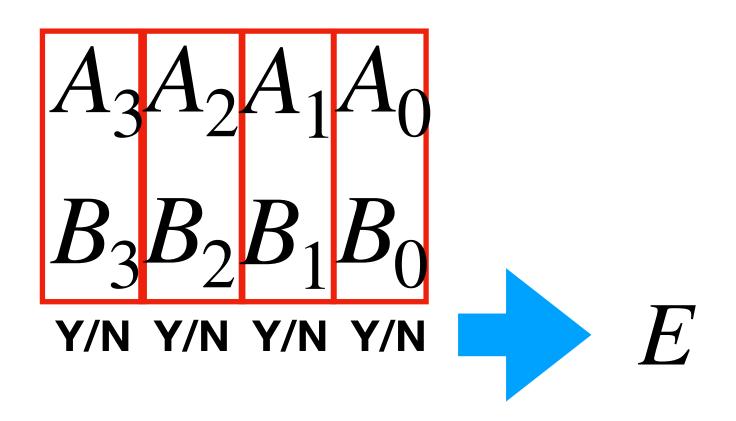

- Input:  $A_3A_2A_1A_0$ ,  $B_3B_2B_1B_0$

- Output: E = 1 for equal, 0 for not

#### 2. Formulation

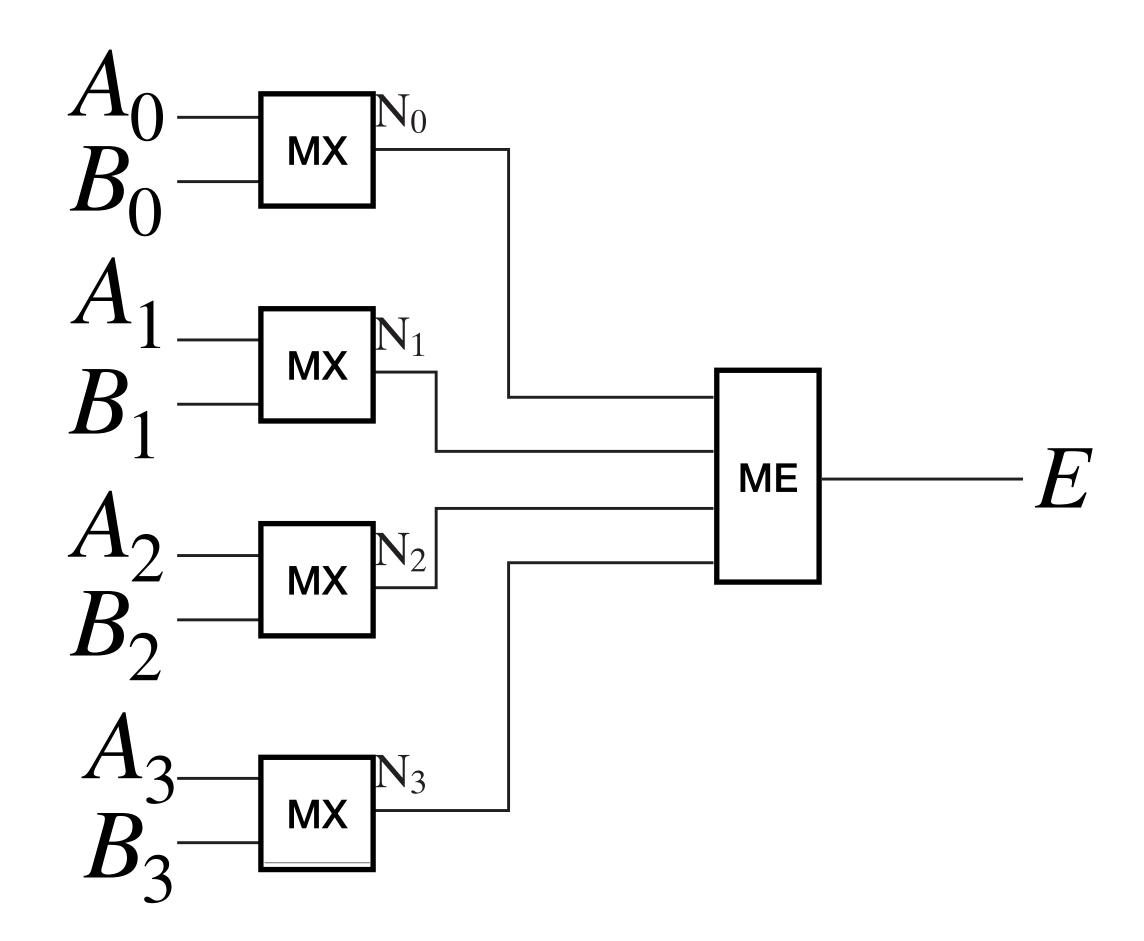

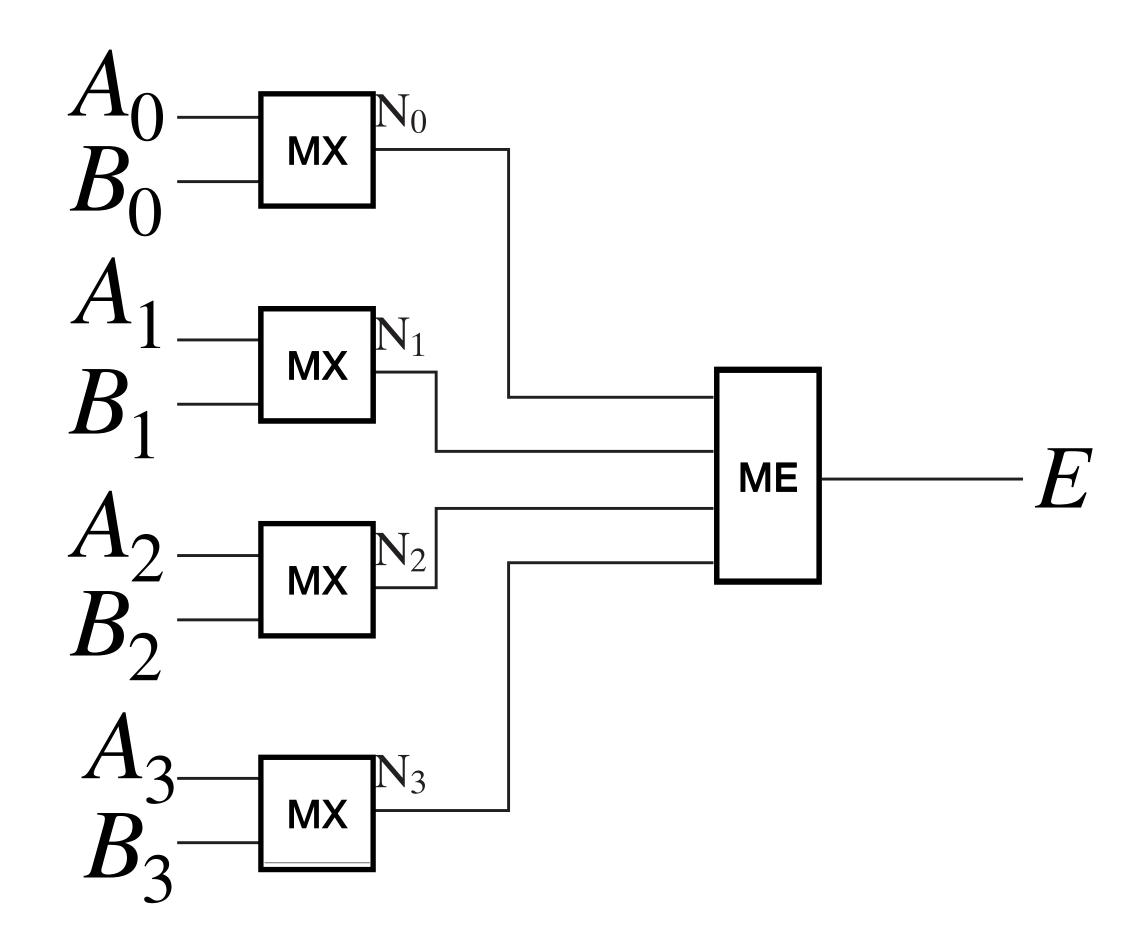

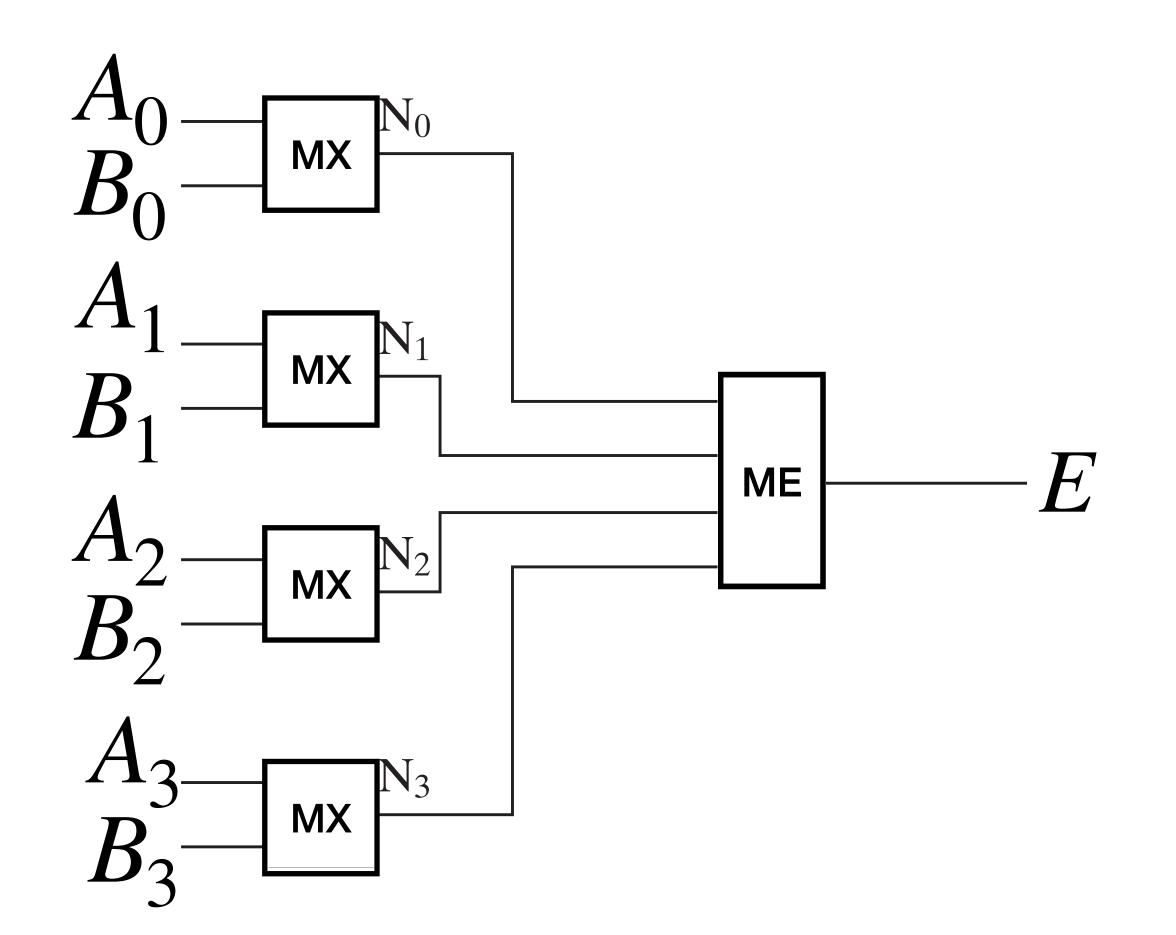

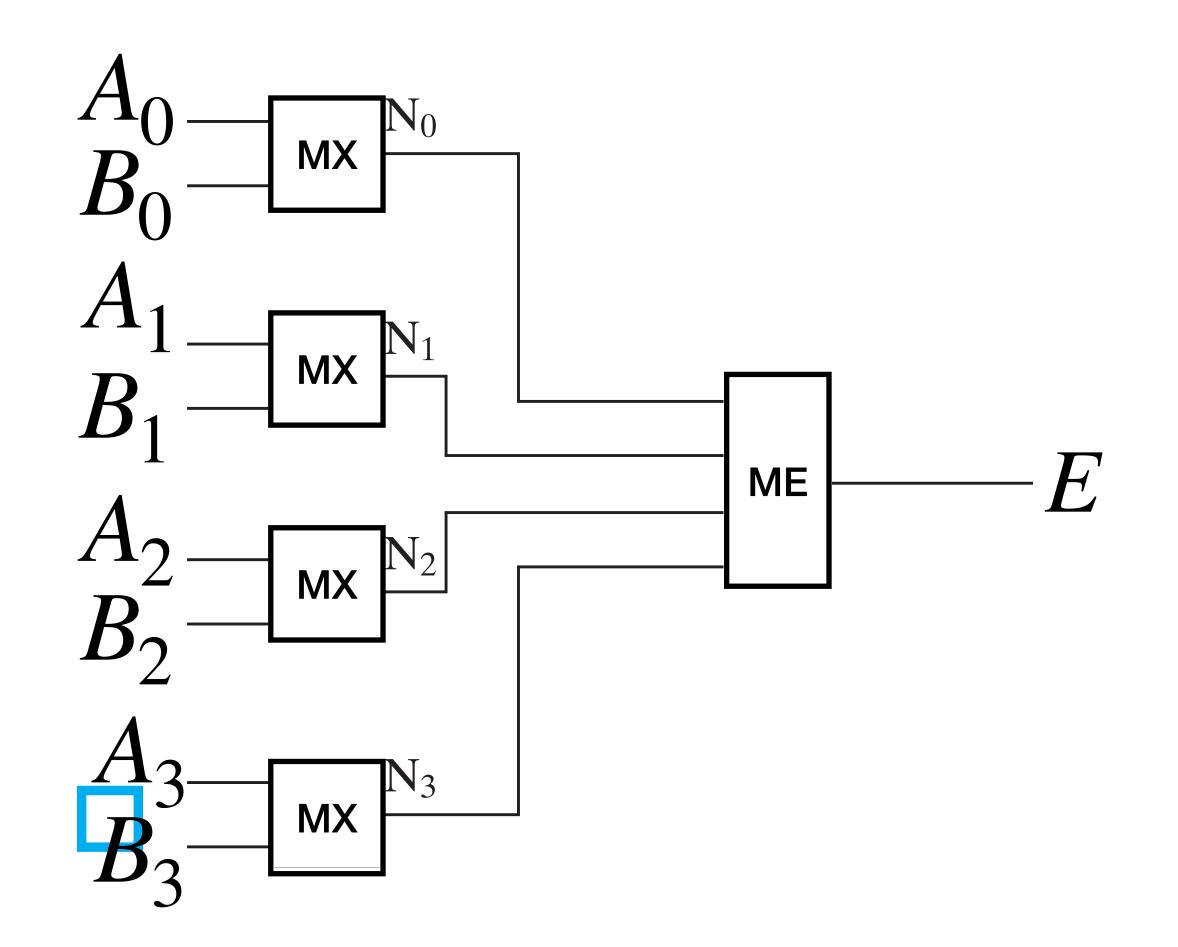

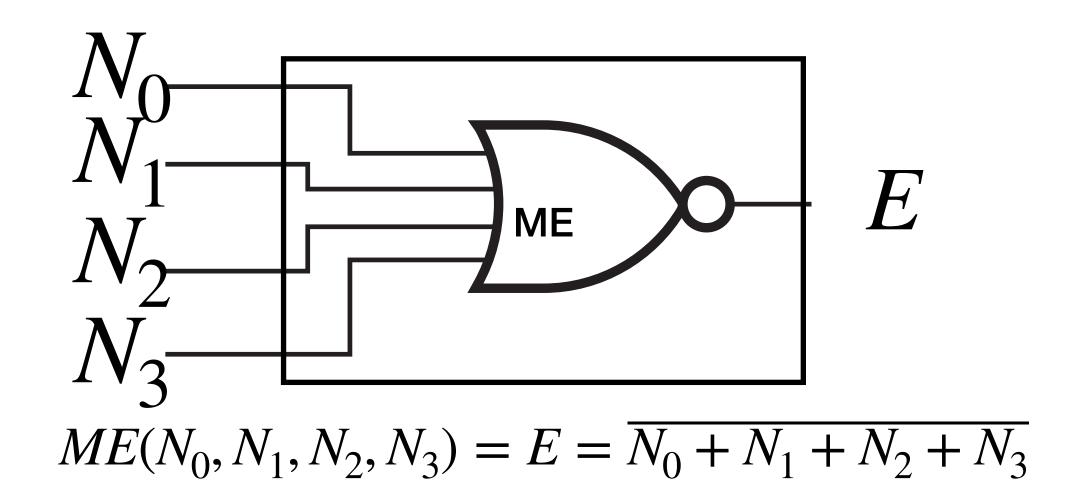

- 2 things are happening

- We need to compare pairs of binary values and see if they are equal

- ullet We need to combine the comparison of all these different bits to make up E

#### Hierarchical Design

- "divide-and-conquer"

- Circuit is broken up into individual functional pieces (blocks)

- Each block has explicitly defined Interface (I/O) and Behaviour

- A single block can be reused multiple times to simplify design process

- If a single block is too complex, it can be further divided into smaller blocks, to allow for easier designs

Cook

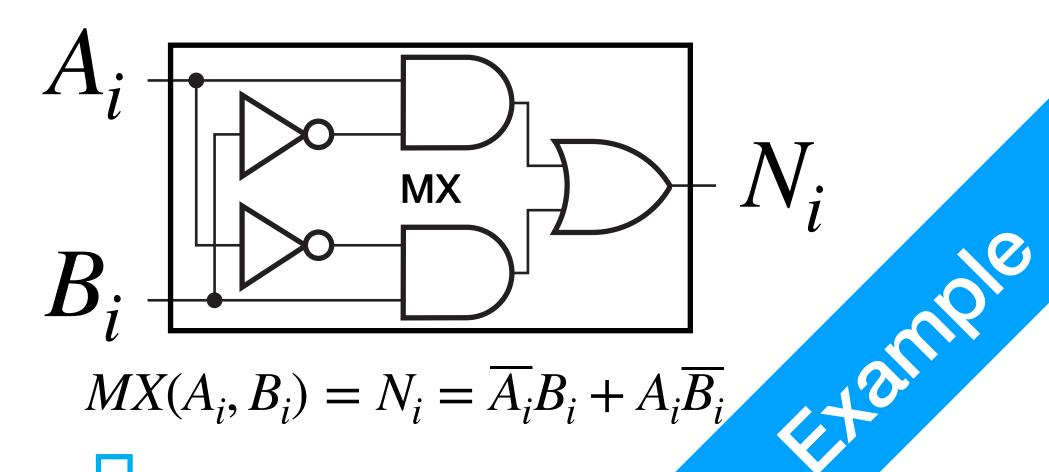

- 2 things are happening

- We need to compare pairs of binary values and see if they are equal м

MX

ullet We need to combine the comparison of all these different bits to make up E

ME

Mostly Old Tech, no new iPhones

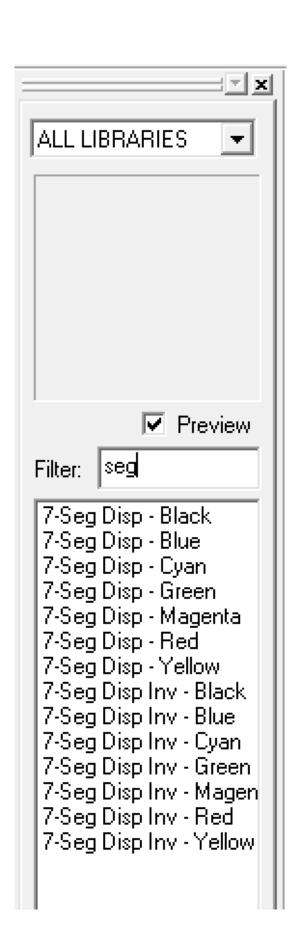

- Technology

- Available physical components

- Programmable implementation technology e.g. Field-Programmable Gate Array (FPGA)

- VHDL; Verilog Language

Course

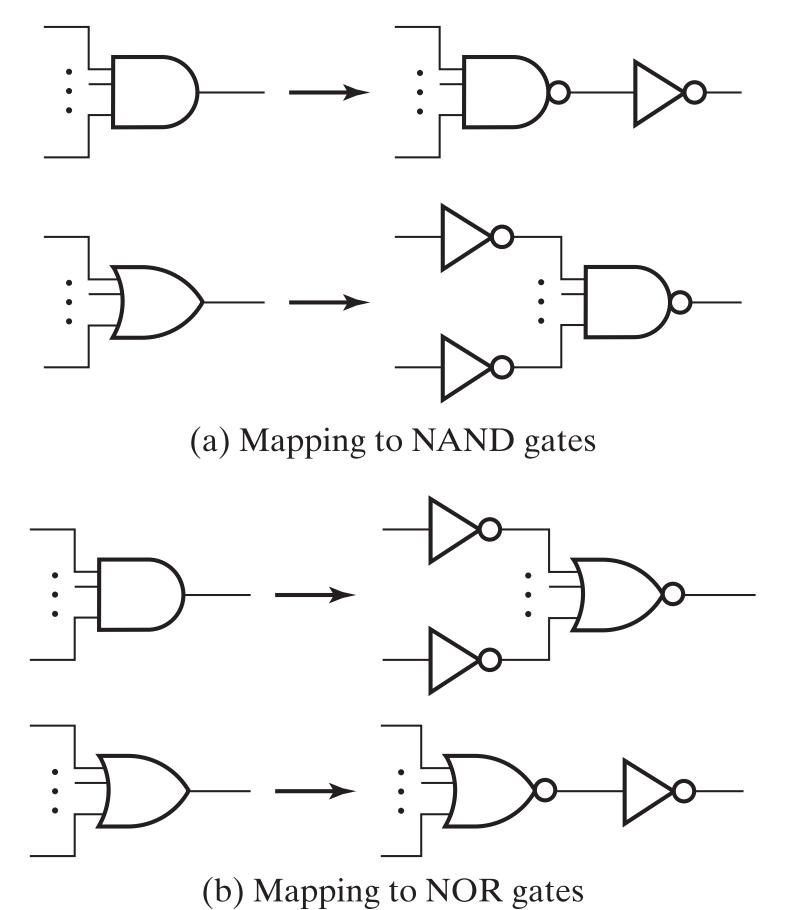

- NAND == AND + Inverter;

- AND == NAND + Inverter;

- NOR == OR + Inverter;

- OR == NOR + Inverter;

- DeMorgen's Rule

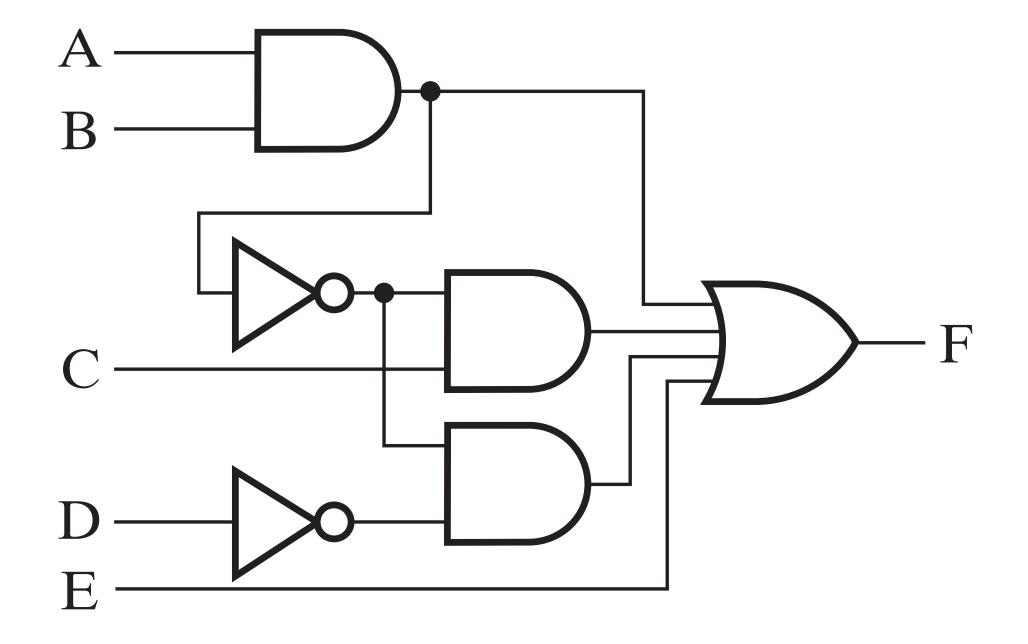

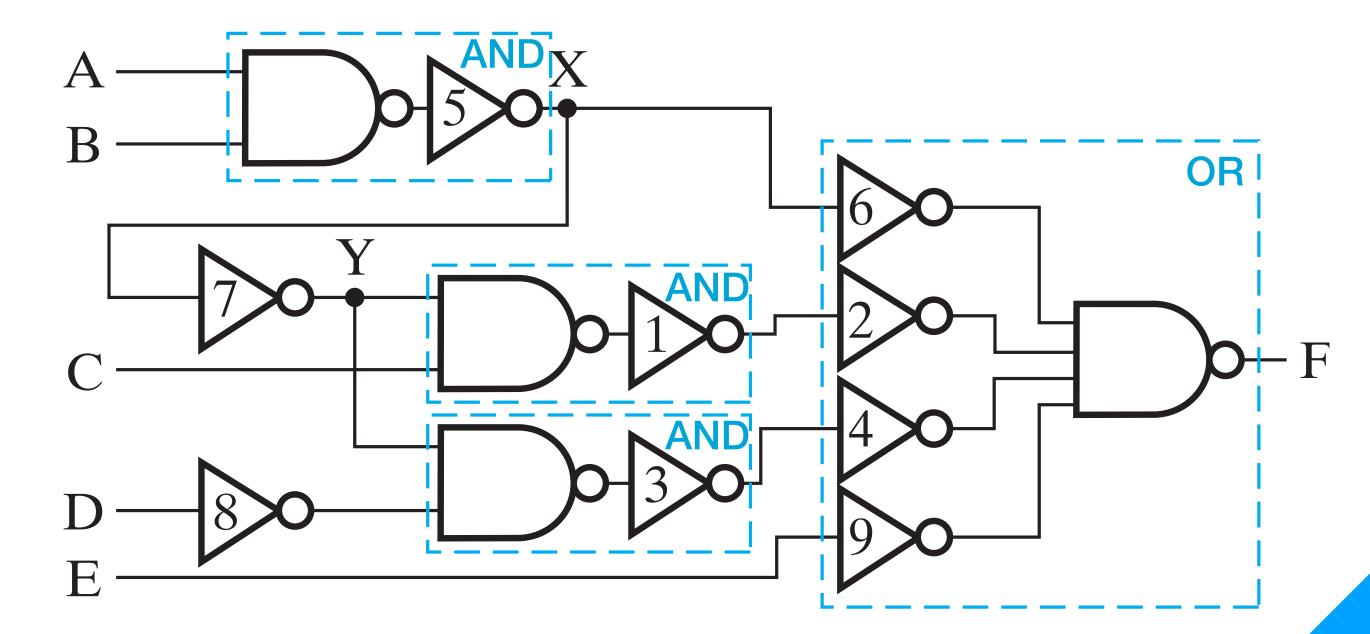

Implement the circuit diagram with NAND gates and Inverters only

- Implement the circuit diagram with NAND gates and Inverters only

- 1. Replacement

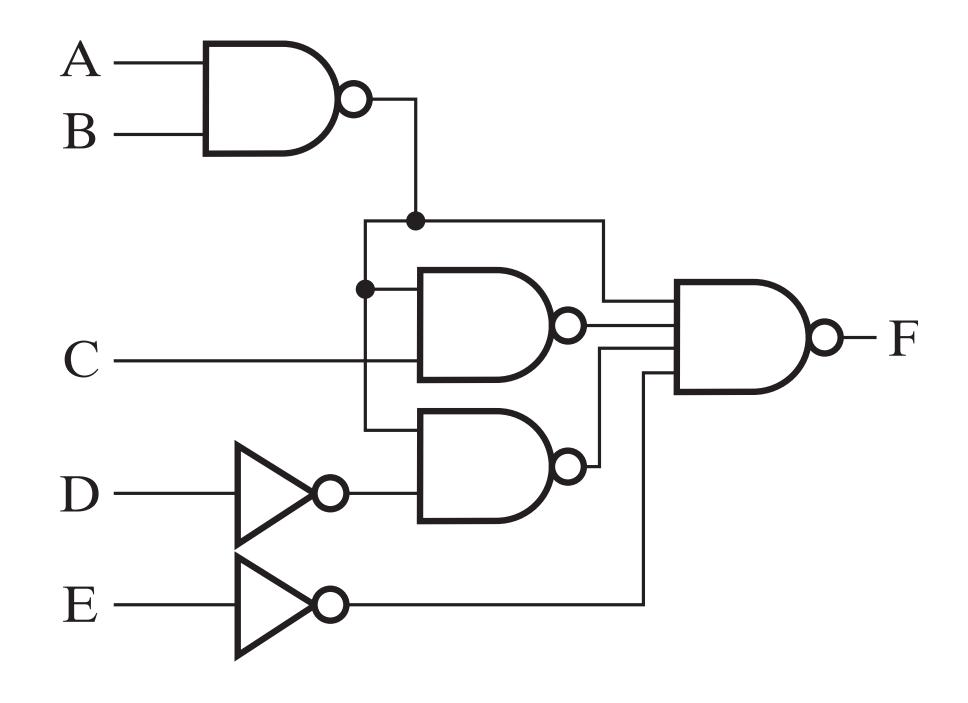

- Implement the circuit diagram with NAND gates and Inverters only

- 1. Replacement

- 2. Simplification

#### Verification

Manual vs Auto

#### Verification

- Manual

- Use the truth table, row by row

- Auto

- Use computer simulation to go through the truth table

Court